24通道数据采集模块设计及FPGA实现技术分析

模拟技术

描述

在声纳系统中,需要对从外界输入的声信号数字化后才能进行处理和分析。其中数据采集模块负责模拟信号的采集及传输,它在系统中起着至关重要的作用,而数字化的精度对后期数据处理的精度有着重要影响。本文采用24位∑-△A/D数据转换器构建24通道高精度数据采集模块,满足声纳系统对数据采集模块的精度要求及采集通道的数量要求。

1 数据采集模块的硬件结构

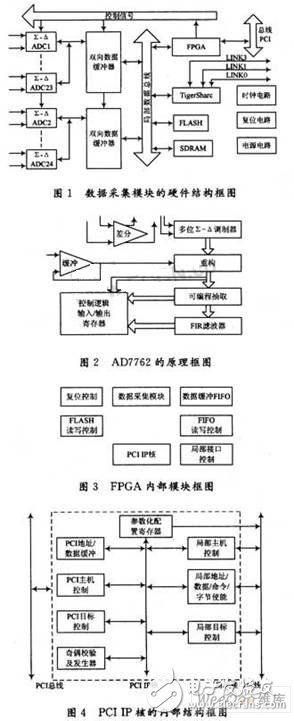

1.1 数据采集模块的结构框图

图1给出本文中数据采集模块的硬件结构框图,它由24路∑-△A/D数据转换器、双向数据缓冲器、FPGA,TigerSharc DSP,FLASH,SDRAM、时钟电路、复位电路及电源电路组成,其中∑-△A/D数据转换器负责对模拟信号的采集转换,FPGA负责整个模块的数据采集控制及数据缓冲,TigerSharc DSP负责整个模块的协调及转换后数据的预处理。下面对∑-△A/D数据转换器及FPGA进行介绍。

1.2 AD7762简介

本文采用的∑-△A/D数据转换器是Analog公司的24位高精度数据转换器AD7762,图2是它的原理框图。它具有如下特性:全差分调制器输入、用于信号缓冲的片上差分放大器、可编程超采样率、带缺省或用户可编程系数的低通FIR滤波器及用于多器件之间的同步输入引脚。在实际电路的PCB设计中,由于AD7762是对噪声敏感的模拟器件,所以在具体PCB设计时需要做到以下几个方面:A/D模拟电源单独供电、模拟地与数字地单点接地、差分输入线等长且阻抗等于100 Ω、采用精确的参考电压源。

1.3 采集控制逻辑原理及其FPGA实现

FPGA主要实现整个模块的数据采集控制、数据缓冲及PCI总线控制器等功能。本文中FPGA采用Altera公司的CycloneⅡ系列EP2C20芯片,其中PCI总线控制器采用PCI IP核进行设计,简化PCI控制器的开发难度。图3是FPGA内部模块的组成框图。下面对其中PCI IP核及其局部接口控制、数据采集模块及数据缓冲FIFO的设计做介绍。

1.3.1 PCI IP核及其局部接口控制

本文采用Altera公司的PCI IP核进行PCI总线协议的硬件实现,图4是PCI IP核的内部结构框图。在具体设计中,使用MegaWizard例化PCI IP核,同时需要相应的局部接口控制逻辑实现DSP与PCI IP核的连接。

1.3.2 数据采集模块

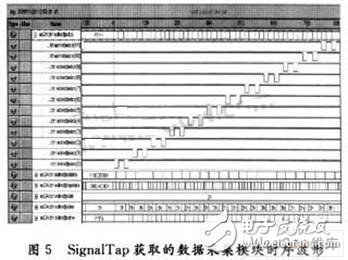

数据采集模块完成A/D初始化控制及A/D数据读控制,其中A/D初始化控制完成对A/D内部控制寄存器的写操作,而A/D数据读控制完成对A/D数据的正常读取。具体控制逻辑根据AD7762的时序图设计,图5是用QuartusⅡ中的SignalTap获取的数据采集模块的时序波形。

1.3.3 数据缓冲FIFO

为了解决前端数据采集与后端数据传输在速率上的不匹配问题,在FPGA内部设置一块数据缓冲FIFO,大小为4 k×32 b,A/D转换后的数据直接存储到FIFO中,而DSP对FIFO中数据的读取通过中断方式完成。数据缓冲FIFO通过MegaWizard例化,只需要少量的读写控制逻辑就可以使FIFO正常工作,而且FIFO的大小可以在FPGA提供的RAM位数范围内灵活设置。

2 数据采集模块的程序设计

在模块上电后FPGA从EPROM中加载配置数据,完成初始化后切换到用户状态,TigerSharc DSP通过主机进行程序加载,程序随之开始运行,在A/D完成初始化及同步后,自动将采集到的数据写入FPGA内部FIFO,DSP等待FIFO半满中断信号的产生,当DSP检测到中断发生后,进入相应的中断服务程序,将FIFO的数据读入到DSP的片上存储器,DSP通过LINK口将数据传送到后续的信号处理模块,另外也可以将数据直接存储到数据采集模块上的SDRAM上,由DSP进行一些预处理后再将数据传送到后续的信号处理模块。

3 结 语

本文设计的24通道数据采集模块采用FPGA实现数据采集控制、数据缓冲及PCI总线控制器等功能,简化了电路,提高模块的可靠性和稳定性,并有利于模块的功能升级;同时采用∑-△A/D数据转换器,满足了声纳系统对数据采集精度方面的要求;另外Tiger-Sharc DSP为数据的预处理也提供了相应的处理能力。因此本文中的数据采集模块具有较好的工程价值和广泛的应用前景。

-

8通道数据采集2012-08-20 2635

-

8通道同步数据采集卡QT11382016-07-27 4560

-

8通道同步数据采集卡 QT11382016-08-05 3401

-

基于FPGA与SRAM数据采集系统设计2018-05-09 3049

-

基于FPGA+AD7609的数据采集系统实现2018-08-09 7543

-

16通道,24位ΔΣADC,为数据采集提供小巧灵活和精确的解决方案2019-07-12 2799

-

如何去实现基于32单片机的16通道ADC数据采集呢2022-01-05 1611

-

MIMXRT1601如何能实现8通道的pdm麦克风数据采集?2022-01-12 1251

-

多通道超声探伤数据采集处理技术2010-08-05 695

-

基于FPGA的多通道同步数据采集存储系统2010-12-27 1140

-

8通道并行数据采集PCI模块的设计2009-02-08 1277

-

基于FPGA的多通道数据采集系统设计2016-05-10 941

-

六通道高速数据采集系统的设计2017-01-17 757

-

如何使用FPGA进行多通道同步数据采集系统的设计2018-12-18 1542

-

FPGA的多通道数据采集传输系统2024-12-09 1260

全部0条评论

快来发表一下你的评论吧 !