FPGA开发进行实例化,如何获得访问权限

电子说

描述

部分可重配置会涉及到将配置数据下载到正在运行的系统中。 尽管在芯片和比特流中内置了一些保护措施,比如器件ID,从而确保识别正确的部分,但是作为用户设计的一部分,仍有一些技术需要理解和实现。 设计人员应遵循这些建议,以确保部分可重配置的安全和可预测性。

• 在进行重新配置操作之前需要对可重配置分区(RP)内的一些活动程序进行关闭,如果可重配置功能没有进行完整的传输或者没有对最近的请求作出回复,那么整个系统可能会挂起。

解决方案:在你的设计中务必确保在重新配置之前RP分区内所有活动都已经完成,在设计中对每个分区内都实现请求—通知握手操作,这样系统就不会挂起,信息也不会丢失。

• 对RP分区进行隔离,这样任何动态的变化都不会对静态设计产生任何负面的影响,目前还无法预测RP分区在进行动态配置时会有哪些行为方式,如果一些浮动信号从RP分区“逃出去”,那么一些虚假事件就会对静态设计产生负面影响。

解决方案:最佳的操作方案就是断开该分区与静态设计之间的连接直到可重配置操作完成,PR Controller IP通过选通任何接口端口可以用于隔离RP分区,或者自定义逻辑模块(2选1多路复用器,具有复位或启动门控的寄存器等)都可以实现这个功能。

• 如果部分比特流文件必须传递给远程系统,那么在传送过程中可能会造成损坏,如果将损坏的部分比特流发送到配置引擎中,那么静态设计部分可能会受影响,在比特流末尾进行标准的CRC检查并不够完整,因为所有的配置数据在检查操作之前已经发送完毕。

解决方案:部分比特流文件的每一帧数据都可以使用CRC进行检测,因此坏帧在可以加载到配置存储器之前都可以被检测到,然后我们可以采取纠正或者回退操作。在每个路由设计检查点都启用CRC检查,开启命令如下:set_property bitstream.general.perFrameCRC yes [current_design]

然而最关键的细节就是绝对确保传送给FPGA或者SoC的部分比特流能够与静态设计相互兼容,这样才能够配置到器件中,部分可重配置设计流程需要对静态实现部分进行锁定,并且所有可重配置模块都要在此上下文中实现,如果静态设计改变了,那么所有使用该静态设计创建的部分比特流都将失效并且需要重新编译,因为部分比特流内容的很多方面都已经发生了变化——时钟、分区管脚、静态路由等都可能是不同的了,这种保守的方法具有一定的灵活性,提升整体设计的性能,但是必须要个遵循主从的关系。

设计者必须实现某种版本检查方案来确保只有匹配的比特流才能够被加载到静态设计系统中,实现方式有很多种,片上/片下、硬件/软件等。不管哪种方式都将会在部分比特流文件发送至配置端口前根据静态设计部分的版本来检查比特流文件的版本。

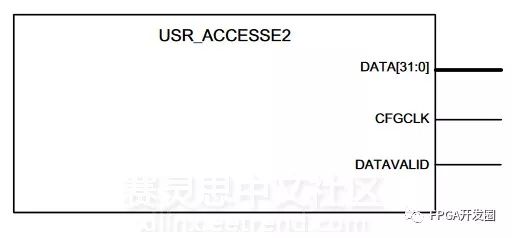

在FPGA结构中执行这种检查的一个便利的方式就是使用USR_ACCESS模块,该组件在专用配置空间中保存一个32位的寄存器,但是可以通过FPGA访问,只需要将USR_ACCESSE2模块在你的RTL设计中进行实例化就可以获得访问权限,通过连接32位数据总线即可使用此功能。

这个常量寄存器的值是通过下面命令来设置的:set_property BITSTREAM.CONFIG.USR_ACCESS 0x<8-digit-hex>|TIMESTAMP [current_design]

尽管我们可以使用TIMESTAMP选项,通过加载所有比特位文件信息可能更容易创建自定义的寄存器值,TIMESTAMP的值是即时计算的,所以在应用到部分比特文件时需要读取Vivado工具为静态设计部分计算的数值。

一旦设计连接了此元素,你可以使用32位的值来匹配部分比特流文件,这个值保存在上文给定属性的完整比特流文件中,因为它是在器件初始化配置时编写的,然而部分比特流文件并不包含此值,因为它不会去重新编程USR_ACCESS寄存器,你需要对每个部分比特流添加自定义数据头信息,这个数据头应该包含这个值用于静态设计部分的版本检查,最简单的比较匹配就是设置错误标志,如果检测到失败这是必需的,一旦检测到不匹配系统需要确定下一步该怎么操作。

当创建新版本的静态设计时你需要更新USR_ACCESS的值,不仅包括静态设计部分还包括根据此静态设计版本相匹配的一系列部分比特流文件,USR_ACCESS模块具有两个特性使其成为该用法的理想选择:

1. 由于它是配置应用方面专用的模块,因此它不使用任何标准的CLB或者BRAM资源,为你的设计留出更多可用的资源。

2. 由于该值是通过属性来设置的,因此可以在所有布局和布线完成后再插入该值,以后再重新插入新值时也不再需要进行重新综合或者实现。

在写入完整的比特流数据前只需要将新的 BITSTREAM.CONFIG.USR_ACCESS 应用于完整设计版本检查,任何较旧版本的部分比特流文件都会在进行版本检查时被拒绝,确保与硬件的匹配。

想了解更多关于USR_ACCESS的信息可以查看XAPP1231文档。

总结在部分可重配置设计中应用版本识别检查和其他安全机制从而可以确保安全可靠的工作环境。

我们希望听到您的意见!参与部分可重配置问卷调查(请点击“阅读原文”在线参与)对这个解决方案提供反馈,帮助我们改进的更好。

作者简介David Dye是分层设计流程的高级产品营销经理,他的职责包括产品规划、部分可重配置的市场营销,串联配置和相关设计流程等,比如模块分析和团队设计。他在Xilinx拥有超过20年的从业经验,并在其任职期间支持各种ISE和Vivado设计工具的开发,从综合、实现到调试。David拥有卡内基梅隆大学的电气工程学位。

-

shenhao0520

2018-04-30

0 回复 举报学习 收起回复

shenhao0520

2018-04-30

0 回复 举报学习 收起回复

- 相关推荐

- 热点推荐

- FPGA芯片

-

鸿蒙原生应用元服务-访问控制(权限)开发等级和类型2024-04-17 261

-

鸿蒙原生应用元服务-访问控制(权限)开发概念和使用基本原则2024-04-18 260

-

鸿蒙原生应用元服务-访问控制(权限)开发工作流程相关2024-04-19 522

-

鸿蒙原生应用元服务-访问控制(权限)开发校验环节2024-04-22 149

-

鸿蒙原生应用元服务-访问控制(权限)开发应用权限列表三2024-04-25 315

-

鸿蒙原生应用元服务开发-位置服务申请权限2024-06-18 345

-

P2P权限委托与访问控制模型2009-03-24 468

-

基于规则引擎的实例级权限控制研究2009-09-03 649

-

Linux改变文件或目录的访问权限命令2009-01-18 1347

-

JAVA教程之访问权限控制2016-04-13 732

-

微软宣布开放其文本语音转换 AI 的访问权限2021-02-04 2294

-

应用太多无从下手,企业如何破解访问权限管理难题?2023-11-16 1265

-

linux文件访问权限怎么设置2023-11-23 2577

-

如何解决C语言中的“访问权限冲突”异常?C语言引发异常原因分析2024-01-12 7566

-

鸿蒙开发Ability Kit程序访问控制:申请使用受限权限2024-07-02 1318

全部0条评论

快来发表一下你的评论吧 !