PCIe物理层的基本概念

电子说

描述

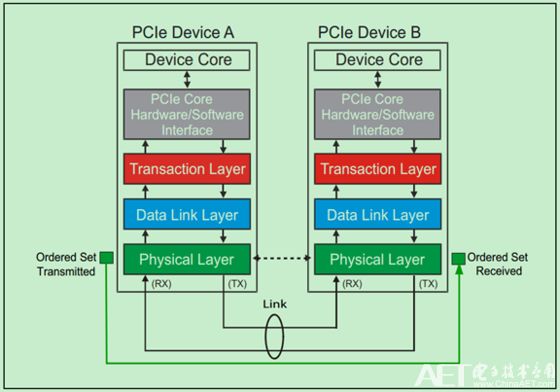

前面的文章简单的介绍了一些关于PCIe总线事务层(Transaction Layer)和数据链路层(Data Link Layer)的一些基本概念。这篇文章来继续聊一聊PCIe总线的最底层——物理层(Physical Layer)。在PCIe Spec中,物理层是被分为两个部分单独介绍的,分别是物理层逻辑子层和物理层电气子层,其中后者一般都是采用SerDes来实现的。本篇文章只是简单地介绍一些PCIe物理层的基本概念,关于物理层详细、深入地介绍,请关注我后续的连载博文。

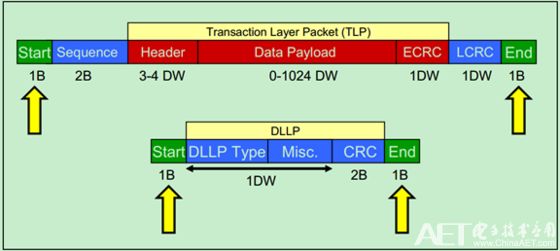

由于物理层处于PCIe体系结构中的最底层,所以无论是TLP还是DLLP都必须通过物理层完成收发操作。来自数据链路层的TLP和DLLP都会被临时放入物理层的Buffer中,并被加上起始字符(Start & End Characters),这些起始字符有的时候也被称为帧字符(Frame Characters)。具体如下图所示:

注:这里所说的TLP和DLLP指的是包的原始发送者发的包,即TLP表示这个包的原始发送者为事务层,而DLLP则为数据链路层。但是TLP仍然会被数据链路层转发,并添加Sequence和LCRC。

物理层完成的一个重要的功能就是8b/10b编码和解码(Gen1 & Gen2),Gen3及之后的PCIe则采用了128b/130b的编码和解码机制。关于8b/10b,这里不再详细地介绍了.

物理层的另一个重要的功能时进行链路(Link)的初始化和训练(Initialization & Training),且是完全自动的操作,并不需要人为的干预。完成链路的初始化和训练之后,便可以确定当前PCIe设备的一些基本属性:

· 链路的宽度(Link Width,x1还是x2,x4……)

· 链路的速率(Link Data Rate)

· Lane Reversal - Lanes connected in reverse order

· Polarity Inversion – Lane polarity connected backward

· Bit Lock Per Lane – Recovering the transmitter clock

· Symbol Lock Per Lane – Finding a recognizable position in the bit-stream

· Lane-to-Lane De-skew Within a Multi-Lane Link

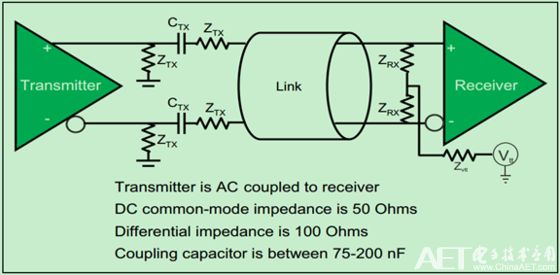

物理层的电气子层主要实现了差分收发对,如下图所示:

由于其速度很高,因此采用的是交流耦合的方式(AC-Coupled),说白了就是在信号线上加了电容Ctx,此时低频信号和直流信号都会被抑制。

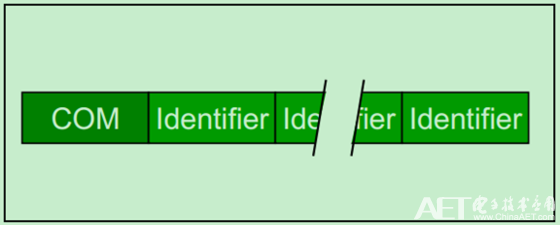

需要注意的是,PCIe物理层处理可以转发LTP和DLLP之外,还可以直接发送命令集(Ordered Sets)。之所以称其为命令集,是因为它并不是真正意义上的包(Packet),因为物理层不会为其添加起始字符(Start & End Characters)。并且命令集始于发送端的物理层,结束语接收端的物理层。虽然命令集没有起始字符,但是对于Gen1&Gen2版本的PCIe物理层来说,会为其添加一个叫做COM的字符作为开始字符,随后跟着三个或者更多的信息字符。

注:PCIe Gen3及之后的版本处理方式有所不同,但是Gen3是向前兼容Gen1 & Gen2的。由于本文主要还是基于Gen2来介绍的,所以关于Gen3的更多信息,大家可以自行参考PCIe Gen3 的Spec。

命令集(Ordered Sets)的收发示意图,如下图所示:

命令集(Ordered Sets)的结构图如下图所示:

命令集主要用于链路的训练操作(Link Training Process)。此外,命令集还用于链路进入或者退出低功耗模式的操作。

-

Flex Bus物理层的CXL帧和数据概述2023-09-11 4995

-

CCIX物理层详解2022-08-15 3544

-

SPI基本概念2021-08-11 1627

-

如何对PCIe 3.0接收机物理层进行测试?2021-05-11 3414

-

什么是以太网物理层?Ethernet物理层有哪些功能?2021-03-18 6230

-

CAN总线不同的物理层2019-05-23 2915

-

PCIe物理层接口定义了物理层中的,媒介层和物理编码子层之间的统一接口2018-09-07 9942

-

PCIe物理层实现了一对收发差分对,可以实现全双工的通信方式2018-05-31 14645

-

物理层的成帧过程2010-02-09 1565

-

物理层 PPT课件2009-11-24 834

-

计算机网络物理层2009-08-05 820

-

WCDMA系统的物理层(FDD)2009-06-14 819

-

物理层2008-10-23 1041

-

物理层的作用2008-07-22 7218

全部0条评论

快来发表一下你的评论吧 !