ADuM7240/ADuM7241 1KV、双通道数字隔离器技术手册

描述

概述

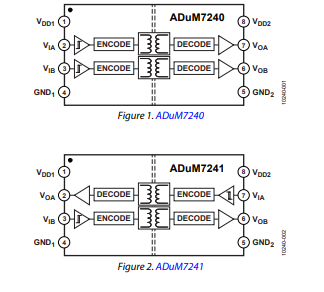

ADuM7240/[ADuM7241]是采用ADI公司的iCoupler ^®^ 技术的双通道数字隔离器。这些隔离器件结合了高速CMOS与单片空芯变压器技术,可提供出色的性能特性,优于光耦器件和其它集成式耦合器。

ADuM724x系列双通道1 kV数字隔离器件采用窄体8引脚SOIC封装。与2.5 kV或5 kV隔离器相比,ADuM724x提供了一种经济选项,适用于仅需基本隔离功能的应用场合。

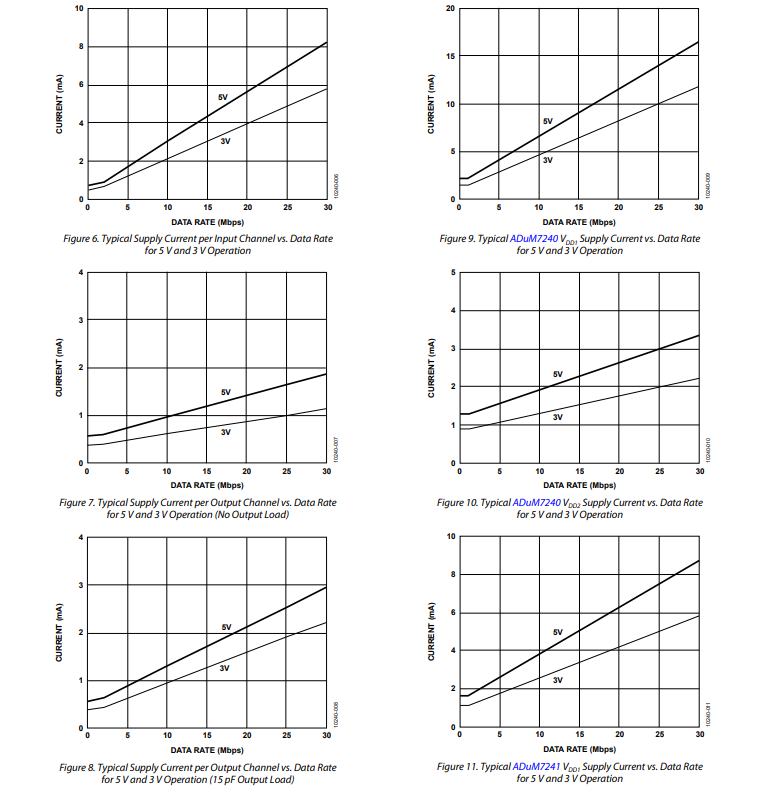

该产品系列像ADI公司的许多隔离器产品一样功耗极低,在高达25 Mbps的数据速率下,其功耗仅为同类隔离器的十分之一至六分之一。除了低功耗,ADuM724x的所有型号都具有很低的脉宽失真(C级小于5 ns)。此外,每款型号均提供输入毛刺滤波器,以防外来噪声干扰。

ADuM724x提供两个独立的隔离通道,支持两种通道配置以及1Mbps和25 Mbps两种数据速率(请参考“订购指南”)。所有型号均可采用3.0 V至5.5 V电源电压工作,与低压系统兼容,并且能够跨越隔离栅实现电压转换功能。另外,在没有输入电源的情况下,所有型号的缺省输出均为逻辑高电平状态。

数据表:*附件:ADuM7240 ADuM7241 1KV、双通道数字隔离器技术手册.pdf

应用

- 通用多通道隔离

- 数据转换器隔离

- 工业现场总线隔离

特性

- 8引脚窄体SOIC封装,符合RoHS标准

- 安全和法规认证

- UL认证(申请中)

UL 1577:1分钟1000 V rms - 低功耗工作

5 V 工作电压:

每个通道2.4 mA(最大值,0 Mbps至1 Mbps)

每个通道11.8 mA(最大值,25 Mbps) - 3.3 V电源:

每个通道1.7 mA(最大值,0 Mbps至1 Mbps)

每个通道8.2 mA(最大值,25 Mbps) - 双向通信

- 数据速率最高可达25 Mbps (NRZ)

- 3 V/5 V电平转换

- 工作温度最高可达:105℃

- 高共模瞬变抗扰度:>15 kV/μs

框图

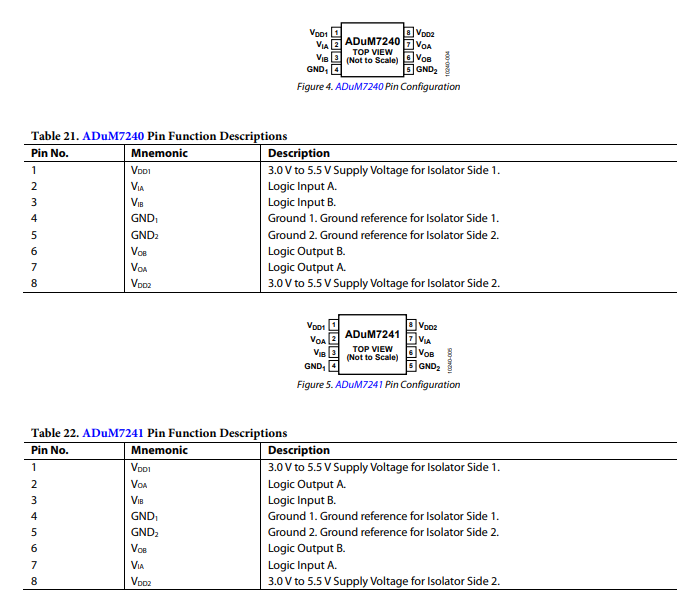

引脚配置描述

典型性能特征

应用信息

印刷电路板布局

ADuM7240/ADuM7241 数字隔离器的逻辑接口无需外部接口电路。强烈建议在输入电源引脚(VDD1)和输出电源引脚(VDD2)处进行电源去耦。去耦电容值应在 0.01μF 至 0.1μF 之间,电容与电源引脚两端的总引线长度不应超过 20mm。

在涉及高共模瞬变的应用中,务必使电路板布局(跨隔离栅)的设计将耦合降至最低。此外,电路板布局应设计为:在给定的器件侧,任何产生的耦合都能均匀影响所有引脚。若不这样做,可能会导致引脚间出现电压差,超过器件的绝对最大额定值,进而致使器件闩锁或永久损坏。

通过合理的印刷电路板设计,ADuM7240/ADuM7241 能够轻松满足 CISPR 22 A 类(及 FCC A 类)发射标准,以及要求更为严格的 CISPR 22 B 类(及 FCC B 类)标准。有关与印刷电路板相关的电磁干扰缓解技术,包括电路板布局和堆叠引脚等内容,请参考 AN - 1109《应用笔记》。

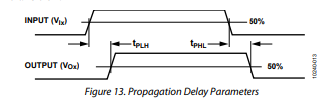

传播延迟相关参数

传播延迟是描述逻辑信号通过器件传播所需时间的参数。高到低转换的输入 - 输出传播延迟时间,可能与低到高转换的传播延迟时间不同。

脉冲宽度失真是这两个传播延迟值之间的最大差值,它体现了输入信号定时的保持精度。

通道间匹配指的是单个 ADuM7240/ADuM7241 器件内各通道之间传播延迟的最大差异量。

传播延迟差异指的是在相同条件下工作的多个 ADuM7240/ADuM7241 器件之间传播延迟的最大差异量。

直流正确性

隔离器输入的正向和负向逻辑转换,会使窄(~1ns)脉冲通过变压器发送至解码器,进而对解码器进行置位或复位,表明有输入逻辑转换。在输入逻辑转换缺失(即输入为逻辑 1 持续超过 1μs)时,会发送一组刷新脉冲,以确保输出的直流正确性,表明正确的输入状态。

若解码器在约 5μs 内未收到脉冲,输入侧内部电路会被视为未通电或无功能,隔离器输出会被看门狗定时器强制置为默认高电平状态。

磁场抗扰度

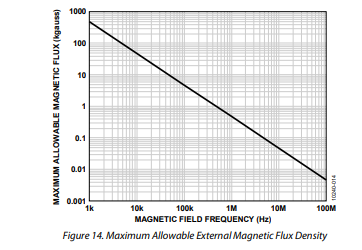

ADuM7240/ADuM7241 的磁场抗扰度由变化的磁场决定,该磁场会在变压器接收线圈中感应出电压,感应电压大到足以错误地置位或复位解码器。以下分析明确了可能出现这种情况的条件。对 ADuM7240/ADuM7241 的 3V 工作条件进行研究,因为这代表了该产品最敏感的工作模式。

变压器输出的脉冲幅度大于 1.0V。解码器的感应阈值约为 0.5V,因此确定了一个 0.5V 的裕量,在此裕量内感应电压可被容忍。接收线圈上感应的电压由下式给出:

其中:

- β 为磁通密度(高斯)。

- r_{n} 为接收线圈中第 n 匝的半径(厘米)。

- N 为接收线圈的匝数。

考虑到 ADuM7240/ADuM7241 中接收线圈的几何形状,以及解码器处感应电压最大为 0.5V(有 0.5V 的裕量)的要求,可计算出给定频率下的最大允许磁场。计算结果如图 14 所示 。

-

ADuM7640/ADuM7641/ADuM7642/ADuM7643 1 kV RMS 四通道数字隔离器技术手册2025-06-05 2513

-

3 kV RMS双通道数字隔离器ADuM1280数据手册2023-11-29 479

-

双通道数字隔离器ADuM1200/ADuM1201数据手册2021-07-01 2021

-

ADuM220N/ADuM221N/ADuM225N/ADuM226N:5.0 kV rms双通道数字隔离器数据表2021-04-30 1009

-

ADuM1200/ADuM1201:双通道数字隔离器数据表2021-04-15 1271

-

ADuM2200/ADuM2201:双通道数字隔离器,5 kV数据表2021-04-14 1070

-

ADuM7440/ADuM7441/ADuM7442: 1 kV RMS四通道数字隔离器2021-03-21 1032

-

ADuM2280/ADuM2281/ADuM2285/ADuM2286: 5 kV RMS双通道数字隔离器2021-03-19 924

-

ADuM1280/ADuM1281/ADuM1285/ADuM1286:3 kV RMS双通道数字隔离器2021-03-18 995

-

ADUM7240 1 KV、双通道数字隔离器(2/0通道方向性)2019-02-22 551

-

1千伏双通道数字隔离器adum7240/adum7241数据表2017-10-18 841

全部0条评论

快来发表一下你的评论吧 !