ADuM4400/ADuM4401/ADuM4402 5 kV RMS四通道数字隔离器技术手册

描述

概述

ADuM440x是采用ADI公司iCoupler^®^技术的四通道数字隔离器。这些隔离器件将高速CMOS与单芯片空芯变压器技术相结合,具有优于光耦合器和其他集成耦合器等替代器件的出色性能特征。

ADuM440x隔离器提供四个独立的隔离通道,支持多种通道配置和数据速率(请参考“订购指南”)。这些型号均可采用3.0 V至5.5 V电源电压工作,与低压系统兼容,并且能够跨越隔离栅实现电压转换功能。ADuM440x隔离器具有已取得专利的刷新特性,可确保不存在输入逻辑转换时及上电/关断条件下的直流正确性。

像ADI公司的许多隔离器一样,该系列隔离器的功耗极低;在数据速率相当(最高10 Mbps)的情况下,其功耗只有同类隔离器的1/10至1/6。ADuM440x系列的所有型号均具有低脉冲宽度失真(C级小于2 ns)特性。此外,每款型号均提供输入毛刺滤波器,以防外来噪声干扰。

ADuM440x包含多项电路和布局改进,有助于其达到系统级IEC 61000-4-x要求(ESD、突波和浪涌)。对于ADuM440x,这些测试的精度主要取决于用户电路板或模块的设计与布局。欲了解更多信息,请参考应用笔记AN-793:iCoupler隔离产品的ESD/闩锁考虑因素。

数据表:*附件:ADuM4400 ADuM4401 ADuM4402 5 kV RMS四通道数字隔离器技术手册.pdf

应用

- 通用高压多通道隔离

- 医疗设备

- 电机驱动器

- 电源

特性

- 增强的系统级ESD保护性能,符合IEC 61000-4-x标准

- [安全和法规认证](RI-16封装)

- UL认证:1分钟5000 V rms,符合UL 1577标准

- CSA元件验收通知#5A

- IEC 60601-1:250 V rms(加强)

- IEC 60950-1:400 V rms(加强)

- VDE合规证书

- DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

- V

IORM= 846 V峰值

- V

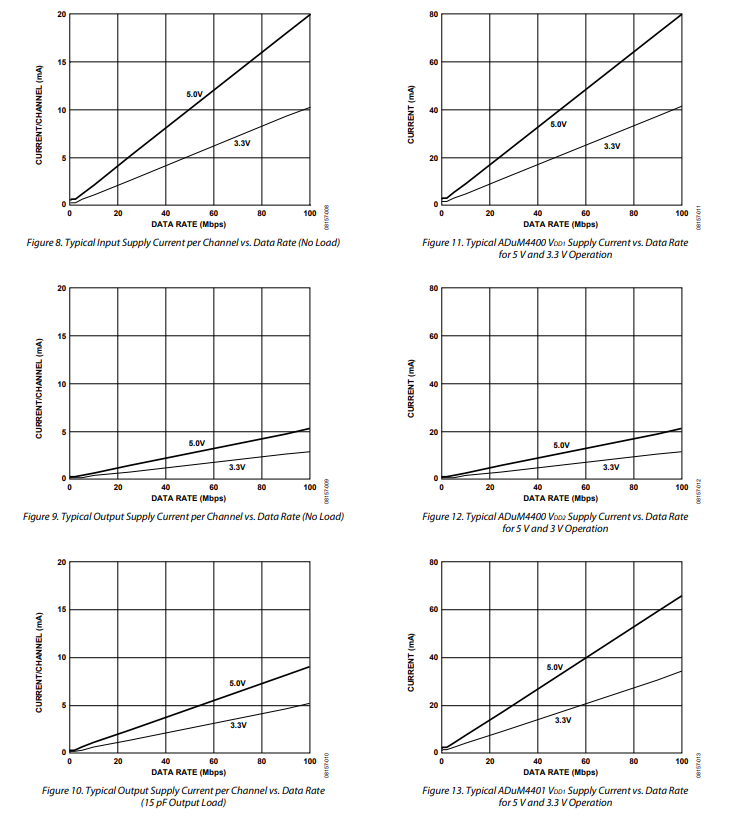

- 低功耗工作

- 5 V电源:

- 每个通道1.4 mA(最大值,0 Mbps至2 Mbps)

- 每个通道4.3 mA(最大值,10 Mbps)

- 每个通道34 mA(最大值,90 Mbps)

- 3.3 V电源

- 每个通道0.9 mA(最大值,0 Mbps至2 Mbps)

- 每个通道2.4 mA(最大值,10 Mbps)

- 每个通道20 mA(最大值,90 Mbps)

- 5 V电源:

- 双向通信

- 3.3 V/5 V电平转换

- 工作温度高达:105°C

- 高数据速率:DC至90 Mbps (NRZ)

- 精密时序特性

- 脉冲宽度失真:2 ns(最大值)

- 通道间匹配:2 ns(最大值)

- 高共模瞬变抗扰度:>25 kV/μs

- 输出使能功能

- 16引脚宽体SOIC封装版本(RW-16)

- 16引脚宽体SOIC封装版本,增强爬电距离(RI-16)

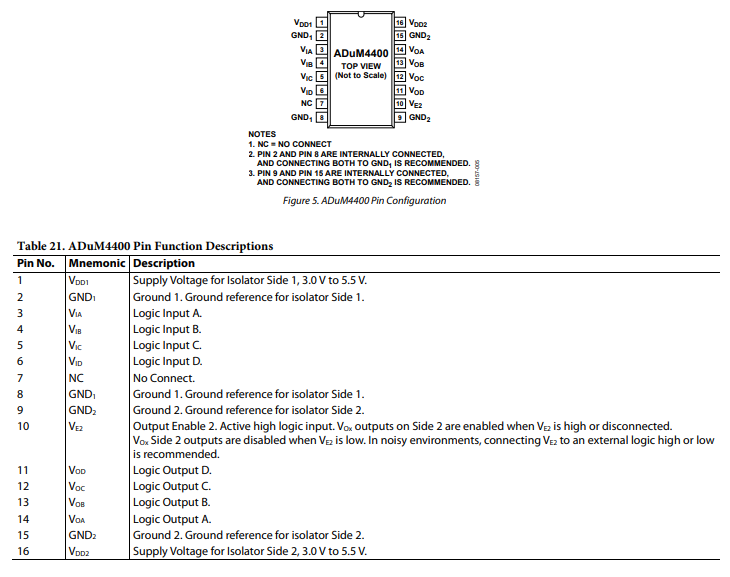

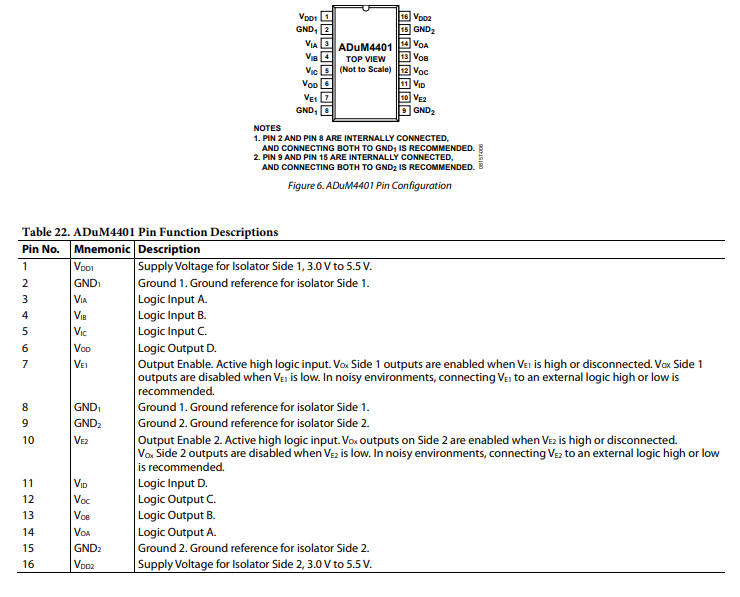

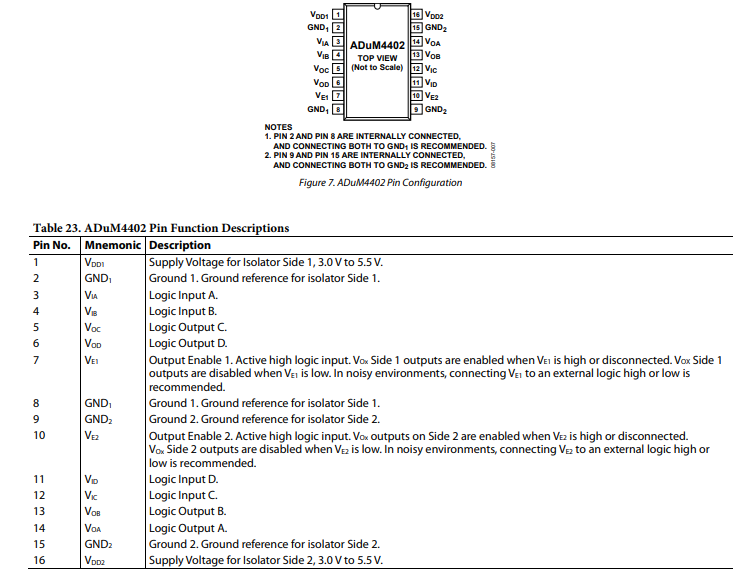

引脚配置描述

典型性能特征

应用信息

印刷电路板布局

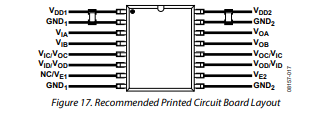

ADuM440x 数字隔离器的逻辑接口无需外部接口电路。强烈建议在输入和输出电源引脚处进行电源去耦(见图 17 )。去耦电容最便于连接在 Pin 1 和 Pin 2(针对 V_{CC1} )以及 Pin 15 和 Pin 16(针对 V_{CC2} )之间。电容值应为 0.01μF 至 0.1μF 。电容两端与输入电源引脚之间的总引线长度均不得超过 20mm 。另外,除非每个封装侧的接地对都靠近封装连接,否则还应考虑 Pin 1 与 Pin 8 之间以及 Pin 9 与 Pin 16 之间的连接。

在涉及高共模瞬变的应用中,务必使电路板布局(跨隔离栅)的设计将耦合降至最低。此外,电路板布局应设计为:在给定的器件侧,任何产生的耦合都能均匀影响所有引脚。若不这样做,可能会导致引脚间出现电压差,超过器件的绝对最大额定值,进而致使器件闩锁或永久损坏。

有关电路板布局指南,请参阅 AN - 1109《应用笔记:与印刷电路板相关的布局》。

系统级静电放电(ESD)注意事项及增强功能

系统级 ESD 可靠性(例如,符合 IEC 61000 - 4 - x 标准)在很大程度上取决于系统设计,而系统设计因应用而异。ADuM440x 集成了许多增强功能,以降低对系统设计的依赖,从而实现更可靠的 ESD 性能。这些增强功能包括:

- 在所有输入/输出引脚上添加 ESD 保护单元。

- 通过采用更宽的几何形状和并联走线,降低关键金属走线的电阻。

- 通过在 PMOS 和 NMOS 器件之间采用保护和隔离技术,最大限度地减少 CMOS 器件中固有的串扰效应。

- 使用 45° 角的电源引脚走线,消除高电场集中区域。

- 通过在每个电源引脚与其相应的地之间采用更大的 ESD 钳位,防止电源引脚金属迁移。

虽然 ADuM440x 可提高系统级 ESD 可靠性,但它们无法替代稳健的系统级设计。有关采用 iCoupler 隔离产品的 ESD/闩锁注意事项,请参阅 AN - 793《应用笔记》,其中针对电路板布局和系统级设计提供了详细建议。

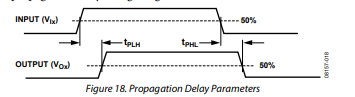

传播延迟相关参数

传播延迟是描述逻辑信号通过一个组件传播所需时间的参数。信号到逻辑低电平输出的传播延迟,可能与到逻辑高电平输出的传播延迟不同。

脉冲宽度失真是指这两种传播延迟值之间的最大差异,它体现了输入信号定时的保持精度。

通道间匹配指的是单个 ADuM440x 器件内各通道之间传播延迟差异的最大量。

传播延迟差异指的是在相同条件下工作的多个 ADuM440x 器件之间传播延迟差异的最大量。

直流正确性和磁场抗扰度

隔离器输入的正向和负向逻辑转换,会使较窄(~1 ns )的脉冲通过变压器发送至解码器,进而对解码器进行置位或复位,表明有输入逻辑转换。在输入逻辑转换缺失(即输入为逻辑 1 持续超过约 1μs )时,会发送一组周期性的刷新脉冲,以确保输出的直流正确性,表明正确的输入状态。

如果解码器在约 5μs 以上的时间内未收到脉冲,则认为输入侧未通电或无功能,此时隔离器输出会被看门狗电路强制置为默认低电平状态(见表 20 )。

ADuM440x 的磁场抗扰度极限由以下条件设定:变压器接收线圈中感应的电压足够大,会错误地置位或复位解码器。以下分析明确了这种情况发生的条件。对 ADuM440x 在 3V 工作条件下进行研究,因为这代表了该产品最敏感的工作模式。

-

ADuM6400/ADuM6401/ADuM6402/ADuM6403/ADuM6404:四通道数字隔离器的技术剖析与应用指南2026-03-11 196

-

ADuM250N/ADuM251N/ADuM252N:5.0 kV rms,5通道数字隔离器数据表2021-05-24 1085

-

ADuM2400/ADuM2401/ADuM2402:四通道数字隔离器数据表2021-05-22 1057

-

ADuM3440/ADuM3441/ADuM3442:四通道高速数字隔离器产品手册2021-04-30 1186

-

ADuM1400/ADuM1401/ADuM1402:四通道数字隔离器数据表2021-04-25 1223

-

ADuM7440/ADuM7441/ADuM7442: 1 kV RMS四通道数字隔离器2021-03-21 1033

-

ADuM140D/ADuM140E/ADuM141D/ADuM141E/ADuM142D/ADuM142E:3.75 kV rms 四通道数字隔离器2021-03-20 1201

-

ADuM1410/ADuM1411/ADuM1412:四通道数字隔离器 数据手册2021-03-19 1257

-

ADUM4400 5 kV RMS四通道数字隔离器2019-02-22 456

-

5千伏rms四通道数字隔离器adum4400w/adum4401w/adum4402w汽车产品2017-10-18 1013

全部0条评论

快来发表一下你的评论吧 !