ADuM3300/ADuM3301三通道数字隔离器技术手册

描述

概述

[ADuM3300]/ADuM3301均为采用ADI公司iCoupler ^®^ 技术的3通道数字隔离器。这些隔离器件将高速CMOS与单芯片空芯变压器技术融为一体,具有优于光耦合器等替代器件的出色性能特征。

iCoupler器件不存在一般与光耦合器相关的设计困难。简单的iCoupler数字接口和稳定的性能特征,可消除光耦合器通常具有的电流传输比不确定、非线性传递函数以及温度和使用寿命影响等问题。这些iCoupler产品不需要外部驱动器和其它分立器件。此外,在信号数据速率相当的情况下,iCoupler器件的功耗只有光耦合器的1/10至1/6。

ADuM3300/ADuM3301隔离器提供三个独立的隔离通道,支持多种通道配置和数据速率。所有型号均可采用3.3 V至5.5 V电源电压工作,与低压系统兼容,并且能够跨越隔离栅实现电压转换功能。ADuM3300/ADuM3301隔离器具有已取得专利的刷新特性,可确保不存在输入逻辑转换时及上电/关断条件下的直流正确性。

与ADuM1300/ADuM1301隔离器相比,ADuM3300/ADuM3301隔离器包含多项电路和布局改进,系统级IEC 61000-4-x测试(ESD、突波和浪涌)显示其性能大大增强。对于ADuM1300/ADuM1301或ADuM3300/ADuM3301产品,这些测试的精度主要取决于用户系统的设计与布局。

数据表:*附件:ADuM3300 ADuM3301三通道数字隔离器技术手册.pdf

应用

- 通用多通道隔离

- SPI接口/数据转换器隔离

- RS-232/RS-422/RS-485收发器

- 工业现场总线隔离

特性

- 增强的系统级ESD保护性能,符合IEC 61000-4-x标准

- 低功耗工作

- 5 V电源:

- 每个通道2.0 mA(最大值,0 Mbps至2 Mbps)

- 每个通道4.1 mA(最大值,10 Mbps)

- 每个通道36 mA(最大值,90 Mbps)

- 3.3 V电源:

- 每个通道1.0 mA(最大值,0 Mbps至2 Mbps)

- 每个通道2.8 mA(最大值,10 Mbps)

- 每个通道17 mA(最大值,90 Mbps)

- 5 V电源:

- 双向通信

- 3.3 V/5 V电平转换

- 工作温度高达:105°C

- 高数据速率:DC至90 Mbps (NRZ)

- 精密时序特性

- 脉冲宽度失真:2 ns(最大值)

- 通道间匹配:2 ns(最大值)

- 高共模瞬变抗扰度:>25 kV/μs

- 输出使能功能

- 16引脚宽体SOIC封装,符合RoHS标准

- 安全和法规认证

- UL认证:1分钟2500 V rms,符合UL 1577标准

- CSA元件验收通知5A

- VDE合规证书

- DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

- VIORM = 560 V峰值

- CQC认证符合GB4943.1-2011

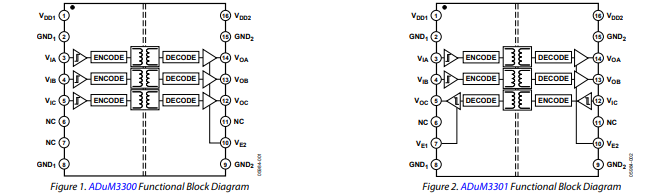

功能框图

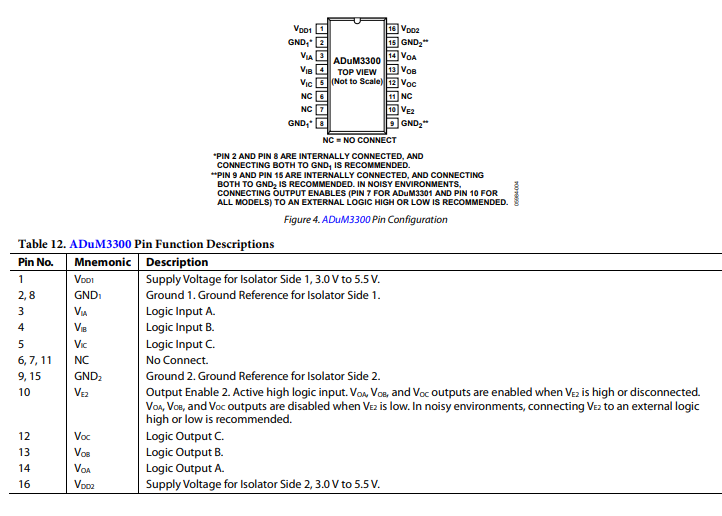

引脚配置描述

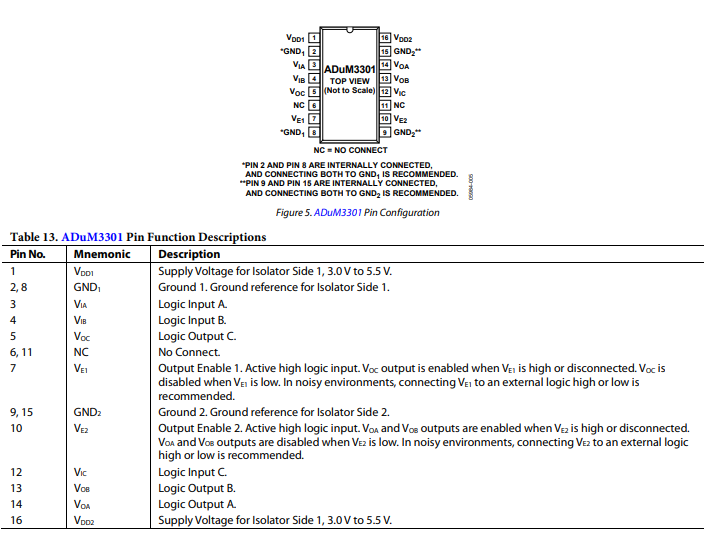

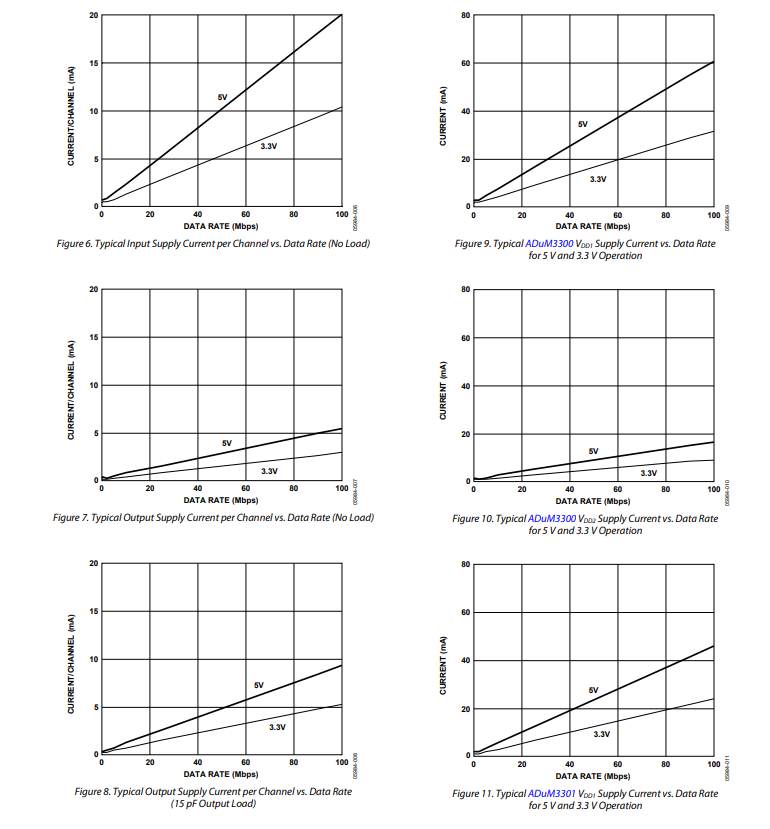

典型性能特征

应用布局

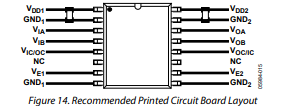

印刷电路板布局

ADuM3300/ADuM3301数字隔离器的逻辑接口无需外部接口电路。强烈建议对电源引脚进行旁路滤波。电源旁路电容在输入和输出侧最为常用,可在引脚1和引脚16(针对VDD1)以及引脚2(针对VDD2)和引脚15之间连接。电容值应在0.01μF至0.1μF之间,且电容两端的总引线路径应不超过20mm。除非封装两侧的接地引脚靠近封装连接,否则应考虑在引脚1与引脚8之间以及引脚9与引脚16之间进行旁路。

在涉及高共模瞬变的应用中,应注意确保隔离栅上不会发生进一步的耦合。电路板布局应设计为使任何给定组件侧发生的耦合效应均匀分布。未能做到这一点可能会导致引脚之间的电压差超过器件的绝对最大额定值,从而导致闩锁或永久性损坏。有关电路板布局指南,请参见AN - 1109应用笔记。

系统级静电放电(ESD)考虑因素及增强措施

符合IEC 61000 - 4 - x等标准的系统级ESD可靠性在很大程度上取决于系统设计,而系统设计因应用而异。ADuM3300/ADuM3301采用了许多增强措施,以使ESD可靠性对系统设计的依赖程度降低。这些增强措施包括:

- 在所有输入/输出接口添加ESD保护单元

- 通过更宽的金属走线几何形状、走线的平行排列和过孔,减少关键走线的串扰

- 利用CMOS器件中固有的硅控整流器(SCR)效应,通过在PMOS和NMOS器件之间采用接地和隔离技术,将其影响降至最低

- 使用金属走线上的45°拐角,消除高电场集中区域

- 通过更大的ESD钳位,防止每个电源引脚及其相应接地之间的电源引脚过压

虽然ADuM3300/ADuM3301提高了系统级ESD可靠性,但它们无法替代稳健的系统级设计。有关电路板布局和系统级设计的详细考虑因素,请参见应用笔记AN - 793《ESD/闩锁考虑因素与Coupler隔离产品》。

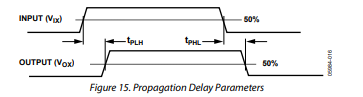

传播延迟相关参数

传播延迟是一个描述逻辑信号通过组件传播所需时间的参数。到逻辑低电平输出的传播延迟可能与到逻辑高电平输出的传播延迟不同。

脉冲宽度失真指的是这两个传播延迟值之间的最大差异,它表明输入信号的定时能在多大程度上得到准确保留。

通道间匹配是指单个ADuM3300/ADuM3301组件内不同通道之间传播延迟的最大差异。

传播延迟偏差是指在相同条件下工作的多个ADuM3300/ADuM3301组件之间传播延迟的最大差异。

直流正确性和磁场抗扰度

正逻辑和负逻辑转换会使隔离器输入产生窄(~1ns)脉冲,通过变压器发送到解码器。解码器无法区分这些脉冲,因此会根据输入的逻辑转换设置或重置内部计数器。在没有逻辑转换脉冲的情况下,会向解码器发送一组周期为大于1μs的更窄脉冲,以确保输出的直流正确性。如果解码器在超过5μs的时间内未收到任何脉冲,则假定输入未通电或出现故障,在这种情况下,隔离器输出将被强制为默认状态(参见表11中的看门狗定时器电路)。

ADuM3300/ADuM3301的磁场抗扰度限制在于,变压器中感应的电压会使解码器的接收线圈充分偏置,从而错误地设置或重置解码器。以下分析定义了ADuM3300/ADuM3301可能出错的条件。ADuM3300/ADuM3301的3V工作条件是最容易受到影响的工作模式,因此对其进行了考察 。

-

ADuM6400/ADuM6401/ADuM6402/ADuM6403/ADuM6404:四通道数字隔离器的技术剖析与应用指南2026-03-11 285

-

ADuM2400/ADuM2401/ADuM2402四通道数字隔离器技术手册2025-06-05 1847

-

ADuM230D/ADuM230E/ADuM231D/ADuM231E:5.0 kV rms三通道数字隔离器数据表2021-05-24 1063

-

ADuM2400/ADuM2401/ADuM2402:四通道数字隔离器数据表2021-05-22 1085

-

ADuM3440/ADuM3441/ADuM3442:四通道高速数字隔离器产品手册2021-04-30 1235

-

ADuM130D/ADuM130E/ADuM131D/ADuM131E:3.75 kV rms三通道数字隔离器数据表2021-04-26 917

-

ADuM1400/ADuM1401/ADuM1402:四通道数字隔离器数据表2021-04-25 1251

-

ADuM1300/ADuM1301:三通道数字隔离器数据表2021-04-17 1162

-

ADuM7440/ADuM7441/ADuM7442: 1 kV RMS四通道数字隔离器2021-03-21 1072

-

ADuM1410/ADuM1411/ADuM1412:四通道数字隔离器 数据手册2021-03-19 1295

-

ADUM3300 三通道数字隔离器,具有增强的系统级ESD可靠性(3/0通道方向性)2019-02-22 362

-

三通道数字隔离器增强系统级ESD可靠性adum3300/adum3301数据表2017-10-18 819

全部0条评论

快来发表一下你的评论吧 !