RISC-V架构CPU的RAS解决方案

描述

RISC-V架构以追赶者的姿态在多个应用领域与X86架构和ARM架构展开竞争。在服务器应用领域,RISC-V架构正在重新定义服务器芯片领域必备的安全、虚拟化和RAS等规格和规范。

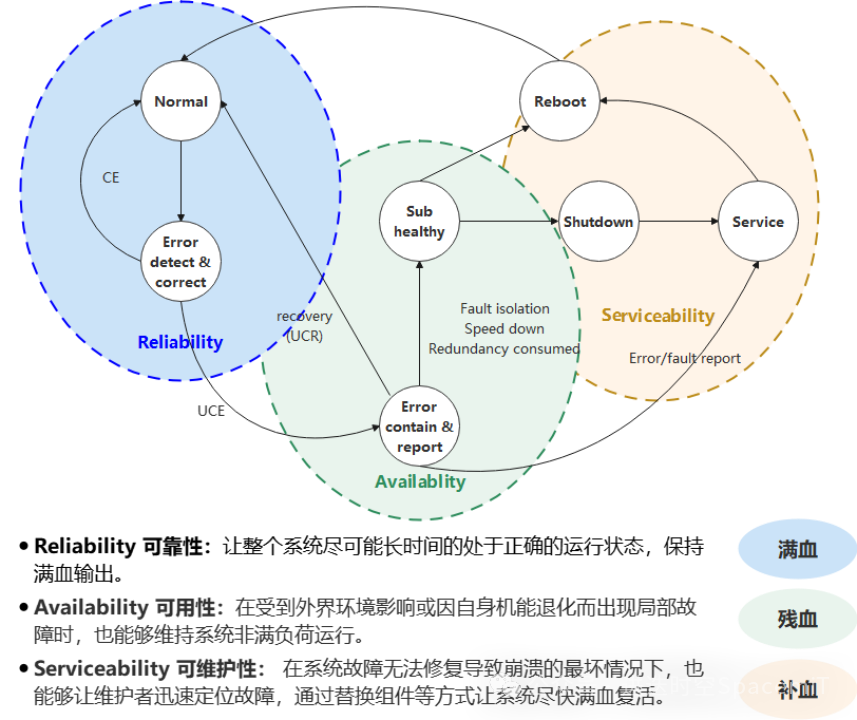

服务器CPU芯片作为服务器核心部件,承担了CPU算力、高速内存接口和高速IO传输接口等功能。从应用场景和需求出发,RAS(Reliability、Availability、Serviceability)已经成为服务器系统必备的功能属性:高可靠性(Reliability)可以延长整个系统硬件“满血”运行的持续时间,此阶段为服务器系统最理想状态;高可用性(Availability)使得硬件系统发生随机或者持续硬件故障时,通过软硬件协同处理,系统仍然可以维持“残血”运行,不至于因为关机导致服务中断;高可维护性(Serviceability)使得在系统崩溃时,能够迅速定位故障,通过替换部件等方式对服务器进行“补血”,为系统尽快恢复运行提供保障。

(图1: RAS定义框架)

进迭时空以RISC-V高性能算力计算核心SpacemiT X100 Core 为基础构建的服务器CPU芯片,充分考虑了服务器的RAS需求,集成了包含RAS组件功能特性和RAS管理功能特性的完整RAS软硬件方案,并在应用层上对X86和ARM服务器的RAS方案做了兼容适配:RAS处理机制遵循Firmware First准则;通过RISC-V协议栈,支持ACPI的APEI规范,获得面向OS的错误信息格式兼容。进迭时空的RAS方案完全遵循RISC-V RERI (RAS Error Record Register Interface)故障处理接口规范,通过内存映射的寄存器接口统一了各种RAS信息的记录和上报。

进迭时空RAS组件架构

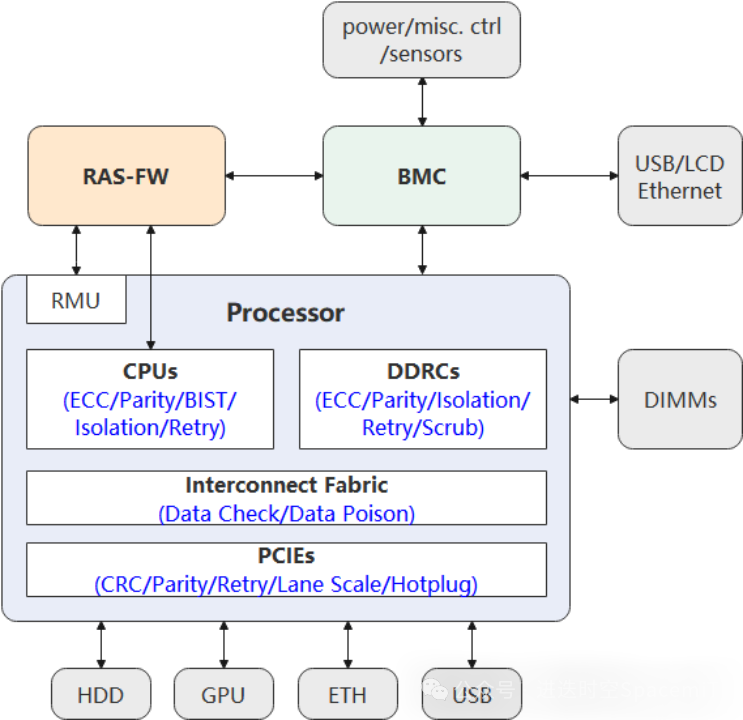

进迭时空服务器CPU芯片的RAS硬件方案主要围绕SpacemiT X100 Core、DDR控制器、PCIe控制器、片上互连总线等几个核心部件展开。

(图2: 进迭时空RAS组件架构)

SpacemiT X100 Core 和 Cluster

- 实现L1/L2 Cache的Parity校验和ECC,TLB 的Parity校验,对于Parity错误和ECC不可纠正错误会进行Cache line invalid并Reload,对于ECC可纠正错误会进行数据回刷 (Scrubbing);

- 实现系统总线数据的Data check和Data poison检测,在Core读取Cache line时若检测到数据错误则触发异常中断;

- 集成Core Boot MBIST,在启动中测试CPU内部的所有RAM单元,若MBIST failed则通知系统启动固件对Core进行隔离;

- 集成RISC-V规范RAS RERI接口模块;

- 支持Warm Reset,允许在保留RAS错误信息的同时重启CPU核。

DDR控制器

- 实现控制器端系统总线数据的Data check和Data poison;

- 实现控制器内部RAM的Parity校验;

- 通过ECC机制实现对DRAM的命令式和自动式巡检回刷 (Scrubbing);

- 对DRAM读写数据进行CRC校验,若有错误自动Retry;

- 支持DDR5的EAPAR(Encoded Address Parity)机制;

- 支持72-bit和80-bit的DDR5 ECC DIMM,可以实现内存颗粒Chipkill功能;

- 支持对DRAM颗粒的PPR(Post Package Repair)修复功能。

PCIe控制器

实现控制器端系统总线数据的Data check和Data poison;

实现控制器内部RAM的Parity校验;

支持传输层的ECRC校验;

支持链接层的LCRC校验;

在Lane training failed时,可以进行Lane isolation;

支持PCIe设备热插拔。

片上互连总线

实现所有总线数据的Data check和Data poison;

实现互连总线的错误Response传递;

支持SLC和SF的RAM ECC;

支持片间互连总线接口的ECRC和LCRC校验。

进迭时空RAS管理架构

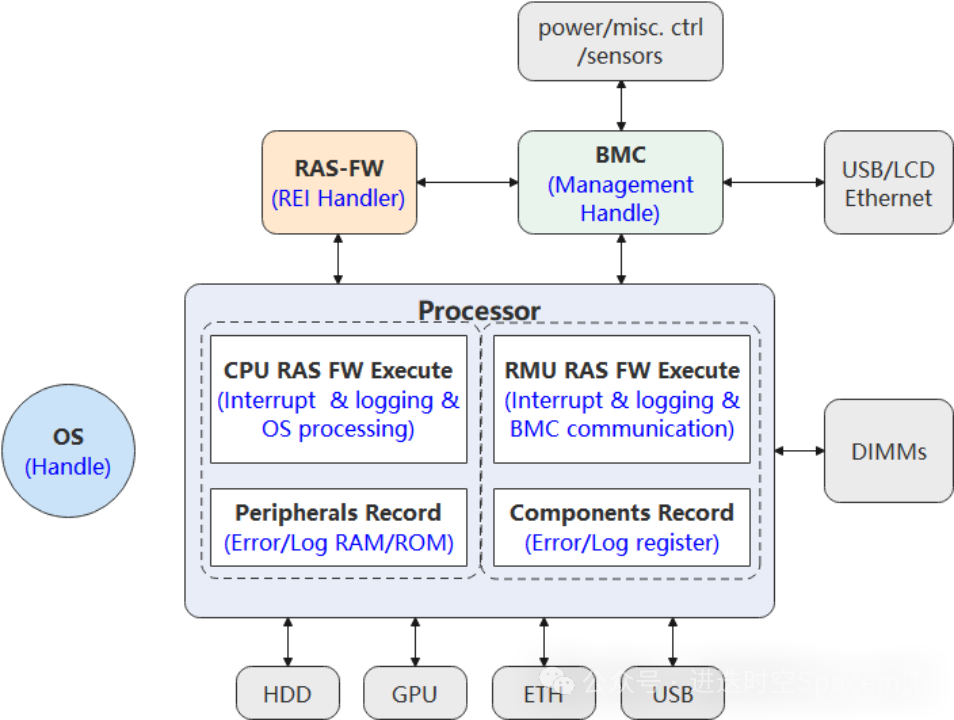

(图3: 进迭时空RAS管理架构)

服务器CPU芯片对RAS信息的处理主要通过SpacemiT X100 Core 主CPU单元和RMU管理单元实现,两者协同分工,实现了对本芯片中所有重要系统组件和多芯互连系统中其他芯片的RAS处理(如OS交互、BIOS固件执行、带外BMC通信等),极大提升了RAS处理的可靠性,它的管理架构特性主要有:

SpacemiT X100 Core 支持RAS中断接口,通过Cluster内部RERI模块,实现符合RISC-V RERI规范的CPU核故障记录和异常中断;

PCIe支持符合规范的AER(Advanced Error Reporting);

通过CPU芯片的管理单元(RMU),实现整芯片RAS错误故障的异常处理:故障信息收集和存储、故障的软件通知和处理;

通过CPU芯片的带外接口,实现BMC芯片的带外RAS故障收集和交互。

进迭时空通过由RAS功能组件和RAS管理软硬件架构协同组建的RAS系统,实现完整的RISC-V架构服务器RAS解决方案,即将推出业界首个完整支持服务器RAS的CPU产品。

文字:博志、风行、Stephen、hw、Zetalog审核:Sophie

-

Imagination CPU 系列研讨会 | RISC-V 平台的性能分析和调试2024-08-10 964

-

两大架构RISC-V 和 ARM 的各种关系2023-06-21 1298

-

倪光南院士:RISC-V是中国最受欢迎CPU架构,不受垄断制约2023-05-28 8108

-

谈一谈RISC-V架构的优势和特点2023-05-14 1978

-

RISC-V架构2023-04-03 2016

-

RISC-V推动下的CPU架构变局2022-02-22 3812

-

聚焦RISC-V架构,避免主流CPU架构制约2021-12-21 1015

-

RISC-V架构简介2021-07-28 3852

-

基于RISC-V开放架构的存算一体化芯片解决方案2021-06-23 3541

-

ARM与RISC-V架构的区别是什么?2021-04-25 6531

-

瑞萨基于RISC-V核心架构的预编程ASSP器件2020-10-13 2526

-

科普RISC-V生态架构(认识RISC-V)2020-08-02 6972

-

为什么选择RISC-V?2020-07-27 5013

-

RISC-V 生态架构浅析2020-06-22 3088

全部0条评论

快来发表一下你的评论吧 !