Analog Devices Inc. ADSP-SC598双SHARC+®数字信号处理器数据手册

描述

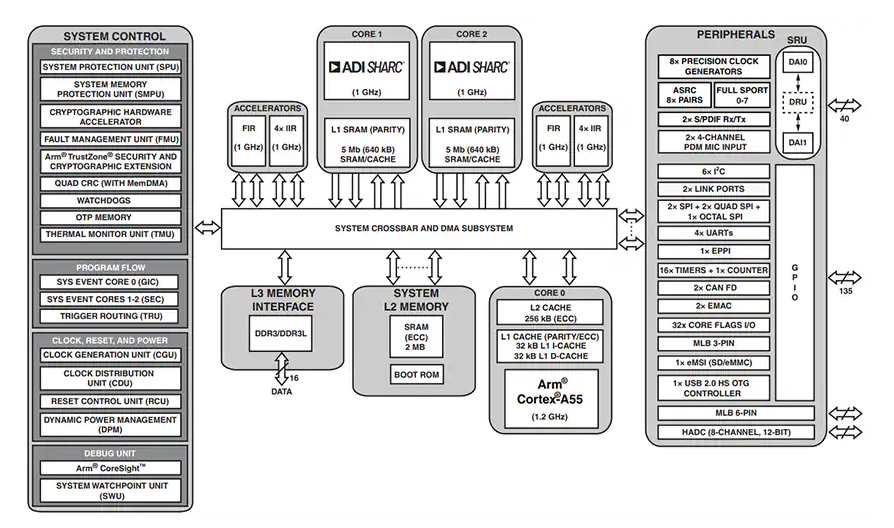

Analog Devices ADSP-SC598双SHARC+® 数字信号处理器 (DSP) 采用集成式Arm® Cortex-A55,运行频率高达1.2GHz。A55处理器带有FPU和Neon® DSP扩展,可处理额外的实时处理任务,并管理用于连接音频应用中关键时间数据的外设。这些接口包括千兆以太网、USB高速、CAN FD和各种其他连接选项,可实现灵活简化的系统设计。

数据手册:*附件:Analog Devices Inc. ADSP-SC598双SHARC+®数字信号处理器数据手册.pdf

ADSP-SC598 SHARC处理器采用Analog Devices Super Harvard架构。这些32位/40位/64位浮点处理器优化用于高性能音频/浮点应用,具有大型片上静态随机存取存储器(SRAM)、可消除输入/输出(I/O)瓶颈的多条内部总线以及创新的数字音频接口(DAI)。SHARC+内核包括缓存增强和分支预测,同时保留与SHARC前代产品的指令集兼容性。

SHARC+处理器集成一系列丰富的业内领先系统外设和存储器,是需要在单一集成封装内提供类似于精简指令集计算(RISC)可编程性、多媒体支持和前沿信号处理应用的首选平台。此类应用包括需要高浮点性能的汽车、专业音频和工业应用。

特性

- SHARC+内核基础架构

- 内核时钟频率:800MHz(最大值)或1GHz(最大值)

- 2个640KB片上1级(L1)SRAM存储器(带奇偶校验)提高了低延迟性能

- 支持32位、40位和64位浮点

- 32位定点

- 字节、短字、字和长字寻址

- 强大的DMA系统

- 16位DDR/DDR3L内存控制器,1.35V支持DDR3L

- 存储器

- 2048KB片上2级(L2)SRAM(带ECC保护),在许多用例中无需外部存储器

- 3级(L3)接口,优化用于降低系统功耗,为DDR3提供16位接口(支持1.35V DDR3L器件)

- 高级硬件加速器

- 增强型FIR/IIR卸载引擎以内核时钟频率运行,可提高处理能力

- 采用OTP的安全加密引擎

- 数字音频接口(DAI)

- 8个全SPORT接口,具有TDM和^I2S^模式

- 2个S/PDIF Rx/Tx、8个ASRC对

- 8个精密时钟发生器

- 2个4通道PDM麦克风输入

- 40个缓冲

- Arm核心基础设施

- 1.2GHz ARM Cortex-A55(带Neon/FPU)

- 32kByte/32kByte L1指令/数据缓存

- 256kByte L2缓存

- 其他外设连接/接口

- 1个eMSI(SDIO/eMMC)

- 2个四通道SPI、1个八通道SPI

- MLB 3引脚/6引脚

- 6个 ^I2C^ 、3个UART

- 2个链路端口

- 16个通用定时器、1个通用计数器

- 3个看门狗计时器

- ePPI

- USB 2.0 HS OTG控制器

- 10/100 EMAC

- 10/100/1000 EMAC,带AVB和1588

- 2个CAN FD

- 8通道12位内务ADC

- 135个GPIO引脚、40个DAI引脚

- 热传感器

- 17mmx17mm(0.8mm间距)400焊球CSP_BGA封装

- 安全和保护

- 加密硬件加速器

- 快速安全引导,支持IP保护

- 增强型FIR和IIR加速器,运行频率高达1GHz

- 符合汽车应用类AEC-Q100标准

应用

- 消费类和专业音频

- 扬声器

- 条形音箱

- AVR

- 会议系统

- 调光台

- 麦克风阵列

- 耳机

- 汽车

- 音频放大器

- 音响主机

- ANC/RNC

- 后座娱乐系统

- 数字驾驶舱

- ADAS

处理器框图

相关文章

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

32位浮点数字信号处理器SHARC产品组合(ADI)2010-04-10 1624

-

EE-208型:考虑ADSP-21262 SHARC®数字信号处理器2021-04-15 932

-

EE-401:ADSP-SC5xx/215xx SHARC+处理器系统优化技术2021-04-23 848

-

ADSP-SC58x/ADSP-2158x SHARC+处理器硬件参考(1.0版)2021-04-26 907

-

EE-400:在ADSP-SC5xx/ADSP-215xx SHARC+处理器上使用缓存2021-04-27 1003

-

ADSP-21562/21563/21565:SHARC+单核高性能数字信号处理器(高达1 GHz)初步数据表2021-04-29 1568

-

ADSP-21160M/ADSP-21160N:SHARC数字信号处理器数据表2021-04-30 1030

-

ADSP-21566/21567/21569 SHARC+单核高性能数字信号处理器(高达1 GHz)产品手册2021-05-23 909

-

ADSP-21160M/ADSP-21160N:SHARC数字信号处理器数据手册2025-01-03 517

-

ADSP1802 SHARC处理器技术手册2025-05-12 1894

-

Analog Devices Inc. ADSP1802 SHARC®处理器数据手册2025-05-29 1888

-

Analog Devices Inc. ADSP-SC592 SHARC+®双核DSP数据手册2025-06-07 1593

-

Analog Devices Inc. EV-SC598-SOM模块化系统板数据手册2025-06-10 1198

-

Analog Devices Inc. ADSP-21594/ADSP-SC594 SHARC+双核DSP数据手册2025-06-11 1269

-

Analog Devices Inc. ADSP-21591/ADSP-21593 SHARC+ 双核DSP数据手册2025-06-24 1826

全部0条评论

快来发表一下你的评论吧 !