电子系统对LDO稳压器的要求

描述

欢迎来到芝识课堂!上篇我们了解了LDO稳压器的基本定义、内部原理、工作方式以及它们的电气特性。在本篇中,您将了解电子系统对LDO稳压器的要求,以及优化电源布局的解决方案和板上供电的关键设计原则。

电子设备为何需要LDO稳压器

在电子设备中,LDO稳压器是实现系统稳定运行的关键部件。

传统电子系统,电源电路或稳压器IC(例如电源管理IC,也就是PMIC,它能够对系统里多条电源线进行有效管理)常常被用在电路板上,目的是为每一个电路或IC供应所需的电压,以此保障各个电路正常运转。

然而,实际情况并非一帆风顺。电路板上较长的布线会产生电阻,进而导致出现显著的压降现象;同时,电路板平行布线之间存在的串扰问题,经常会对那些对噪声敏感的器件造成干扰。为了妥善解决这些棘手的问题,负载点(POL)稳压器IC应运而生,它们能够在局部形成每个电路或IC所需要的电压。

如今,电子设备朝着高性能、小尺寸以及强通用性的方向不断发展。在此背景下,电路变得越发复杂,并且对节能的要求也日益提高。在这样的趋势下,众多电路和IC开始采用低电压供电来工作。

除此之外,传感器以及高精度模拟电路对电路设计提出了低噪声的严格要求。这一系列变化,都凸显出LDO稳压器在当下电子设备中的重要性与必要性。

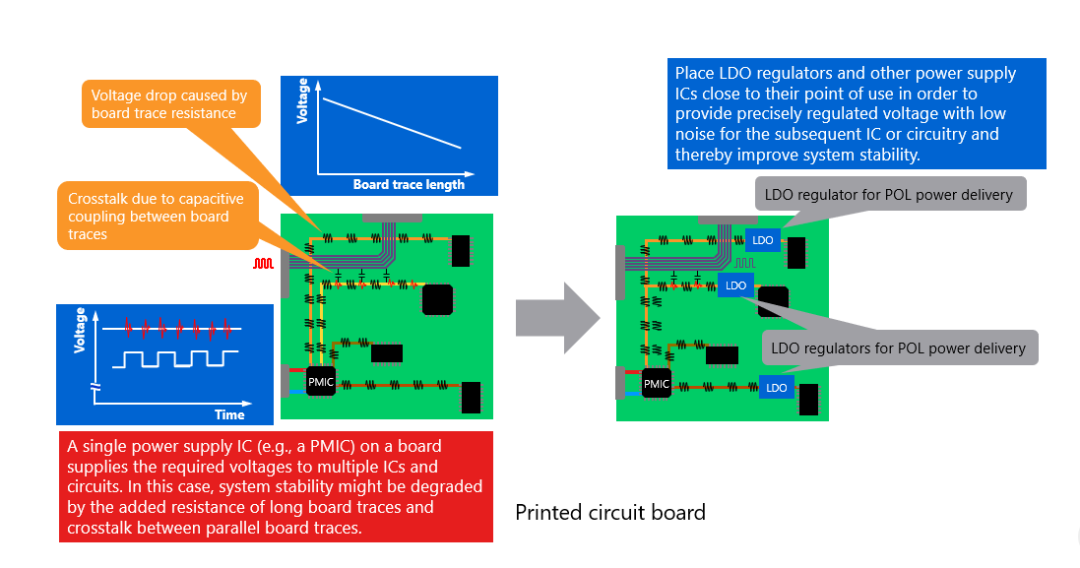

如图1左侧所示,电路板设计中因电源走线设计不当会引发两大问题:长电路板迹线电阻引起的远端电压降会引起电压与时间波形不稳定;而电路板并行迹线之间的电容耦合引起的串扰(信号重叠),高频或敏感信号可能被噪声污染,导致信号完整性(SI)问题。

该板使用单个电源IC(例如PMIC)为多个IC和电路提供所需的电压。在这种情况下,长板迹线的电阻增加和平行板迹线之间的串扰可能会降低系统稳定性。

另外,这种一对多的负载供电可能会导致远端器件因电压不足而工作异常,降低系统稳定性。

图1右侧是优化电源布局的解决方案,将LDO稳压器靠近负载,缩短供电走线长度,从而减少走线电阻,避免电压降;降低走线电感,抑制噪声信号;提供更精准的稳压输出(低噪声、高稳定性)。

图1. 电路板设计需要考虑的问题

在这里,为您推荐几个板上供电的关键设计原则。

减少串扰:为有效降低电容耦合效应,在设计时需着重关注走线规划。合理拉开走线间距,尽可能避免长距离的并行走线,同时巧妙运用地平面进行隔离。这些举措有助于减少线路间的相互干扰,保障信号传输的稳定性。

电源完整性(PI):实现良好的电源完整性同样要注意走线设计。采用短而宽的走线方式,能够降低线路电阻与电感,减少电压降和电磁干扰。此外,合理布置去耦电容也很重要,它可以有效滤除电源中的高频噪声,为电路提供稳定纯净的电源。

信号完整性(SI):在布线过程中,还要留意信号布局,防止敏感信号与电源信号或高频信号并行敷设。因为并行走线容易引发串扰,干扰敏感信号的正常传输,进而影响整个系统的性能。

LDO与PMIC分工:PMIC承担着全局电源分配的重任,负责将输入电源合理分配到系统的各个部分,确保整体供电架构的稳定与协调。LDO则主要用于局部(POL)的精密稳压。由于PMIC到局部电路的走线可能较长,会产生一定的电压降和干扰,LDO正好可以弥补这一不足,为局部电路提供精准稳定的电压。

值得一提的是,东芝提供的LDO稳压器产品具有先进模拟电路供电特别需要的低噪声、高波纹抑制比(PSRR)、高输出电流稳定性(负载瞬态响应)和低电流消耗等特性。

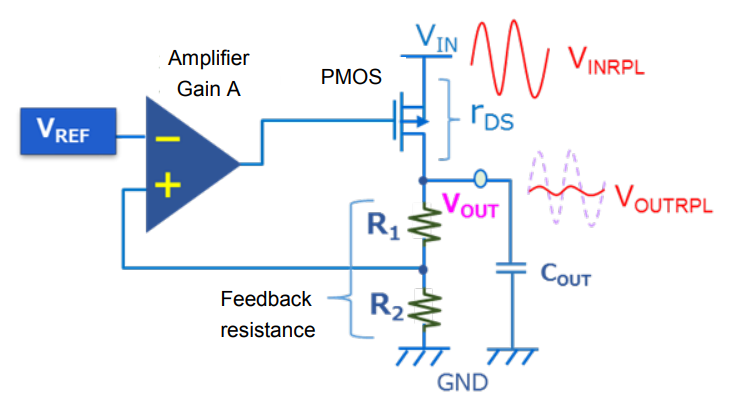

图2. 典型LDO及其PSRR电路图

此外,东芝开发的新一代工艺成效显著,大幅优化了LDO稳压器的压差特性,推出更为高效的线性稳压器解决方案。

本篇我们了解了电子系统对LDO稳压器的要求,以及优化电源布局的解决方案和板上供电的关键设计原则。下篇我们将进一步分享几种稳压器的工作原理、功能和电路配置。

关于东芝电子元件及存储装置株式会社

东芝电子元件及存储装置株式会社是先进的半导体和存储解决方案的领先供应商,公司累积了半个多世纪的经验和创新,为客户和合作伙伴提供分立半导体、系统LSI和HDD领域的杰出解决方案。

东芝电子元件及存储装置株式会社十分注重与客户的密切协作,旨在促进价值共创,共同开拓新市场,期待为世界各地的人们建设更美好的未来并做出贡献。

-

线性稳压器和开关稳压器、串联稳压器的区别2025-07-18 1731

-

LDO稳压器的负载瞬态响应特性2024-09-11 5183

-

浅析线性稳压器(LDO)2021-11-12 1894

-

怎样去使用LDO稳压器2021-11-10 1386

-

汽车电子系统对性能的要求有哪些?2021-05-17 2448

-

LT8210汽车电子系统演示电路直通稳压器,效率99.9%(3-100V至12V@5A)2021-03-23 1544

-

电源 IC 应用在汽车电子系统有什么样的要求?2021-03-06 1866

-

使用误差放大器设计LDO线性稳压器的论文说明2019-12-04 1784

-

汽车电子系统苛刻挑战谁来应对2019-05-13 1853

-

低压降线性稳压器(LDO)应用教程2019-01-17 4798

-

【下载】《电子系统专题设计与制作》2018-04-16 16478

-

LDO低压差线性稳压器2012-12-25 4234

-

稳压器在电源中的重要作用2012-12-02 2289

全部0条评论

快来发表一下你的评论吧 !