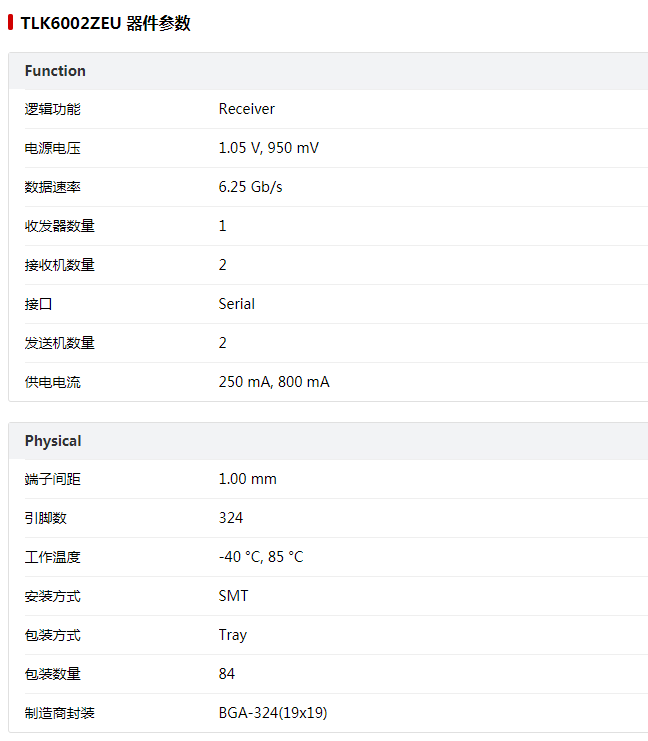

Texas Instruments TLK6002ZEU 6千兆位每秒 (Gbps) 的双通道串行器-解串器 EDA模型与数据手册解析

描述

给大家带来Texas Instruments (TI)推出的 TLK6002ZEU参数特性、引脚 EDA模型与数据手册解析。

TLK6002是德州仪器 (TI) 很久之前就推出的业界首款 6 千兆位每秒 (Gbps) 的双通道串行器-解串器 IC (SerDes),其可为无线应用提供 高达470 兆位每秒 (Mbps) 至6.25 Gbps 的连续数据速率。该TLK6002支持从原有速度到最新更快速度的升级,符合所有无线基站设计所需的 OBSAI 与 CPRI 标准要求。TLK6002 可用于各种无线基础设施应用,其中包括 WiMAX、TD-SCDMA、WCDMA 以及 CDMA2000 等。

双通道 0.47Gbps 至 6.25Gbps 多速率收发器TLK6002是多千兆位收发器产品组合的一员,旨在用于超高速双向点对点数据传输系统。它专门用于基站RRH(远程无线电头)应用,但也可用于其他高速应用。

最新 SerDes 使用统一 122.88 MHz 或 153.6 MHz 固定参考时钟频率,可支持通用公共无线电接口 (CPRI™) 与开放式基站架构发起组织 (OBSAI) 速率。此外,TLK6002 的 20 位并行单端接口还可便捷地连接至现场可编程门阵列 (FPGA)。与具有高速串行链路的 FPGA 相比,更经济的 FPGA 与 TLK6002 组合方案可显著降低系统成本。

TLK6002ZEU EDA模型免费下载:https://www.elecfans.com/p/e951433114

https://www.elecfans.com/p/e951433114

TLK6002ZEU 数据手册免费下载:

TLK6002 的主要特性与优势:

接收机均衡与收发器预加强功能可通过对线缆振幅损失与码间干扰 (ISI) 的补充来提高信号完整性,从而可支持超过 50 厘米的线迹范围;

集成型自动 CPRI/OBSAI 速率感测功能可自动调谐适应于系统设置,无需其它硬件或软件;

集成型高精度时延测量(6.144 Gbps 时为 0.6510 ns)功能可简化系统设计,为设计人员减少工作量;

支持 CPRI/OBSAI 数据速率:0.6144、0.768、1.2288、1.536、2.4576、3.072、4.9152 以及 6.144 Gbps;

TLK6002 可为众多 TI 数字信号处理器 (DSP)、数据转换器以及时钟产品提供补充。

TLK6002支持0.470 Gbps至6.25 Gbps的串行接口速度。速率支持包括使用单个固定参考时钟频率(122.88 MHz或153.6 MHz)的所有CPRI和OBSAI速率(0.6144 /0.768 /1.2288 /1.536 /2.4576 /3.072 /4.9152 /6.144 Gbps)。

TLK6002 20位并行接口采用1.5V或1.8V HSTL单端格式。 20位接口允许并行端的低速信号,因此可以在系统设计中使用低成本FPGA。并行接口可以编程为SDR(单数据速率)或DDR(双数据速率)模式。线路速率可以设置为满(≤6.25Gbps),半(≤3.75Gbps),四分之一(≤1.88Gbps)或第八(≤0.94Gbps)。可以使用器件输入或软件控制寄存器设置线速率。

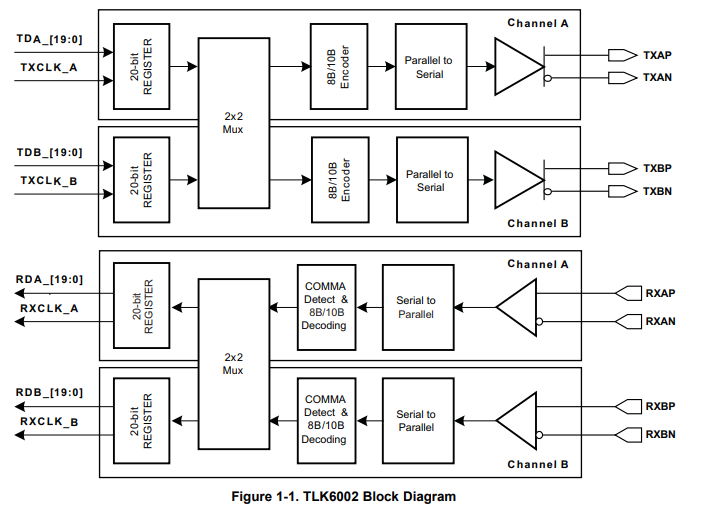

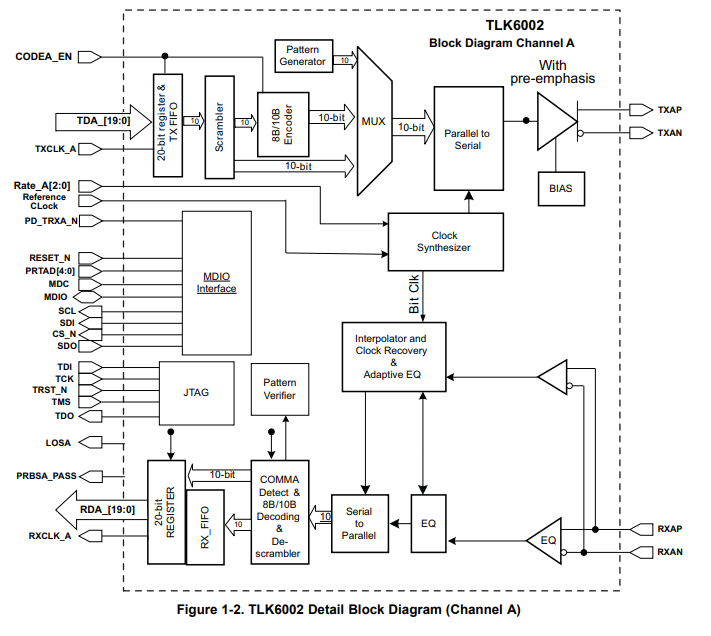

TLK6002作为物理层接口器件执行并行到串行,串行到并行和时钟提取的数据转换。串行收发器接口的最大串行数据速率为6.25 Gbps。

TLK6002在其并行发送和接收数据总线上接受单端HSTL信号。如果内部8B /10B编码和解码被使能,则TCL /B_ [19:0]被TXCLK_A /B锁存并发送到内部8b /10b编码器,其中产生的编码字被串行化并使用线路时钟差分传输以期望的线速率从SERDES参考时钟导出。如果禁用内部编码和解码,则TDA /B_ [19:0]被定义为20位数据被串行化并根据所需的线路速率进行未经修改的传输。

接收方向执行串行输入串行数据的并行转换,将得到的20位并行数据与恢复的字节时钟(RXCLK_A /B)同步。可选的解码接收数据可在RDA /B_ [19:0]输出信号上获得。

串行发送器和接收器使用带集成终端电阻的差分电流模式逻辑(CML)实现。

TLK6002提供两个本地(并行侧)和两个远程(串行侧)环回模式,用于自检和系统诊断。

TLK6002具有集成的信号丢失(LOS)检测功能功能,在串行输入信号没有足够电压幅度(≤75mV dfpp )的条件下置位。注意,当使能接收数据通路数据的信号丢失失败时(输入位6.6),输入信号必须≥150mV dfpp 。

特性总结:

双通道470Mbps至6.25Gbps连续/多速率收发器

支持所有CPRI和OBSAI数据速率

集成延迟测量功能,精度为±814 ps

CPRI /OBSAI自动速率感应(ARS)功能

支持SERDES操作,8B /10B数据模式(20-位和16位+控制器)

20位HSTL单端并行数据接口(集成源和

端接)

每个通道的共享或独立参考时钟< /li>

延迟/深度可配置发送和接收FIFO。

环回功能(串行和并行端),符合OBSAI

支持串行重新定时操作

支持PRBS(2 7 -1),(2 23 -1)和(2 31 -1)和

CRPAT Long /短期生成和验证

双电源:1.0V内核和1.5V /1.8VI /O标称电源

串行侧三分频发送去加重和接收自适应均衡离子

允许扩展背板延伸

串行输出上的可编程输出摆幅

最小接收器差分输入阈值为100mV dfpp

信号丢失(LOS)检测(≤75mV dfpp )

背板,铜缆或光模块的接口

热插拔保护< /li>

JTAG; IEEE 1149.1 /1149.6测试接口

MDIO; IEEE 802.3第22条支持

65nm高级CMOS技术

全速率工业环境工作温度(-40°C至85°C)

器件封装; 324 PBGA

应用程序

WI基础设施

CPRI和OBSAI链接

专有链接

背板

高速点对点传输系统

TLK6002ZEU 数据手册解析、电气规格汇总:

TLK6002文档主要内容提炼

1. 引言

- 产品概述:TLK6002是一款双通道多速率收发器,支持0.47Gbps至6.25Gbps的串行接口速度,专为超高速双向点对点数据传输系统设计。

- 应用领域:包括无线基础设施、CPRI和OBSAI链路、专有链路、背板以及高速点对点传输系统等。

2. 收发器特性

- 双通道支持:每个通道独立或共享参考时钟。

- 多速率支持:支持所有CPRI和OBSAI数据速率,通过单个固定参考时钟频率(122.88MHz或153.6MHz)实现。

- 接口模式:支持20位SDR/DDR并行接口模式,可选8b/10b编码/解码。

- 集成功能:包括延迟测量、可编程输出摆幅、CPRI/OBSAI自动速率感应(ARS)功能、PRBS生成和验证等。

3. 功能描述

- 数据转换:支持并行到串行、串行到并行的数据转换以及时钟提取。

- 串行接口:使用差分电流模式逻辑(CML),集成终端电阻,支持热插拔保护。

- 自动速率感应:ARS功能可自动检测并适应CPRI/OBSAI标准定义的串行链路速率。

- 延迟测量:集成延迟测量功能,测量精度±814ps。

- 电源管理:支持多种电源管理模式,包括引脚控制和MDIO接口控制。

4. 引脚描述

- 信号引脚:包括串行收发引脚(TXAP/N、RXAP/N等)、时钟引脚(REFCLK_0_P/N、REFCLK_1_P/N等)、控制引脚(RATE_A[2:0]、RATE_B[2:0]等)以及其他功能引脚。

- 电源引脚:提供多种电源电压选项,包括核心电压(DVDD)、模拟电压(AVDD)、高速模拟电路电压(VDDT)等。

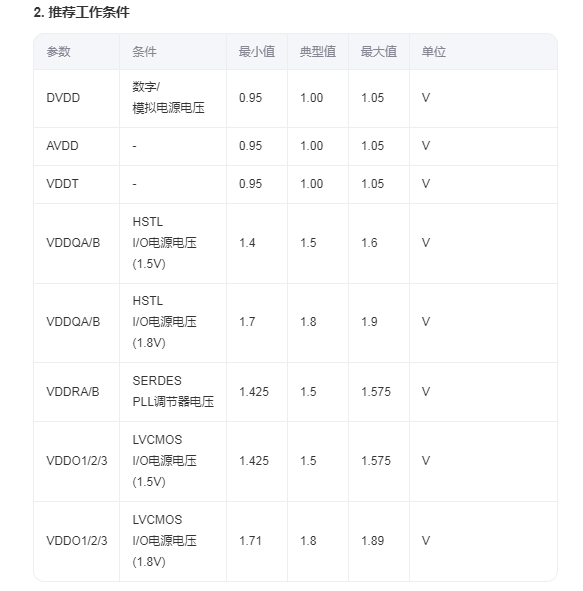

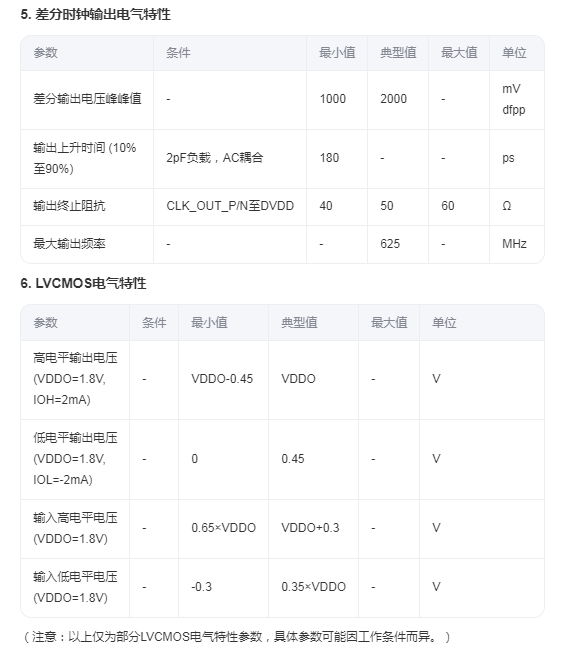

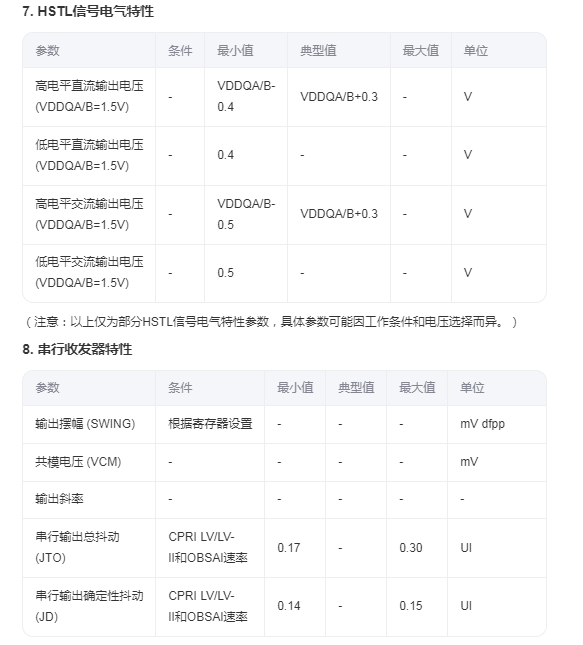

5. 电气规格

- 绝对最大额定值:规定了供电电压、输入电压、存储温度等参数的最大值。

- 推荐工作条件:详细列出了各电源电压、电流、温度等推荐工作范围。

- 参考时钟要求:规定了参考时钟的频率范围、相对精度、占空比等。

- 串行收发器特性:包括输出摆幅、共模电压、输出斜率、抖动容限等详细参数。

6. 应用指南

- 设备初始化:提供了详细的设备初始化步骤,包括引脚设置、设备复位、时钟配置、数据速率设置等。

- 测试模式:支持多种测试模式,包括CRPAT长/短模式、PRBS 27-1/223-1/231-1模式等,用于生成和验证测试图案。

- 功耗评估:提供了不同工作条件下的设备功耗评估数据。

7. 封装与尺寸

- 封装类型:采用324引脚BGA封装。

- 尺寸与标记:数据手册提供了封装尺寸、引脚间距、设备标记等详细信息。

8. 附件

- 连续速率设备配置:详细说明了如何根据串行速率和SERDES配置选择参考时钟。

- 8b/10b控制字符支持:列出了支持的8b/10b控制字符及其编码。

- 设备延迟规范:提供了设备在不同工作模式下的绝对延迟、静态延迟变化和动态延迟变化数据。

核心电气规格汇总如下:

一、电源规格

- 核心电压:

- 工作范围:0.95V - 1.05V(推荐1.0V)

- 最大耐受电压:1.1V45

- I/O电压:

- 支持双电压:1.5V 或 1.8V HSTL单端接口14

- 容差范围:±5%4

- 功耗:

- 最大电源电流:250mA(全速率工作)5

二、接口电气特性

- 串行收发器(CML差分接口) :

- 输出差分摆幅:800mVpp - 1600mVpp(可编程调节)45

- 接收灵敏度:最小100mVpp差分输入4

- 共模电压范围:0V - 1.2V4

- 并行接口(20位HSTL) :

- 逻辑高电平:0.8×VDDIO 1

- 逻辑低电平:0.2×VDDIO 1

三、时钟与信号完整性

- 参考时钟要求:

- 频率:122.88MHz 或 153.6MHz(固定)14

- 抖动容限:≤1ps RMS(12kHz-20MHz频带)4

- 占空比:45% - 55%4

- 抖动性能:

- 发送端抖动:≤0.15UI(峰峰值)4

- 接收端容限:支持>0.6UI抖动输入5

四、环境与可靠性

- 工作温度:

- 工业级:-40°C 至 +85°C57

- 保护功能:

- 热插拔保护(Hot Plug)4

- 信号丢失检测(LOS):阈值≤75mVpp差分4

五、物理封装

- 封装形式:324引脚BGA(19mm×19mm)67

- 焊盘设计:裸露焊盘增强散热

TLK6002ZEU EDA模型免费下载:https://www.elecfans.com/p/e951433114

https://www.elecfans.com/p/e951433114

-

TLK2501:一款高性能的1.5 - 2.5 Gbps收发器2025-12-31 463

-

深入剖析TLK6002:高性能多速率收发器的技术详解2025-12-28 645

-

深入解析TLK6002:高性能多速率收发器的技术洞察2025-12-24 307

-

TLK10081:10Gbps 1 - 8 通道多速率串行链路聚合器的深度解析2025-12-23 494

-

Texas Instruments DS90UB9702-Q1 FPD-Link解串器数据手册2025-08-03 1421

-

onsemi FIN3386MTDX LVDS串行解串器参数特性,数据手册与EDA模型下载2025-07-09 942

-

MAX9278/MAX9282用于同轴电缆或STP输入和LVDS输出的3.12Gbps GMSL解串器技术手册2025-05-28 1421

-

TLK10002 10Gbps双通道多速率收发器数据表2024-07-09 568

-

TLK2711-SP收发器2021-03-24 1079

-

TLK6002 2 通道 0.47Gbps 至 6.25Gbps 多速率收发器2018-10-16 302

-

探讨串行解串器的技术及其应用2018-09-13 2393

-

基于TLK10081的千兆以太网多速率链路聚合器参考设计包括原理图和BOM表2018-08-03 4551

-

双通道串行器-解串器TLK60022010-06-03 1981

全部0条评论

快来发表一下你的评论吧 !