用74ls151实现全加器设计电路

IC应用电路图

描述

根据全加器的定义可知:

输入为:A,B,Ci其中A,B为被加数和加数,Ci为低位进位数。

输出为:S,Co,其中S为本位和数,Co为高位进位数。

其逻辑关系为:

S=A⊕B⊕Ci

Co=AB+(A⊕B)Ci

计算后,结果用最小项表示为:

S=m1+m2+m4+m7

Co=m3+m5+m6+m7

查询74LS151和74LS138的真值表可知:

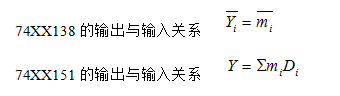

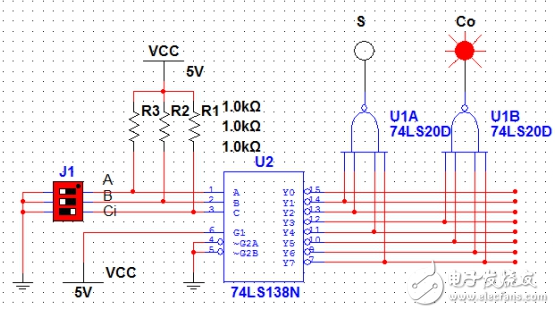

(一)74LS138

那么利用74LS138可以得到地址端A,B,Ci对应的所有最小项,然后用两个4输入与非门(74LS20)取得与上面计算得到的对应的最小项和,就能得到想要的结果。可以设计如图1所示电路:

图1

图中,三位拨码开关分别代表A,B和Ci。S和Co是两个灯,代表S和Co的状态,为“1”

时亮,为“0”时不亮。

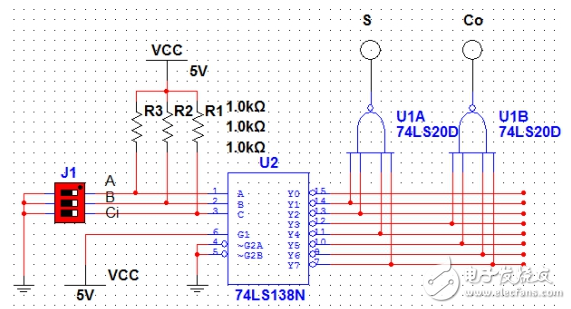

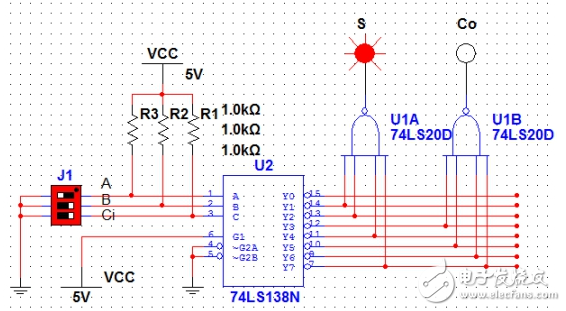

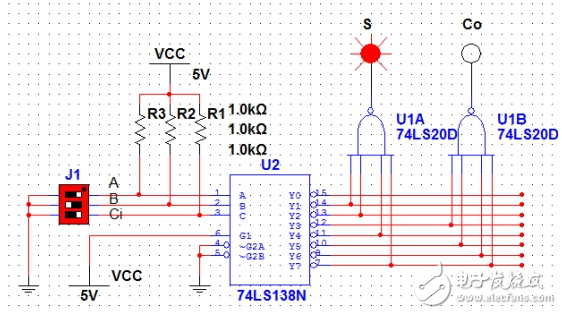

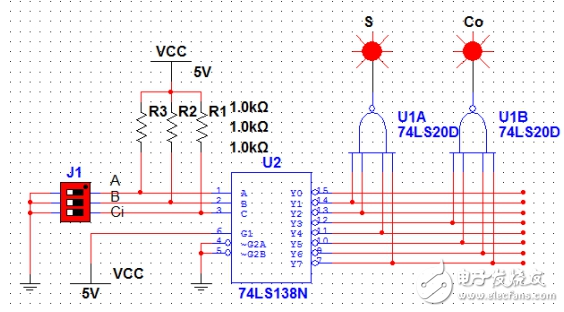

下面给出{A=1,B=0,Ci=0};{A=0,B=1,Ci=0};{A=1,B=1,Ci=0}和{A=1,B=1,Ci=1}四种输入状态下的S和Co状态。

图2(A=1,B=0,Ci=0)

图3(A=0,B=1,Ci=0)

图4(A=1,B=1,Ci=0)

图5(A=1,B=1,Ci=1)

可以看出电路的逻辑关系是正确的。

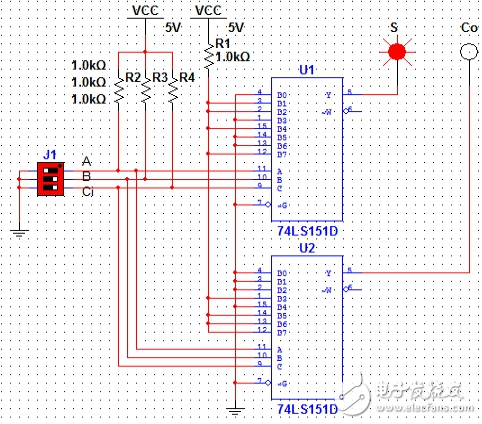

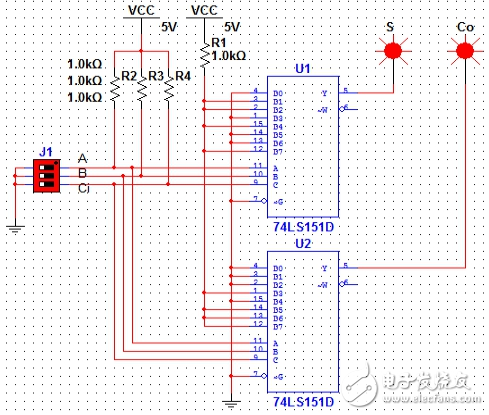

(2)74LS151

利用74LS151数据选择器可以设计如图6所示电路:

两个74LS151分别得到S和Co;其中U1的数据端配置为D1=D2=D4=D7=1,其余为0;

U2配置为D3=D5=D6=D7=1,其余为0.

图6

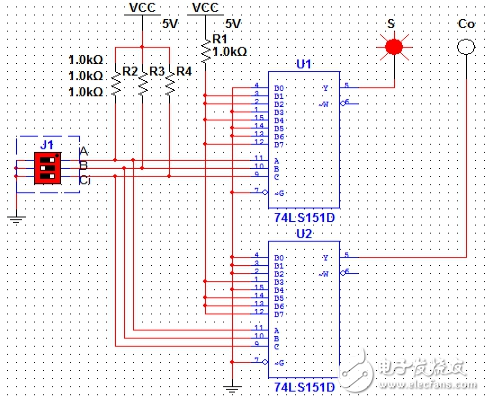

同样,下面也给出{A=1,B=0,Ci=0};{A=0,B=1,Ci=0};{A=1,B=1,Ci=0}和{A=1,B=1,Ci=1}四种输入状态下的S和Co状态。

图7(A=1,B=0,Ci=0)

图8(A=0,B=1,Ci=0)

图9(A=1,B=1,Ci=0)

图10(A=1,B=1,Ci=1)

可以看出,电路的逻辑关系也是正确的。

-

简单的lm339和74ls151的组合电路,lm339和74ls151接合起来后,功耗电流变得很大是为什么?2024-08-15 1438

-

74ls151引脚图及功能表2021-06-25 165749

-

74LS151数据选择器/多路复用器数据手册2021-05-31 5269

-

一个简单的lm339和74ls151的组合电路,lm339和74ls151接合起来后,功耗电流变得很大,这是为什么?2019-01-25 6345

-

74ls151中文资料汇总(74ls151引脚图及功能_工作原理及应用电路)2018-05-07 565769

-

74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)2018-05-04 122393

-

74ls151实现三人表决器2018-02-08 214707

-

74LS153实现三人表决电路(4种方式实现3人表决电路)2018-01-26 399425

-

求proteus有74ls151的元件库2017-12-04 12331

-

用74ls138设计全加器2017-10-31 155907

-

74LS151英文手册2016-11-22 1412

-

74LS151 英版数据手册2016-08-29 1868

-

74LS151/54LS151 pdf datasheet2008-08-06 3098

-

74ls151管脚图引脚图 真值表2007-11-29 97949

全部0条评论

快来发表一下你的评论吧 !