TI DRA71x汽车信息娱乐系统参考设计TIDEP-0097

汽车电子

描述

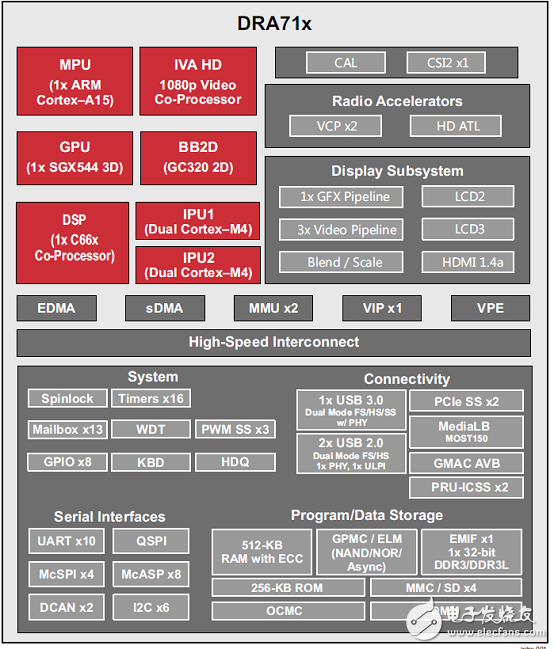

TI公司的DRA71x系列是600 MHz ARM Cortex-A15 SoC处理器,其架构提供汽车应用时的高性能并行处理特性,包括图像,语音,HMI,多媒体和智能手机投影模式功能,采用28-nm CMOS技术,支持全高清(HD)视频(1920×1080p, 60 fps),多视频输入和视频输出以及2D和3D图像,主要用在人机接口(HMI),导航,数字和模拟无线电,多媒体播放器,汽车显示音频系统,入门级导航和多媒体系统以及汽车数字仪表盘系统.本文介绍了DRA71x系列主要特性,框图以及汽车信息娱乐系统参考设计TIDEP-0097主要特性和系统指标,框图,电路图和材料清单.

The DRA71x processor is offered in a 538-ball, 17×17-mm, 0.65-mm ball pitch (0.8mm spacing rules canbe used on signals) with Via Channel™ Array (VCA) technology, ball grid array (BGA) package.

The architecture is designed to deliver high-performance concurrencies for automotive applications in acost-effective solution, providing full scalability from the DRA75x (“Jacinto 6 EP ” and “ Jacinto 6 Ex”),DRA74x “Jacinto 6” and DRA72x “Jacinto 6 Eco” family of infotainment processors, including graphics,voice, HMI, multimedia and smartphone projection mode capabilities.

Programmability is provided by a single-core ARM Cortex-A15 RISC CPU with Neon™ extensions and aTI C66x VLIW floating-point DSP core. The ARM processor lets developers keep control functionsseparate from other algorithms programmed on the DSP and coprocessors, thus reducing the complexityof the system software.

Additionally, TI provides a complete set of development tools for the ARM, and DSP, including C compilers and a debugging interface for visibility into source code execution.The DRA71x Jacinto 6 Entry processor family is qualified according to the AEC-Q100 standard.

The device features a simplified power supply rail mapping which enables lower cost PMIC solutions.

DRA71x系列主要特性:

• Architecture Designed for InfotainmentApplications

• Video, Image, and Graphics Processing Support

– Full-HD Video (1920 × 1080p, 60 fps)

– Multiple Video Input and Video Output

– 2D and 3D Graphics

• ARM® Cortex®-A15 Microprocessor Subsystem

• C66x Floating-Point VLIW DSP

– Fully Object-Code Compatible With C67x andC64x+

– Up to Thirty-two 16 × 16-Bit Fixed-PointMultiplies per Cycle

• Up to 512KB of On-Chip L3 RAM

• Level 3 (L3) and Level 4 (L4) Interconnects

• DDR3/DDR3L Memory Interface (EMIF) Module

– Supports up to DDR-1333 (667 MHz)

– Up to 2GB Across Single Chip Select

• Dual ARM® Cortex®-M4 Image Processing Units(IPU)

• IVA-HD Subsystem

• Display Subsystem

– Display Controller With DMA Engine and up toThree Pipelines

– HDMI™ Encoder: HDMI 1.4a and DVI 1.0Compliant

• 2D-Graphics Accelerator (BB2D) Subsystem

– Vivante™ GC320 Core

• Video Processing Engine (VPE)

• Single-Core PowerVR® SGX544 3D GPU

• One Video Input Port (VIP) Module

– Support for up to Four Multiplexed Input Ports

• General-Purpose Memory Controller (GPMC)

• Enhanced Direct Memory Access (EDMA)Controller

• 2-Port Gigabit Ethernet (GMAC)

– Up to Two External Ports

• Sixteen 32-Bit General-Purpose Timers

• 32-Bit MPU Watchdog Timer

• Six High-Speed Inter-Integrated Circuit (I2C) Ports

• HDQ™/1-Wire® Interface

• Ten Configurable UART/IrDA/CIR Modules

• Four Multichannel Serial Peripheral Interfaces(McSPI)

• Quad SPI Interface (QSPI)

• Media Local Bus Subsystem (MLBSS)

• Eight Multichannel Audio Serial Port (McASP)Modules

• SuperSpeed USB 3.0 Dual-Role Device

• High-Speed USB 2.0 Dual-Role Device

• High-Speed USB 2.0 On-The-Go

• Four MultiMedia Card/Secure Digital/Secure DigitalInput Output Interfaces (MMC/SD/SDIO)

• PCI Express® 3.0 Subsystems With Two 5-GbpsLanes

– One 2-lane Gen2-Compliant Port

– or Two 1-lane Gen2-Compliant Ports

• Dual Controller Area Network (DCAN) Modules

– CAN 2.0B Protocol

• MIPI® CSI-2 Camera Serial Interface

• Up to 186 General-Purpose I/O (GPIO) Pins

• Power, Reset, and Clock Management

• On-Chip Debug With CTools Technology

• 28-nm CMOS Technology

• 17 mm × 17 mm, 0.65-mm Pitch, 538-Pin BGA(CBD)

DRA71x系列应用:

• Human-Machine Interface (HMI)

• Navigation

• Digital and Analog Radio

• Multimedia Playback

• Automotive Display Audio Systems

• Automotive Entry Navigation and MultimediaSystems

• Automotive Digital Cluster Systems

图1.DRA71x系列框图

汽车信息娱乐系统参考设计TIDEP-0097

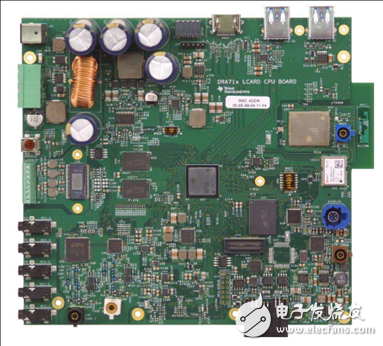

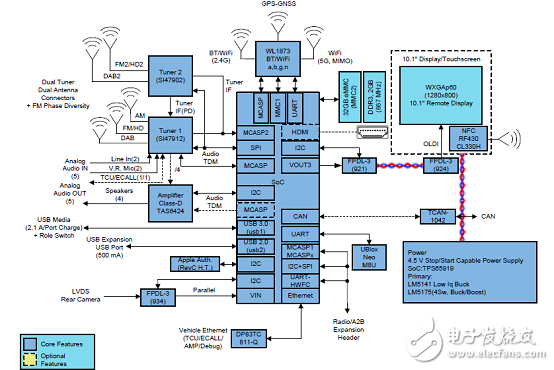

This automotive reference design is based on TI’sJacinto™ DRA71x processor and focuses on systemlevel cost savings.The six-layer design reduces PCBcosts through optimized via breakout scheme andpower distribution network as well as integration of keyfeatures. Functionality can be added or removedbased on the end product requirements. This designtargets applications such as infotainment andreconfigurable digital cluster. The design has a 12-Vinput with a single PMIC. The design supports HDMI,USB3.0 or USB2.0, TAS6424 digital Class-D amplifier,FPD-Link interface, and many other features. ALinux®, Android™, or QNX based softwaredevelopment kit (SDK) is included.

This reference design is a system that includes the DRA 71x automotive applications processor, a powersolution, DRAM(DDR3L), and multiple interface ports an expansion connectors. This system is designedon a six-layer PCB using a unique via breakout scheme, a single PMIC solution, and fewer but integratedfunctions that allows for lower manufacturing costs without sacrificing quality of the end product. Thereference design targets entry level infotainment applications with a high-end look and feel. An HDMI andFPD-Link III port allows for the connection of a high-definition display and rear view camera to provide arich user interface. A Bluetooth ® and Wi-Fi® module, audio and tuner inputs, and USB port are included toallow for connectivity of wireless and wired audio devices for rich output from the Class-D audio amplifier.The optimized power solution allows the design to be powered from a single 12-V power source.

参考设计TIDEP-0097主要特性:

• TI Jacinto DRA71x Processor With IntegratedFeatures Help Design Cost-Effective, Feature Rich,Entry Level (Display Audio) Infotainment andCluster Systems

• DRA71x Superset Processor With 2D and 3Dgraphics, C66x DSP, and Cortex®-M4 options

• Processor SDK for Linux, Android, and QNXDevelopment With Add-on Packages for Radio andAudio

• Cost Saving Features Include Six-Layer HWDesign, Rear View Camera (RVC) Support, TunerIntegration with Software Defined Radio(SDR),Class-D Amplifier and Multi-Sone Audio Support

• Includes TI ’ s Solution and Support for Power,Audio, Processing, and Display

参考设计TIDEP-0097应用:

• Entry Level In Vehicle Infotainment (IVI) Head Unit

• Digital Cluster

• Radio and Audio Co-processor

• Automotive Amplifier

图2.参考设计TIDEP-0097外形图

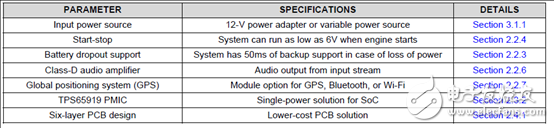

参考设计TIDEP-0097主要系统指标:

图3.参考设计TIDEP-0097框图

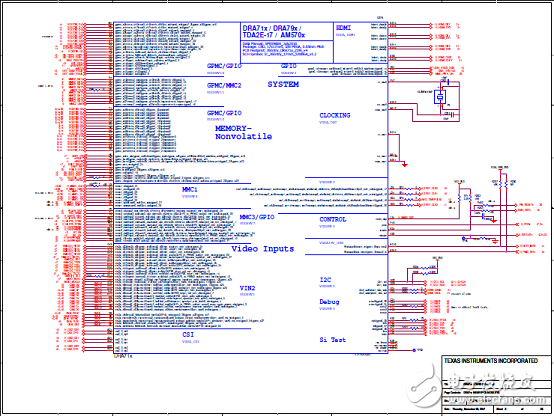

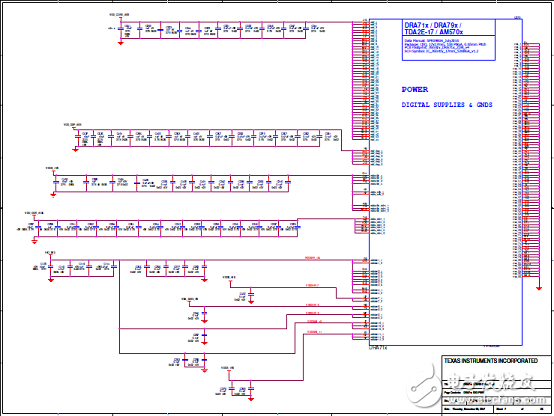

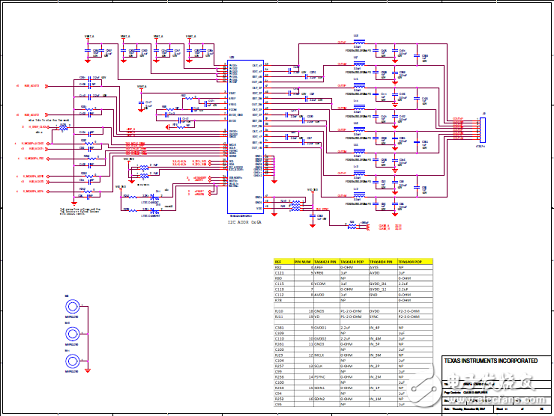

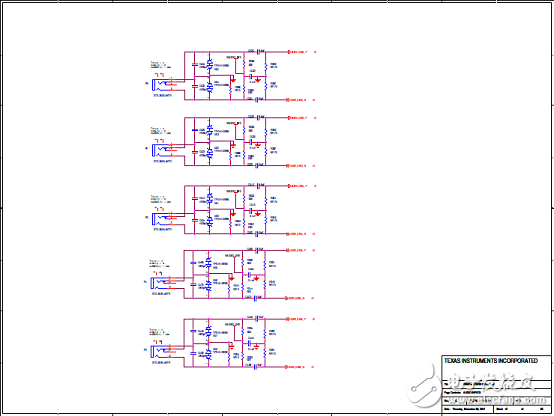

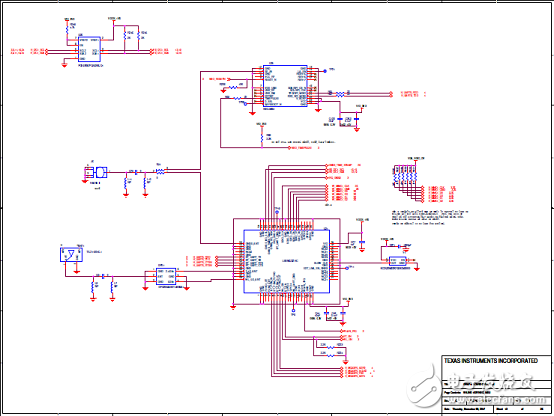

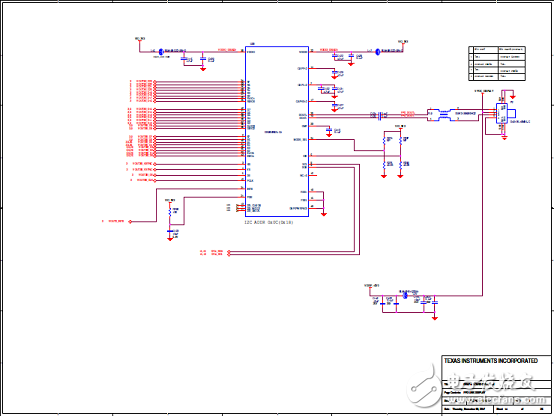

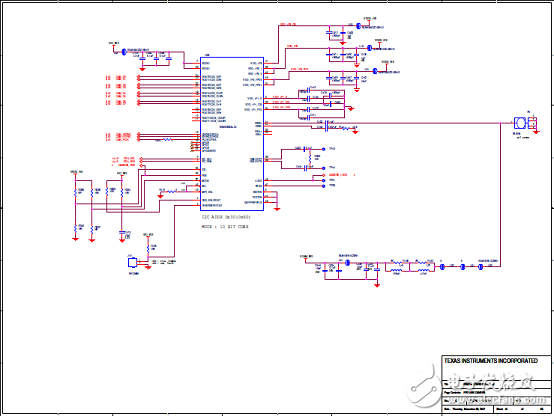

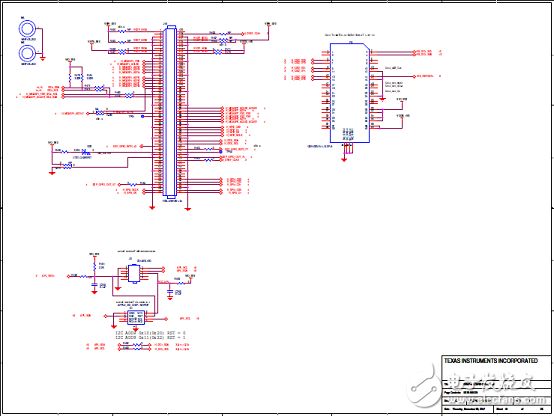

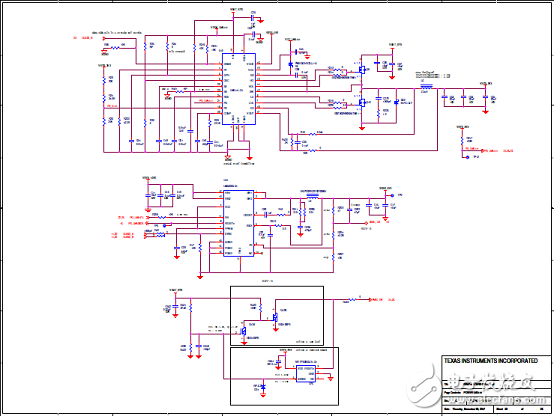

图4.参考设计TIDEP-0097电路图(1)

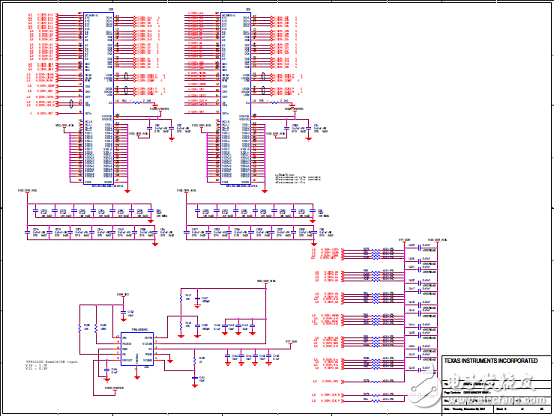

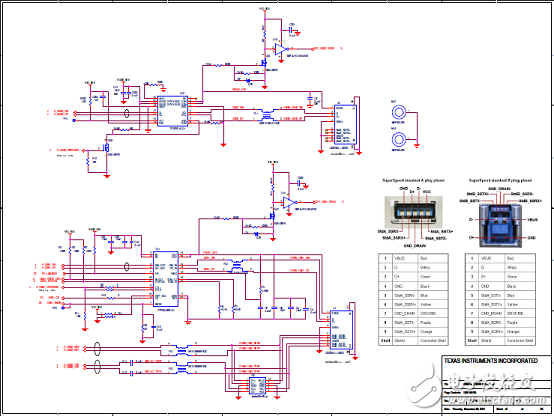

图5.参考设计TIDEP-0097电路图(2)

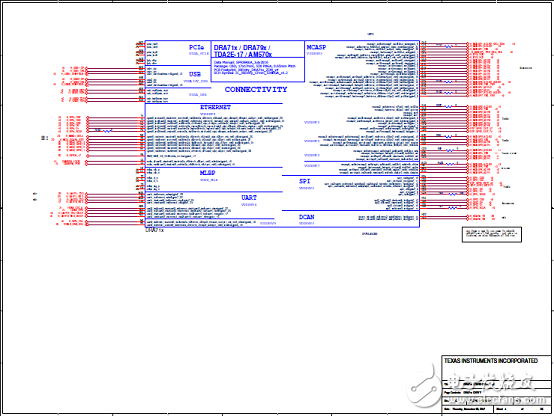

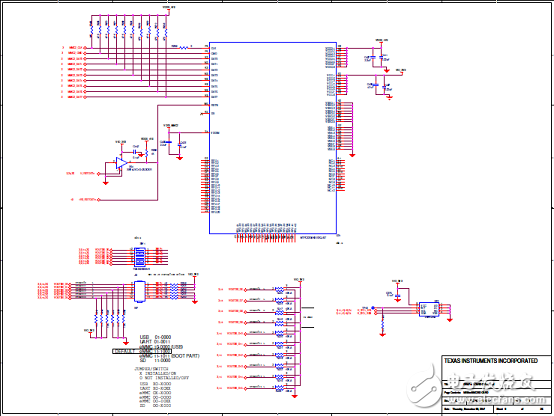

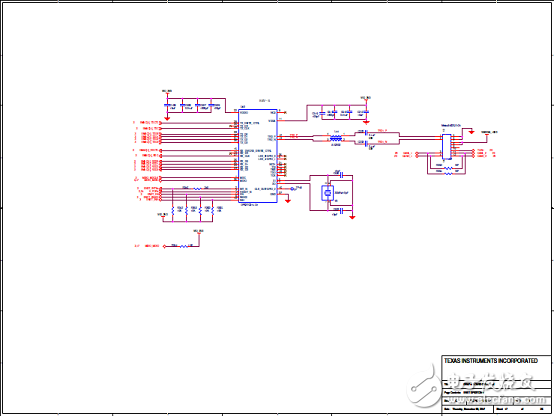

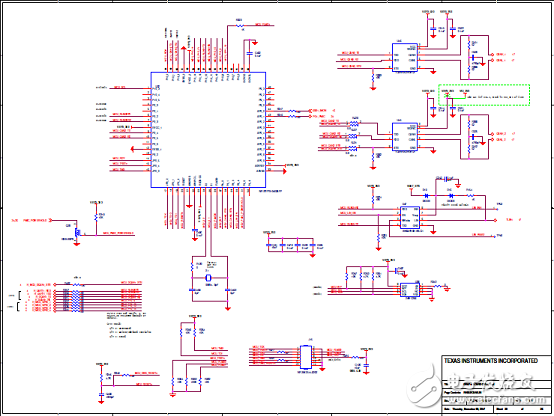

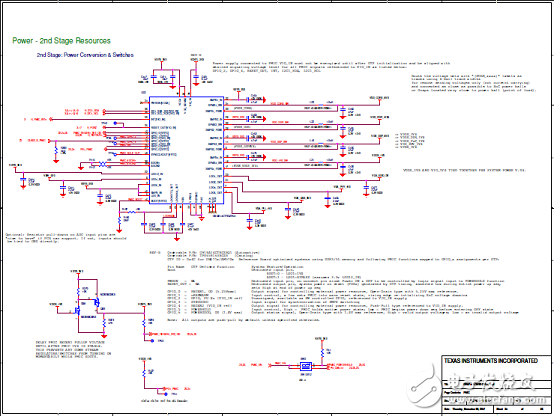

图6.参考设计TIDEP-0097电路图(3)

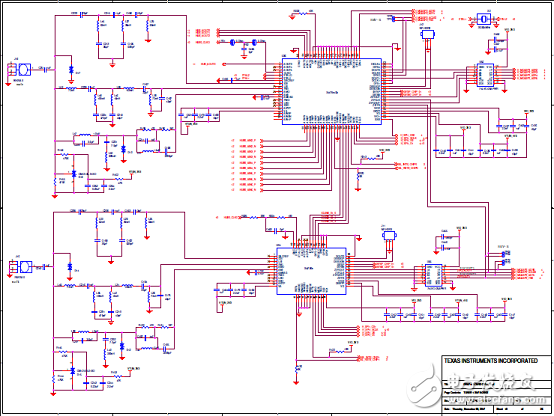

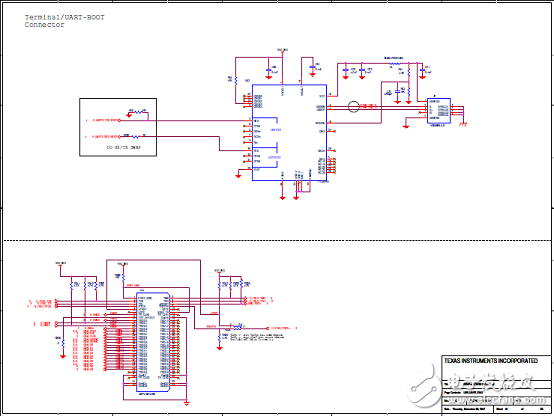

图7.参考设计TIDEP-0097电路图(4)

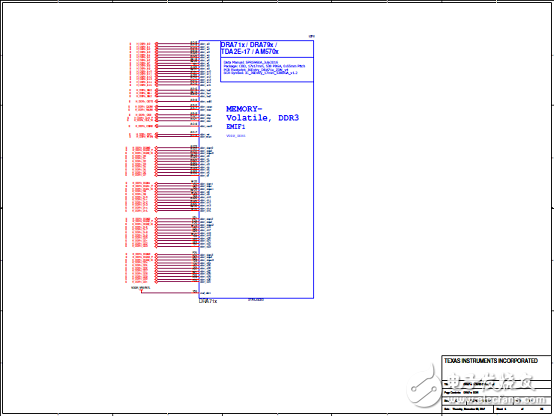

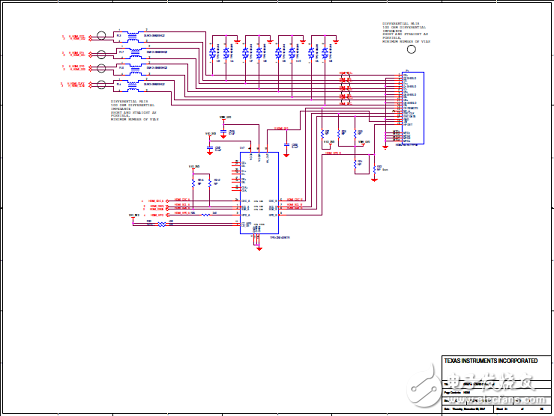

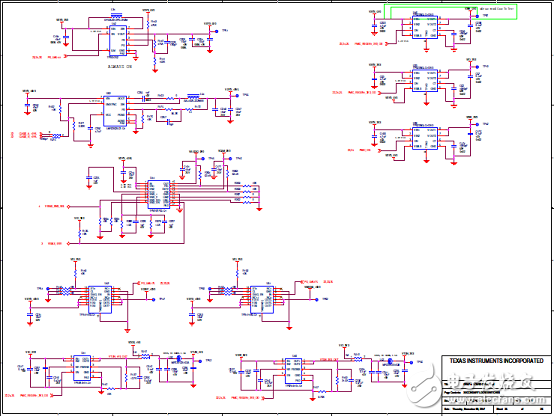

图8.参考设计TIDEP-0097电路图(5)

图9.参考设计TIDEP-0097电路图(6)

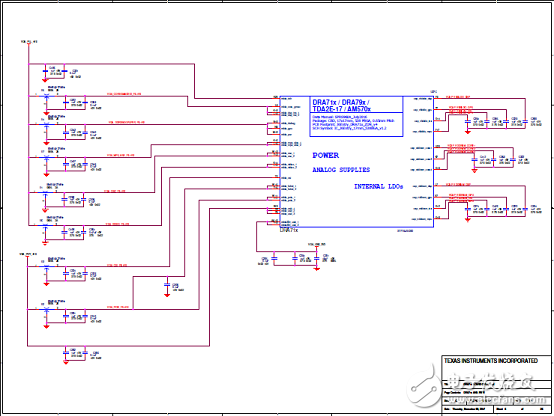

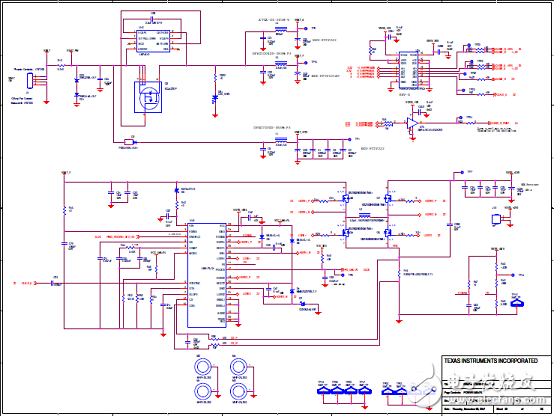

图10.参考设计TIDEP-0097电路图(7)

图11.参考设计TIDEP-0097电路图(8)

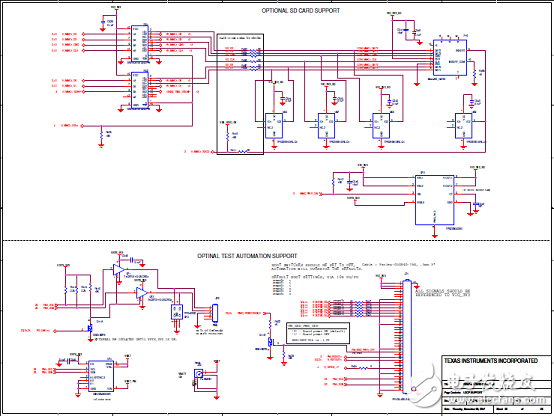

图12.参考设计TIDEP-0097电路图(9)

图13.参考设计TIDEP-0097电路图(10)

图14.参考设计TIDEP-0097电路图(11)

图15.参考设计TIDEP-0097电路图(12)

图16.参考设计TIDEP-0097电路图(13)

图17.参考设计TIDEP-0097电路图(14)

图18.参考设计TIDEP-0097电路图(15)

图19.参考设计TIDEP-0097电路图(16)

图20.参考设计TIDEP-0097电路图(17)

图21.参考设计TIDEP-0097电路图(18)

图22.参考设计TIDEP-0097电路图(19)

图23.参考设计TIDEP-0097电路图(20)

图24.参考设计TIDEP-0097电路图(21)

图25.参考设计TIDEP-0097电路图(22)

图26.参考设计TIDEP-0097电路图(23)

图27.参考设计TIDEP-0097电路图(24)

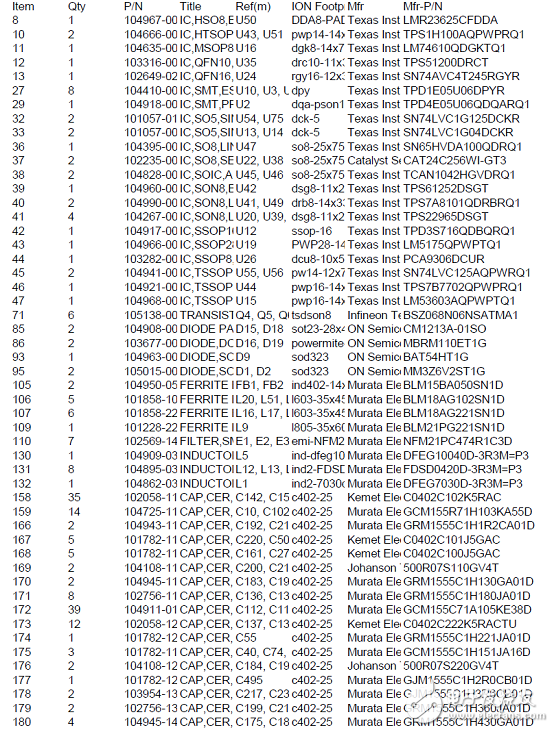

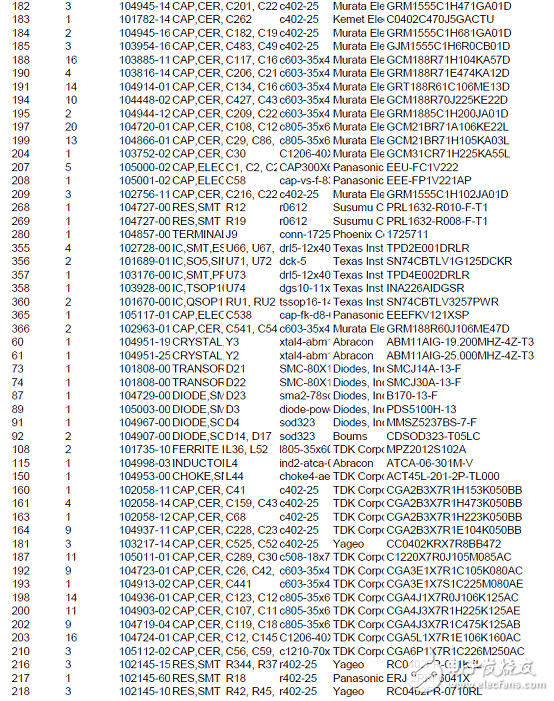

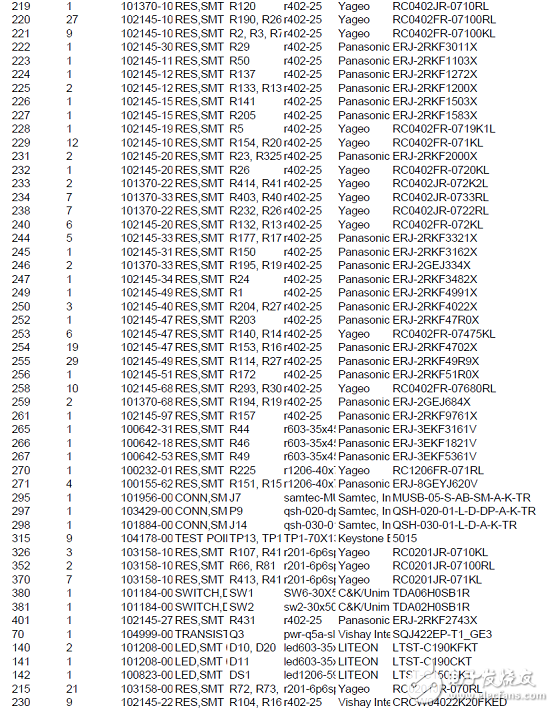

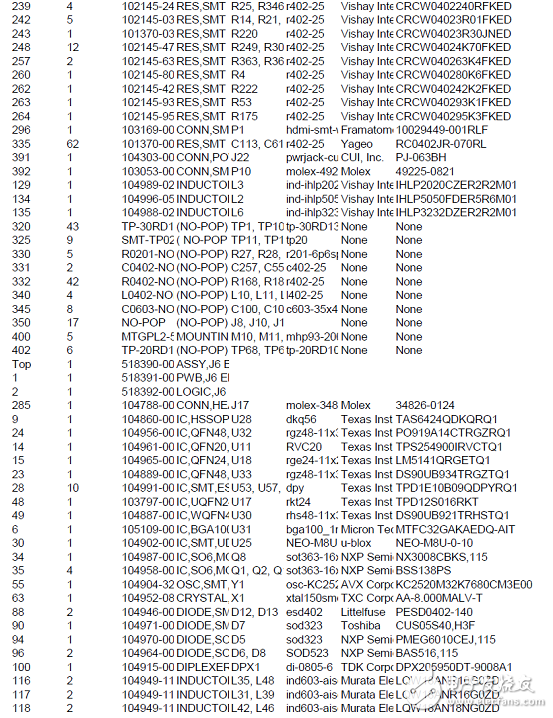

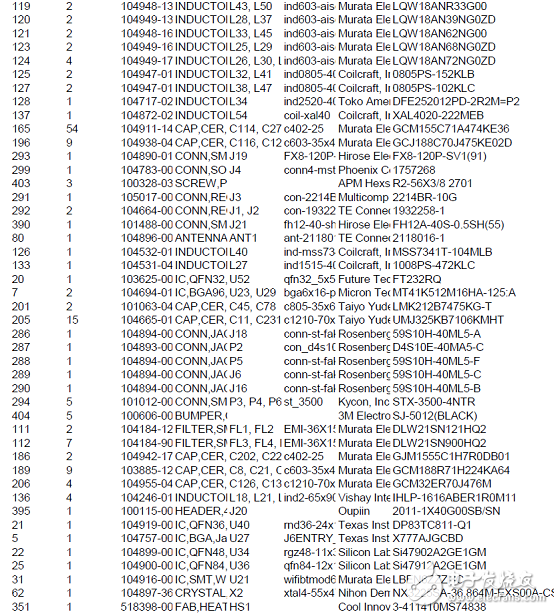

参考设计TIDEP-0097材料清单:

- 相关推荐

- t

-

TI“Jacinto 6 Eco”DRA72x 处理器让车载信息娱乐和车联网功能更加丰富2018-09-14 0

-

QNX软件系统与TI助力汽车信息娱乐系统发展2018-09-20 0

-

无法识别我参与的汽车信息娱乐系统2019-07-26 0

-

电源管理解决方案改善汽车信息娱乐系统设计2019-08-15 0

-

如何推动汽车信息娱乐系统发展2022-11-23 0

-

德州仪器(TI)推出互连汽车信息娱乐系统解决方案2012-01-13 1089

-

汽车信息娱乐和通信系统解决方案2016-01-06 526

-

利用TI全新可扩展汽车信息娱乐解决方案节省开发时间和成本2016-03-08 642

-

TI DRA72x处理器为汽车带来丰富的车载信息娱乐和车联网功能2021-11-10 937

-

汽车信息娱乐电源系统参考设计2022-09-06 403

-

TI携手QNX推动汽车信息娱乐系统发展2022-11-07 556

-

DRA71x信息娱乐应用处理器数据表2024-08-09 149

-

汽车信息娱乐系统的ESD保护2024-09-25 176

-

为DRA71x、DRA79x和TDA2E-17供电的LP8733-Q1和LP8732-Q1用户指南2025-01-03 128

全部0条评论

快来发表一下你的评论吧 !