一文看懂74ls165级联测试程序与proteus仿真电路图

IC应用电路图

描述

74LS165功能简介

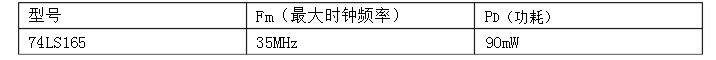

主要电特性如下:

工作原理:

当移位\植入控制端(SH/LD)为低电平时,并行数据(A-H)被置入寄存器,而时钟(CLK,CLKINH)及串行数据(SER)均无关。当SH/LD)为高电平时,并行置数功能被禁止。CLK和CLKINK在功能上是等价的,可以交换使用。当CLK和CLKINK有一个为低电平并且SH/LD为高电平时,另一个时钟可以输入。当CLR和CLKINK有一个为高电平时,另一个时钟被禁止。只有在CLK为高电平时CLKINK才可变为高电平。

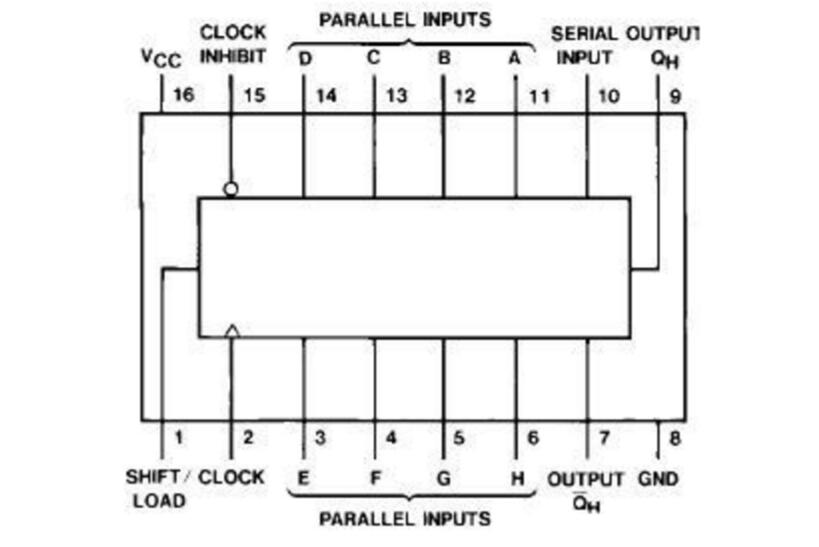

引出端符号

CLK; CLK INK 时钟输入端(上升沿有效)

A-H 并行数据输入端

SER 串行数据输入端

QH 输出端

QH“ 互补输出端

Sh/LD”移位控制/置入控制(低电平有效)

逻辑图

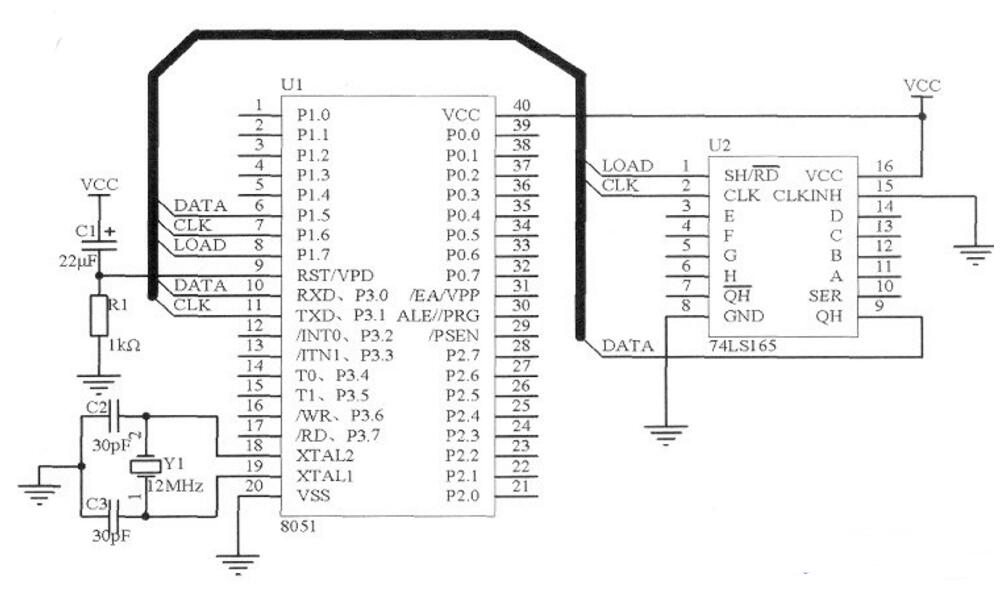

单片机I/O端口驱动74LS165电路

用I/O模拟移位寄存器的时序驱动74LS165,实现并行数据的输入。如下图所示,P1.5被用于串行数据输入,P1.6用于移位时钟输出,P1.7用来控制74LS165的工作状态。

单片机I/O端口驱动74LS165主要包括函数声明管脚定义部分、数据输入函数以及数据输出函数。

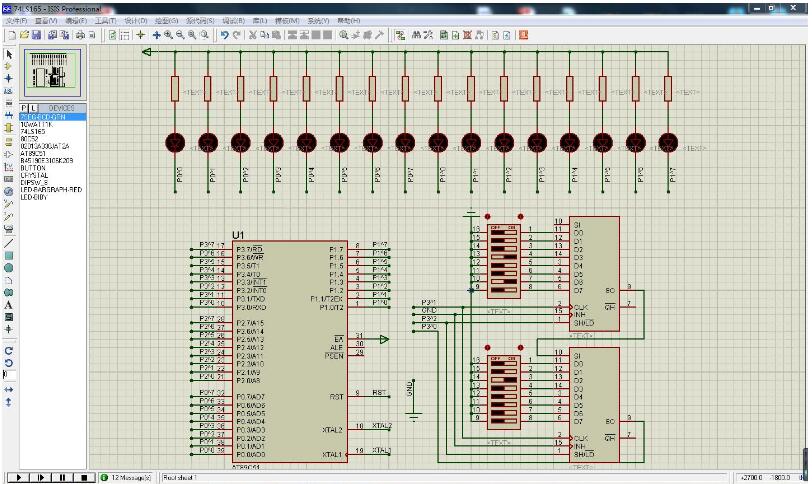

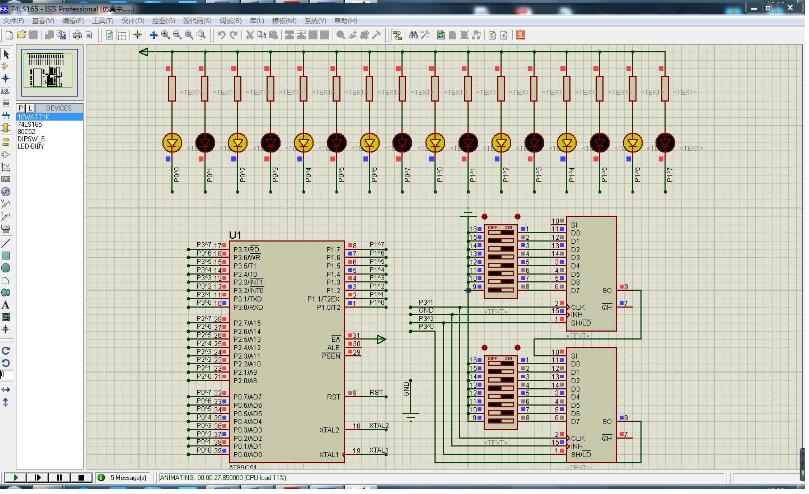

74ls165级联测试程序与proteus仿真电路图

关于如何做74ls165级联测试程序与proteus仿真电路图,内容请看下文:

下面是proteus仿真原理图:

单片机c语言源程序:

/****************************************Copyright (c)**************************************************

**

** -----------------------------------------------------------------------------------------------------

** File Name : 74LS165.C

** Version : V1.0.0

** Description :

* 【外部晶振】: 11.0592mhz

* 【主控芯片】: STC89C52

* 【编译环境】: Keil μVisio4

* 【程序功能】:

* 【使用说明】:

** -----------------------------------------------------------------------------------------------------

** Author : Creavalia

** Date : 2015年10月19日

** -----------------------------------------------------------------------------------------------------

** Modify Person:

** Modify Date :

** Description :

*********************************************************************************************************/

// Includes --------------------------------------------------------------------------------------------

#include《reg51.h》

#include《intrins.h》

/********************************************************************************************************

** Marcos define

*********************************************************************************************************/

#define uint unsigned int

#define uchar unsigned char

//IO设置

sbit QH = P3^0; //输出端

sbit CLK = P3^1; //时钟输入端(上升沿有效)

sbit SPL = P3^2; //移位控制/置入控制(低电平有效)

/********************************************************************************************************

* Function Name : read_int165

* Description : 接收数据

* Input : None

* Output : None

* Return : None

********************************************************************************************************/

uint read_int165(void)

{

uchar i = 0;

uint read_data = 0;

SPL = 0; //置数,读入并行输入口数据

_nop_();

SPL = 1; //移位,并口输入被封锁,串行转换开始

_nop_();

for(i=0;i《16;i++) //16位数据

{

read_data 《《= 1;

if(QH)

{

read_data|=QH;

}

CLK=0; //下降沿

_nop_();

CLK=1; //上升沿

_nop_();

}

return read_data;

}

/********************************************************************************************************

* Function Name : main

* Description : 主函数

* Input : None

* Output : None

* Return : None

********************************************************************************************************/

void main()

{

//初始化

uint temp = 0;

uchar tempH = 0;

uchar tempL = 0;

CLK=0;

while(1)

{

temp = read_int165();

//获取高8位,存放置tempH

tempH = (uchar) (temp》》8);

//获取低8位,存放置tempL

tempL = (uchar) temp;

P0=tempH; //接收到的字节显示在P0 端口,显示的值与拨码开关对应

P1=tempL; //接收到的字节显示在P1 端口,显示的值与拨码开关对应

}

}

/*********************************************************************************************************

** End Of File

********************************************************************************************************/

74ls165相关文章:

74ls165中文资料汇总(74ls165引脚图及功能_工作原理及应用电路)

74ls165相关下载:

-

如何对74HC165的代码Proteus仿真2021-09-29 1965

-

使用单片机和74LS595和74LS165扩展实现8乘8键盘的仿真文件免费下载2021-03-22 1499

-

请问如何使用74LS165将AVR的串口输入扩为并口输入?2020-11-17 1519

-

基于74LS165芯片的串行口方式仿真电路图2020-10-07 5225

-

74ls595级联电路及驱动程序分享2018-05-28 11713

-

74ls165中文资料汇总(74ls165引脚图及功能_工作原理及应用电路)2018-05-08 79114

-

怎么样用单片机的串口驱动74LS1652018-03-07 7697

-

74hc165级联用法(74hc165级联电路图及程序)2018-02-02 56688

-

74LS165英文手册2016-11-21 753

-

芯片74LS165资料2015-12-31 905

-

如何两片74ls151级联的竞争冒险?2015-03-09 3185

-

74LS165如何接可以实现并串转换?2015-03-06 4141

-

AT89C51串口方式0外接74LS165时,读取数据有偏差2012-04-02 6327

-

74ls165引脚图,74ls165参数资料2008-09-06 11692

全部0条评论

快来发表一下你的评论吧 !