74ls160应用电路图大全(数字钟\TLC320AD75C\交通灯\LM324)

IC应用电路图

描述

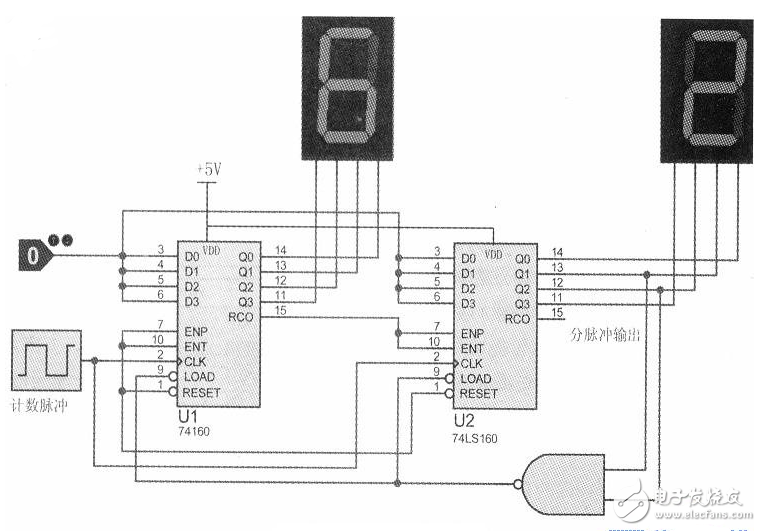

74ls160应用电路图(一)

数字钟是计数电路的一种典型应用,其构成原理框图如下图所示。它主要由三部分组成:

(1)秒脉冲发生电路

它由32768Hz的石英晶体振荡器和若干级分频电路构成,振荡器产生32768Hz的方波,由于使用了晶体,振荡频率准确且稳定,经过216=65536分频后,再经过2倍频,得到秒脉冲信号,该秒脉冲信号经过控制门进入秒计数器进行计数。

(2)时间校准电路

时间调整由3个开关AN1、AN2、AN3以及3个R-S触发器构成。当3个开关都拨到右边时,R-S触发器的输出Q1、Q2、Q3都为1,因此控制门的3个右边门开启,秒、分、时脉冲可以正常进入相应计数器进行计数。当某开关拨到左边时,R-S触发器翻转,例如当“秒调整”开关拨到左边,Q1-0、,控制门的右门关、左门开,秒脉冲不能通过,而0.5s的脉冲信号却可以进入秒计数器实现“秒调整”。分、时的调校原理与此相同,使用R—S触发器的目的是为了消除开关抖动产生的影响。

(3)时、分、秒计数电路

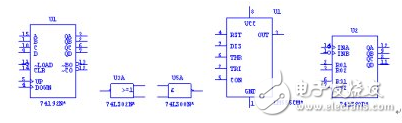

采用两片74LS160按下图所示连接,可以构成作60分频计数,用于数字钟中的秒计数器。

标准秒脉冲经过控制门进入秒计数器,并显示其计数值,当计数满60时得到一个进位“分”脉冲,同时秒计数器自动清零。“分”脉冲经控制门送入“分计数器”又作60分频计数,当计数满后得到进位“时”脉冲。“时”脉冲再经控制门送入“时计数器”计数。“分计数器”与“时计数器”的计数、复零和显示原理与“秒计数器”相同,可以自行设计。

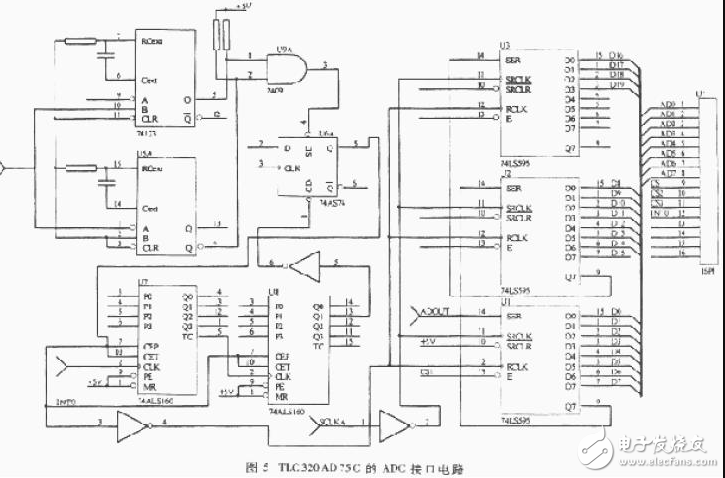

74ls160应用电路图(二)

下图是TLC320AD75C 的ADC 与MCS51 接口电路,DAC 接口电路是上述电路的逆过程,只要将8位输出锁存移位寄存器(三态、串入并出)74LS595 改成8位输入锁存移位寄存器74LS597(三态、并入串出)即可,此处不再详述。图5与图3的画法一样,鉴于篇幅的限制,省略掉了一些电路细节,读者应用本文中的电路时应补上。下面简单讲述一下图5所示电路的工作过程。根据图4串行接口时序,要求利用LRCKA 和SCLKA 生成图4(d)所示的脉冲。在该脉冲的高电平期间20 位串行数据送到由三片74LS595 级联而成的串入并出接口电路中;在脉冲的下降沿将74LS595 中移位寄存器中的数据传输到锁存器;在脉冲的低电平期间发中断到MCS51 的INTO,MCS51 依次发出三个片选信号,读走该20 位数据,从而完成一个声道的采集工作。因此如何产生图4(d)所示的脉冲是本电路的核心问题。在图5所示电路中,74LS123 捕捉到的LRCKA 上升沿和下降沿通过线与的方式生成图4(e)形式的极窄脉冲。在该脉冲的低电平期间置位74LS74;两片74LS160 接成20 进制的计数器,在74LS74 输出高电平到来时对SCLKA 进行计数,当计满20 个脉冲时输出一高电平脉冲,该脉冲经一非门倒相去74LS74 的复位端。74LS74 在上述的置位与复位作用下即产生图4(f)所示的脉冲,同时在该脉冲的低电平期间还要去清除计数器,停止计数器工作,直至该脉冲的下一个高电平到来。要指出的是图4(f)所示脉冲比图4(d)所示的脉冲有一延迟,但只要该延迟时间小于TSCLKA/2,即图4(f)所示脉冲的上升沿比转换开始后SCLKA 的第一个上升沿早,同步计数器就可正确计数,不会漏掉1位串行数据。

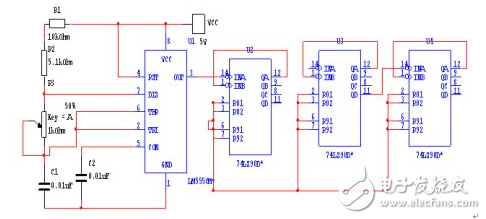

74ls160应用电路图(三)

设计原理和工作电路

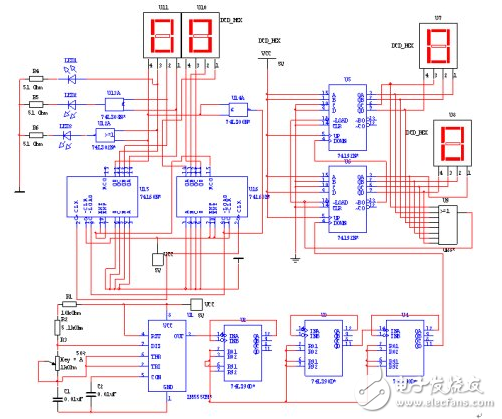

交通灯的控制电路主要由555定时器、分频电路产生出1HZ的脉冲,两个74LS160、与门、与非门、或非门组成的红绿灯转换电路,以及由74LS192设计出的倒计时显示器等组成。

秒脉冲的产生

电路图如下:

本电路由555定时器产生1KHZ的脉冲,再由分频电路产生出1HZ脉冲。

红绿灯的转换

电路图如下:

本电路是由两个74LS160组成的80进制计数器,每到第40个脉冲时转换红绿灯,在每次红绿灯转换的最后10秒,黄灯也一起亮,达到提示的作用。

倒计时显示

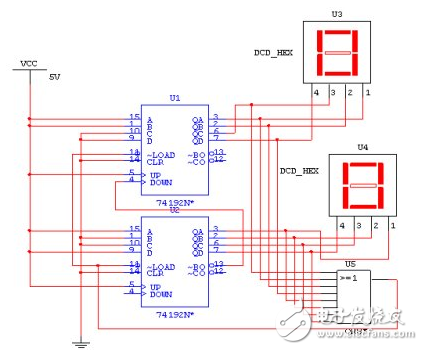

电路图如下:

它是一个由74LS192可逆计数器组成的40倒计时到0的减法计数器,实现红绿灯转换时的显示。由于时间紧迫,在实验时未能调到正常工作状态。#p#

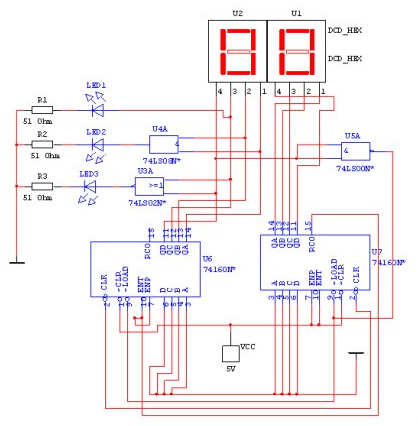

74ls160应用电路图(四)

#e#

交通灯控制电路总图:

实验器材

(1)74LS90N(2)74LS00N(3)74LS47(4)5.1KR(5)10KR(6)36KR(7)51欧R(8)LM555CM(9)DCDHEX(10)LED(红黄绿)

元器件功能

74ls160应用电路图(四)

电路原理

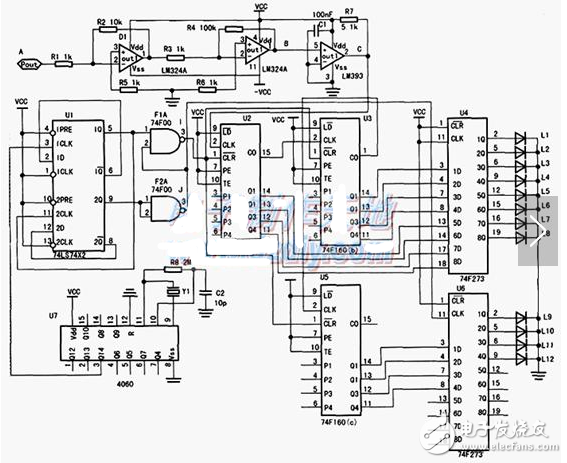

系统电路如下图所示。

(1) 放大电路:放大电路部分主要由一块LM324集成运放及外围元件组成。本放大电路采用两级放大,第一级信号的增益为20dB,第二级的信号增益为 40dB,两级的放大倍数为1000倍,其频率的带宽为0~5kHz。采用多级放大可以提高的放大电路的通频带,如果被测的信号频率较高。可以采用多级放 大来提高通频带,根据实际情况而定,由于本电路的测频范围低,对通频带不做太多的要求。图2中,A端为被测信号的输入端。B端为放大电路的输出端,接整形 电路的输入。

(2)整形电路:整形电路的主要作用是将第一部分放大的交变信号整形为数字信号(即幅度为5V的方波信号),其电路主要由比较器组成,该电路中我们选用LM393比较器,B端为整形电路输入端,C为整形电路的输出端接E端。

(3)计数电路:计数电路部分我们选用3片十进制加法计数器74LS160的级联来实现0-999Hz的频率显示,74LS160为可预置的十进制同步计数器,利用其级联,可以构成任意进制的计数器。

74LS160(a) 的2脚为脉冲信号的输入端,1脚清零端。74LS160(a)的CO进位端接74LSl60(b)的CLK脉;中输入端,74LS160(b)的进位端接 74LS160(c)的CLK脉冲输入端,三块计数器的PE、TE及LD端接电源.使计数器工作在计数的状态,CLR端接时基电路,由时基电路来控制计数 与清零。

(4)显示电路:显示电路部分主要由二块74LS273锁存器和12个红色发光二极管组成,74LS273是8位数据/地址锁存器。他是 一种带清除功能的8D触发器,主要实现对计数电路的输出信号进行锁存,由于计数器的频率较快。采用的是动态显示,我们为了显示的稳定,便于观察,所以在计 数器的输出端进行锁存。该锁存器的锁存信号由时基电路来提供,且当1脚为高电平时,11(CLK)脚是锁存控制端,并且是上升沿触发锁存,当11脚有一个 上升沿,立即锁存输入脚3、4、7、8、13、14、17、18的数据,并且立即呈现在输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、 12(Q4)、15(Q5)、16(Q6)、19(Q7)上。74LS273的CLR端接高电平,使其工作在不清零状态。

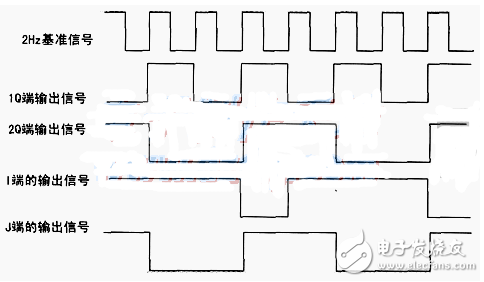

(5)时基信号产生电 路:该电路的主要作用是产生O.5Hz的时基信号(即周期为2秒,脉宽为1秒的闸门信号)为锁存器提供锁存信号和为计数电路提供计数闸门信号,实现频率计 数与显示。时基信号产生电路由一个频率为3.2768MHz的晶振和一块CD4060分频器以及外围元件够成。CD4060(IC)是一种带有振荡器的 14级分频器电路。用作振荡器时需外接R、C元件或石英晶体和电容器。内部包含两个非门和14级2分频电路,它所产生的信号频率为32768Hz,经14 级两二分频后,得到一个2Hz的脉冲信号。下图H端为2Hz信号的输出端。

(6)计数器与锁存器控制电路该部分电路主要是控制计数电路的清零、计数与锁存电路的锁存显示。该电路的核心器件是一块 D触发器74L.S74与一块与非门74LS00组成。H为2Hz方波信号(即周期为0.5s,时基电路产生)的输入端I、J为控制信号的输出端,分别接 计数器的清零端与锁存电路的CLK时钟端,H、I、J端的信号时序如下图所示。

基准信号经过D触发器分频后便获得1Q和2Q的方波信号,经由两个与非即可得到l端和J端的方波信号。当l端的信号在高电平时计数器工作在计数状态,低电平时对计数器清零。当l端的信号处于下降沿的时候,此时J端的信号处于上升沿。

该上升沿信号使锁存器开始工作,直到下一个上升沿的到来.这样便实现输入信号的计数与锁存。

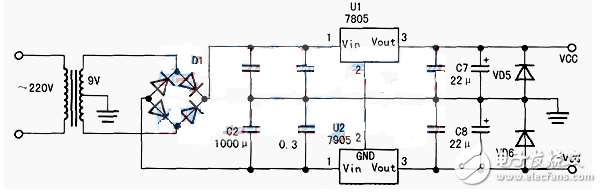

(7)电源电路:该电路的整体供电需要双5V,因此我们可以设计一个简单的双电源供电电路。电路原理图如下图所示。

-

lm324引脚图和参数,lm324应用电路讲解2023-07-25 56629

-

74ls160引脚图及功能真值表介绍2022-05-25 178626

-

数电交通灯参考设计(附Multisim仿真电路+原理文档)2021-08-25 10648

-

74ls160和74ls161区别2018-05-08 127766

-

红绿灯控制电路图大全(555\74LS192\计数器74LS160)2018-05-07 173195

-

tlc320ad75c的数据手册2017-05-23 1283

-

lm324引脚图_lm324管脚图_lm324应用电路(含中文资料)2016-10-21 387269

-

LM324应用电路图2015-10-20 8817

-

lm324这样的电路图没问题吗?2013-08-17 5239

-

20 位Σ-Δ立体声ADA电路TLC320AD75C的接口电2010-06-17 1144

-

LM324的应用电路及原理2010-03-24 7891

-

LM324 Pinouts 电路图2008-10-13 7569

-

lm324比较器电路图2008-03-20 10408

-

74ls160引脚图管脚图及功能真值表2008-01-06 132484

全部0条评论

快来发表一下你的评论吧 !