74ls163中文资料汇总(74ls163引脚图及功能_内部结构图及应用电路)

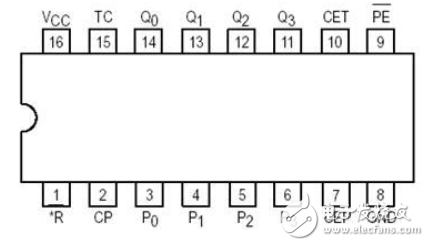

芯片引脚图

描述

74LS163是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能。

74ls163引脚图

74ls163引脚功能

时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET置数PE

数据输出端Q0~Q3

以及进位输出TC.(TC=Q0·Q1·Q2·Q3·CET)

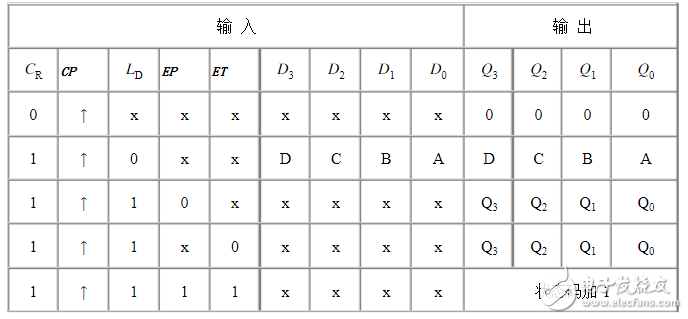

74ls163功能表

从74LS163功能表功能表中可以知道,当清零端CR=“0”,计数器输出Q3、Q2、Q1、Q0立即为全“0”,这个时候为异步复位功能。当CR=“1”且LD=“0”时,在CP信号上升沿作用后,74LS163输出端Q3、Q2、Q1、Q0的状态分别与并行数据输入端D3,D2,D1,D0的状态一样,为同步置数功能。而只有当CR=LD=EP=ET=“1”、CP脉冲上升沿作用后,计数器加1。74LS163还有一个进位输出端CO,其逻辑关系是CO=Q0·Q1·Q2·Q3·CET。合理应用计数器的清零功能和置数功能,一片74LS163可以组成16进制以下的任意进制分频器。

74ls163应用电路

(一)以74LS163为基础设计一个6分频电路

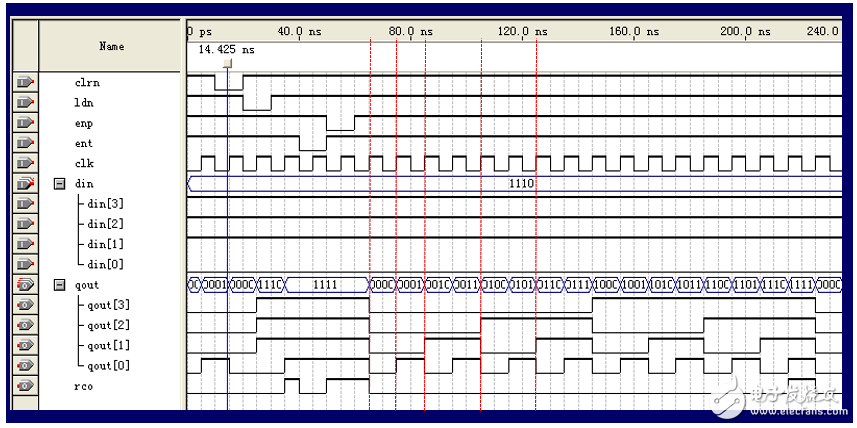

首先,需要明白什么叫分频,图3展示了分频的效果:

分频通常以CP(时钟脉冲)为基础,从图3中可以看出:qout[0]的周期为CP的2倍,qout[1]的周期为CP的4倍,qout[2]位8倍,qout[3]为16倍,显然,其频率分别为CP的1/2, 1/4, 1/8, 1/16,即所谓的2-分频,4-分频,8-分频,16-分频。

再进一步分析,对于qout[0],其变化为:当一个时钟脉冲来临时,qout[0]变化一次;对于qout[1],每两个时钟脉冲,qout[1]值变化一次;对于qout[2],每四个时钟脉冲,qout[2]值变化一次;对于qout[3],每8个时钟脉冲,qout[3]值变化一次。依次类推,如果要做6分频,显然应该是每3个时钟脉冲,值变化一次,如何用74LS163来做6-分频呢?

显然,这个问题变为:如何使74LS163中的某一位每3个时钟脉冲跳变一次。显然,只有QD和QC这两位的变化可能满足(QB每两个脉冲跳变一次,QA每个脉冲跳变一次),如果选择QC,显然可以找出一个序列:

0000 —》 0001 —》 0010 —》 1101 —》 1110 —》1111 —》0000 —》 …

对于QC,先是3个0,然后是3个1,开始循环,正好是6分频。仔细观察,发现这个循环对于QD也是6分频。

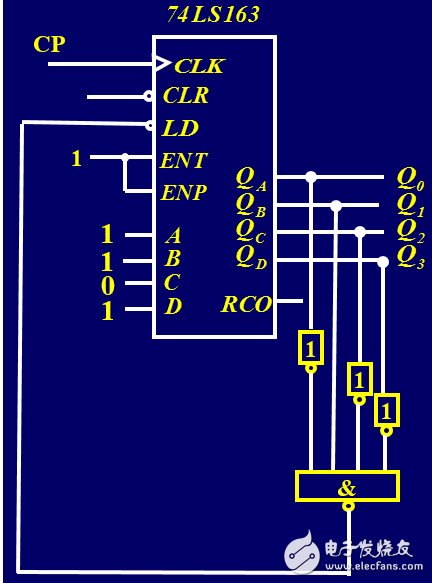

针对上面分析得到的状态迁移序列,如何用74LS163来实现呢?对于前半部0000 —》 0001 —》 0010,执行的是正常的计数功能,对于后半部1101 —》 1110 —》1111( —》0000),执行的也是正常的计数功能,只有0010 —》 1101是一个跳跃,即当计数器状态为0010时,下一个状态需要用到163计数器的并行置数功能,因此,需要对163的计数器的输出进行判断,当输出为0010时,用1101对电路进行置数(确保下一时刻电路状态为1101)。

在此分析的基础上,其电路图如图4所示:

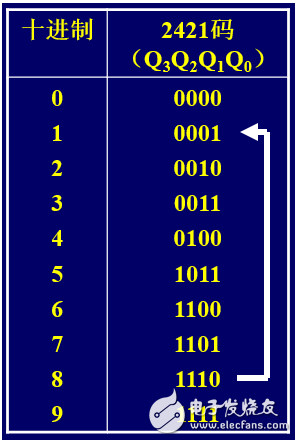

(二)2421码的模8电路

假设要求模8的状态序列如下图5所示:

在图5中,模8的状态迁移序列为:

0001 —》 0010 —》 0011 —》 0100 —》 1011 —》 1100 —》 1101 —》 1110 —》 0001 —》 …

即:初始状态为0001,当状态为1110时,一轮计满并迁移到状态0001。

这个状态迁移序列中,需要注意的地方包括:

- 初始状态为0001,即初始时需要置位

- 序列前半部分 0001 —》 0010 —》 0011 —》 0100和序列后半部分1011 —》 1100 —》 1101 —》 1110执行的是正常的计数功能

- 0100 —》 1011有状态跳跃,在到达状态0100时,需要置数;1110 —》 0001,即记录一轮满时,需要置数

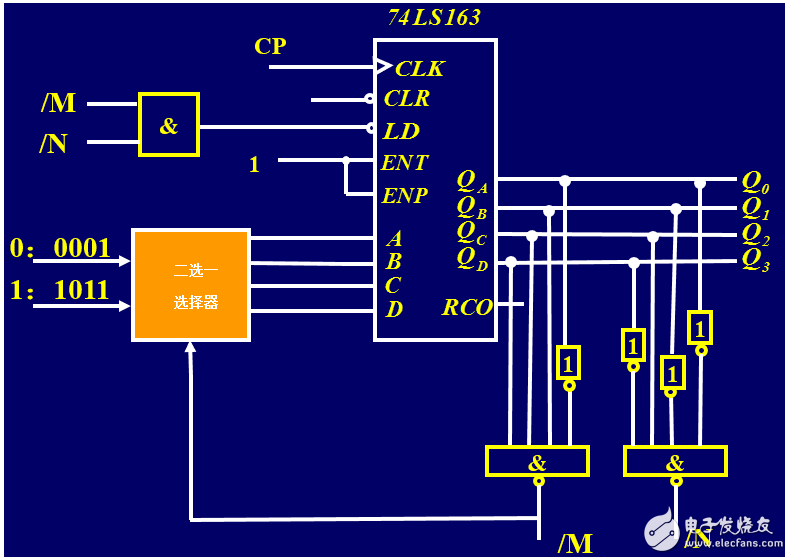

从上面的分析中得知,这个电路中存在两次置数,一次为初始状态的置数,另一个则为0100 —》 1011状态迁移时的置数,并且两次需要置的数值是不一样的,其它情况正常计数。因此,置数的时候需要作二选一,即从两个数中选择一个置数,需要一个二选一的选择器;另外,还要确定置数的时机,显然,当状态为1110时,需要置数为0001,当状态为0100时,需要置数为1011。

由上分析可知,其对应的电路图如图6所示:

-

74ls163是几进制同步计数器2024-10-18 4131

-

74ls163引脚图及功能表2021-07-08 97735

-

求74LS163芯片的内部电路图2019-05-10 6949

-

74ls85中文资料汇总(74ls85引脚图及功能_应用电路)2018-05-29 227071

-

74ls161与74ls163有什么区别2018-05-08 63057

-

74ls74中文资料汇总(74ls74引脚图及功能_内部结构及应用电路)2018-04-28 629666

-

74ls02中文资料汇总(74ls02引脚图及功能_真值表及应用电路)2018-04-08 206720

-

74ls175是什么(74ls175引脚图及功能_内部结构原理图及应用电路)2018-02-01 211859

-

数字钟设计。老师要求小时部分必须用一块74ls163完成。2013-12-16 7509

-

74LS163中文资料pdf2008-03-19 4982

全部0条评论

快来发表一下你的评论吧 !