74ls193中文资料汇总(74ls193引脚图及功能_工作原理及应用电路)

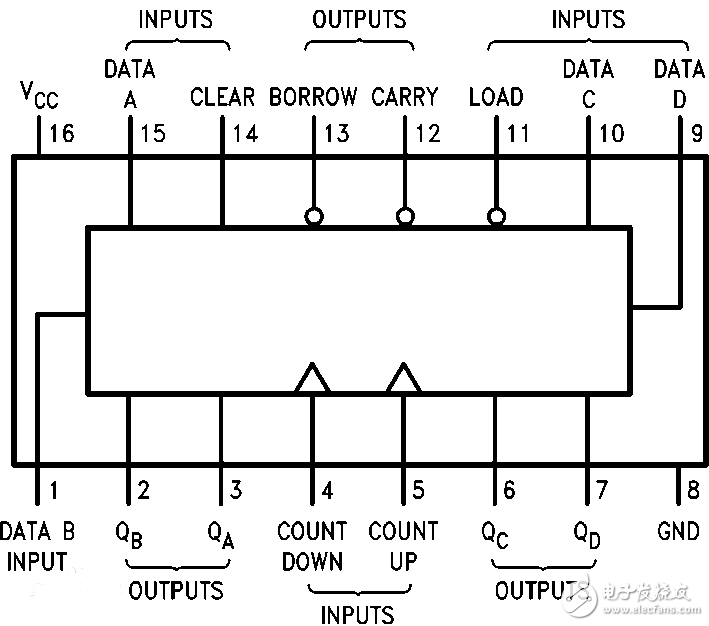

芯片引脚图

描述

74ls193工作原理

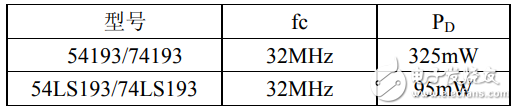

193为可预置的十进制同步加/减计数器,共有54193/74193,54LS193/74LS193两种线路结构形式。其主要电特性的典型值如下:

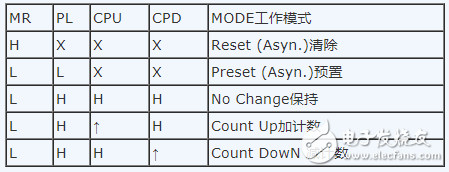

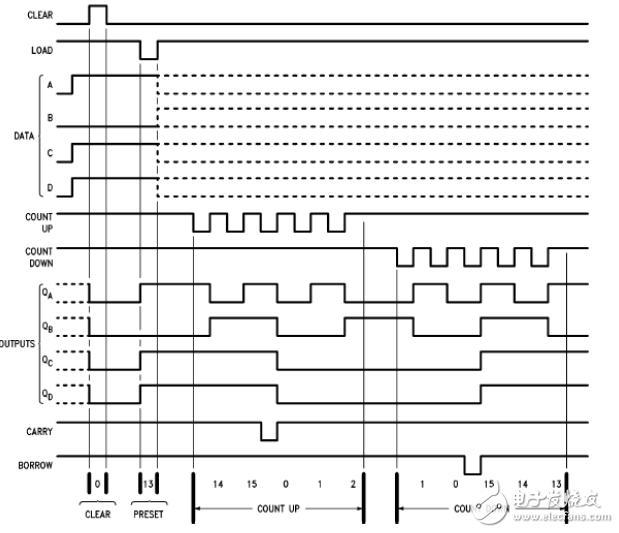

193的清除端是异步的。当清除端(CLEAR)为高电平时,不管时钟端(CDOWN、CUP)状态如何,即可完成清除功能。

193的预置是异步的。当置入控制端(LOAD)为低电平时,不管时钟(CDOWN、CUP)的状态如何,输出端(QA-QD)即可预置成与数据输入端(A-D)相一致的状态。

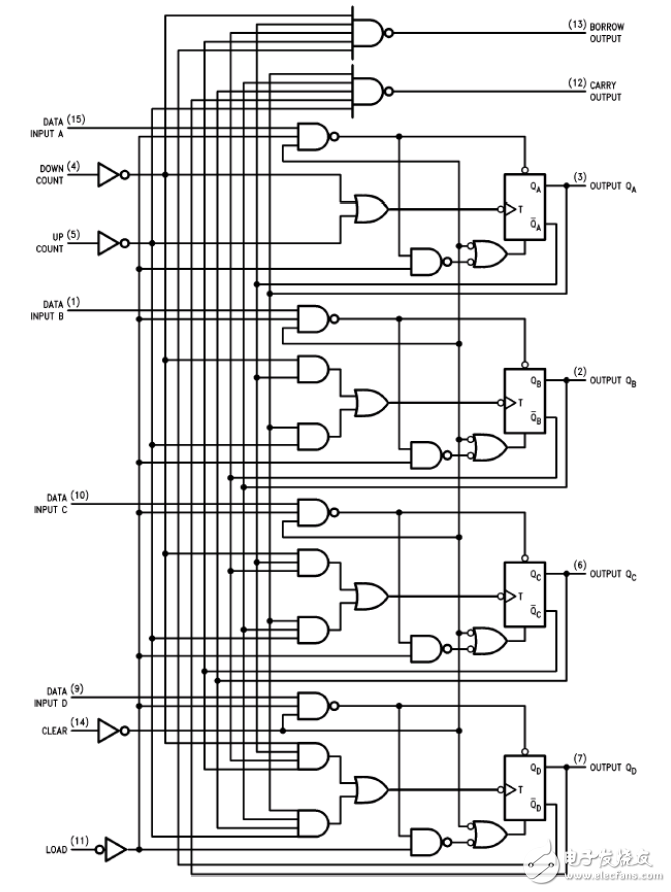

193的计数是同步的,靠CDOWN、CUP同时加在4个触发器上而实现。在CDOWN、CUP上升沿作用下QA-QD同时变化,从而消除了异步计数器中出现的计数尖峰。当进行加计数或减计数时可分别利用CDOWN或CUP,此时另一个时钟应为高电平。

当计数上溢出时,进位输出端(CARRY)输出一个低电平脉冲,其宽度为CUP低电平部分的低电平脉冲;当计数下溢出时,错位输出端(BORROW)输出一个低电平脉冲,其宽度为CDOWN低电平部分的低电平脉冲。

当把BORROW和CARRY分别连接后一级的CDOWN、CUP,即可进行级联。

74ls193引脚图

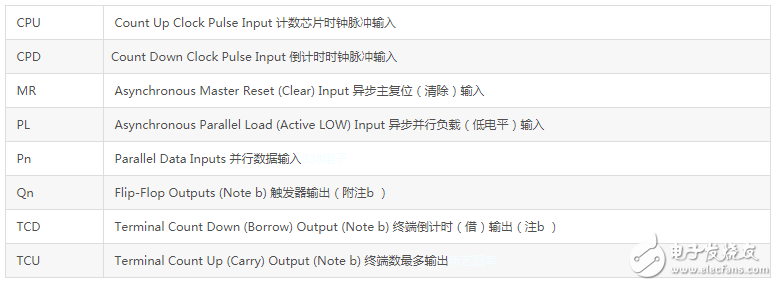

引出端符号

BORROW错位输出端(低电平有效)

CARRY进位输出端(低电平有效)

CDOWN减计数时钟输入端(上升沿有效)

CUP加计数时钟输入端(上升沿有效)

CLEAR异步清除端

A-D并行数据输入端

LOAD异步并行置入控制端(低电平有效)

QA-QD输出端

74ls193引脚功能

74ls193真值表

极限值

电源电压7V

输入电压

54/741935.5V

54/74LS1937V

工作环境温度

54×××-55~125℃

74×××0~70℃

储存温度-65℃~150℃

74ls193逻辑图

74ls193时序图

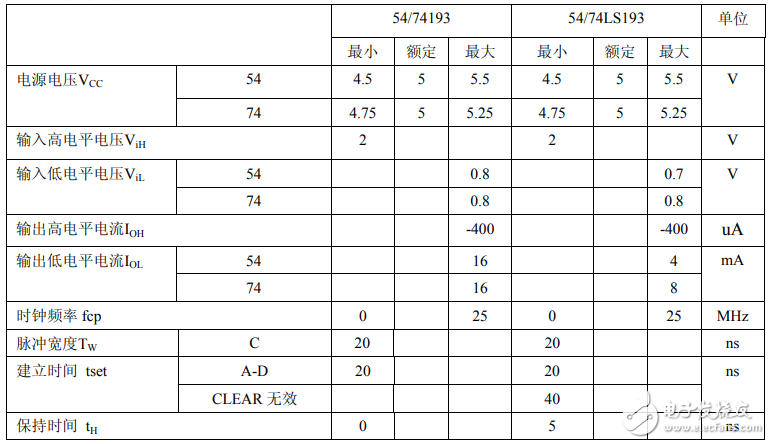

推荐工作条件:

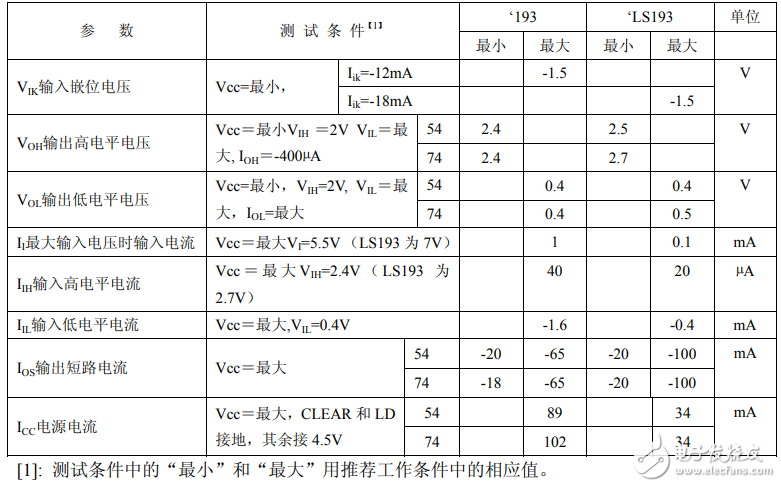

静态特性(TA为工作环境温度范围)

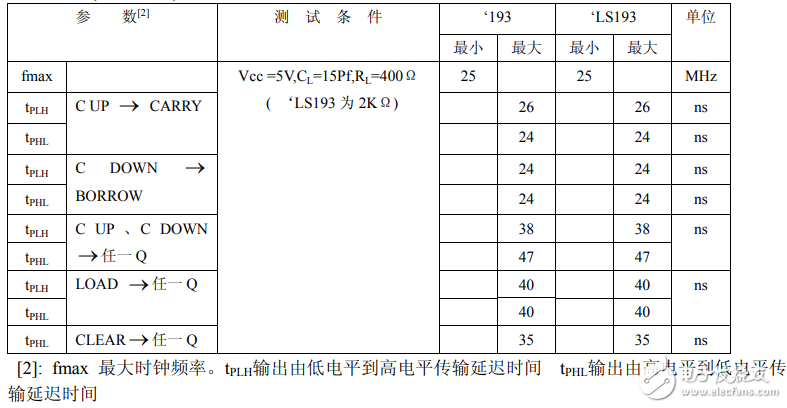

动态特性(TA=25℃)

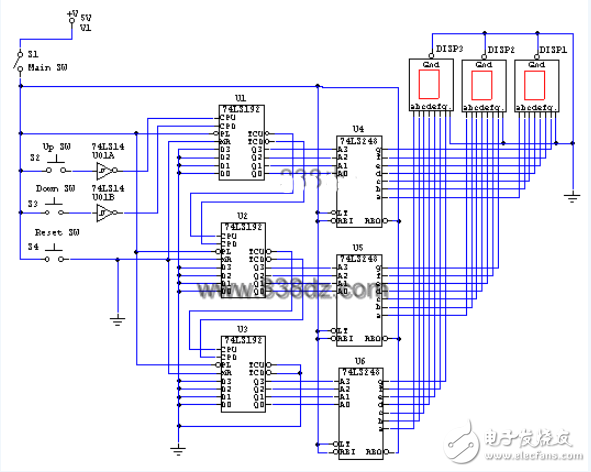

74ls193应用电路(一)

#e#74ls193应用电路(一)

原理:本电路复杂程度为55个等效门。本电路通过同时触发所有触发器而提供同步操作,以便在使用控制逻辑结构时,输出端的变化可相互重合。本工作方式避免了一般用异步(行波时钟)计数器所带来的计数输出的尖峰脉冲。四个主从触发器的输出端,由两计数(时钟)输入之一的“低”到“高”电平的过渡而被触发。计数方向在其它计数输入端为“高”时,由脉冲的计数输入端所定。本电路为全可编程的,当置数输入为“低”时,把所希望的数据送入数据输入端上,来把每个输出端预置到两电平之一。输出将符合独立于计数脉冲的数据输入的改变。该特点可使电路以预置输入而简单地更改计数长度,用作N模数分频器(除法器)。清零输入在加高电平时,迫使所有输出端为低电平。清零功能独立于计数输入和置数输入。清零、计数和置数等输入端都是缓冲过的,它降低了驱动的要求,这就可减少为长字所要求的时钟驱动器数等等。本电路都设计成可被直接级联而勿需外接电路。借位和进位两输出端可级联递增计数和递减计数两功能。借位输出在计数器下谥时,产生宽度等于递减计数输入的脉冲;同样,进位输出在计数器上谥时,产生宽度等于递加计数输入的脉冲。

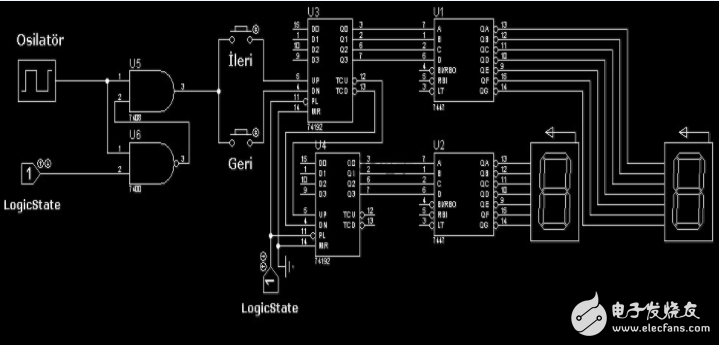

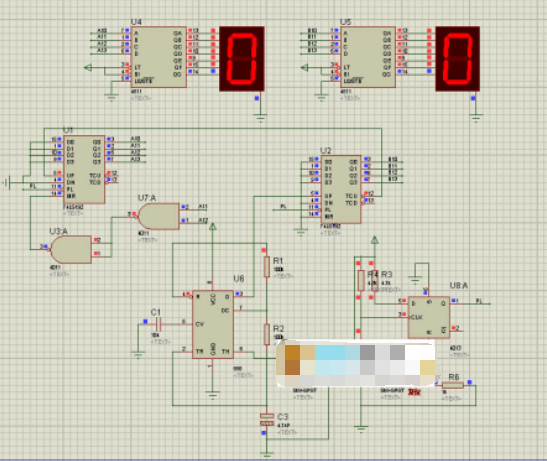

74ls193应用电路(二)

利用555定时器产生1秒脉冲,CD4011与74LS192(74LS193)组成任意进制加减计数器,25秒(S)、50秒(S)、60秒(S)、99秒(S)。

秒表可以加入启动、停止和复位等功能。CD4013双D触发器制作。

电路介绍:4511驱动数码管CD4013双D触发器作为启动停止功能实验模块555芯片提供时钟信号1秒74LS193十进制可逆计数器,设计计数值。CD4011与门,是否达到计数值判断功能。

- 相关推荐

- 热点推荐

- 计数器

-

74LS192/74LS193计数器数据手册2024-02-18 3711

-

74ls193引脚图及功能表2021-07-09 68766

-

74ls85中文资料汇总(74ls85引脚图及功能_应用电路)2018-05-29 225691

-

74ls190中文资料汇总(74ls190引脚图及功能_工作原理及应用电路)2018-05-28 356596

-

74ls247中文资料汇总(74ls247引脚图及功能_工作原理及应用电路)2018-05-09 96604

-

74ls165中文资料汇总(74ls165引脚图及功能_工作原理及应用电路)2018-05-08 78411

-

74ls273中文资料汇总(74ls273引脚图及功能_工作原理及应用电路)2018-04-26 189172

-

74ls00中文资料汇总(74ls00引脚图及功能_工作原理及应用电路)2018-04-08 371523

-

74LS193英文手册2016-11-21 676

-

求74LS193设计的60进制计数器2013-01-05 11357

-

74LS193中文资料.pdf2008-03-15 3982

全部0条评论

快来发表一下你的评论吧 !