两个74LS192级联构成两位十进制计数器

IC应用电路图

512人已加入

描述

下面以两个74LS192级联构成两位十进制计数器控制实现0.0~9.9V的切换为例。低位计数器输出Qo、Qi、Q2、Q3分别提供0.1V、0.2V、0.4V、0.8V的控制信号;高位计数器输出Qo.Qi、Q2、Q3分别提供1V、2V、4V、8V的控制信号。采用按键作为步进加、步进减的控制按钮;为了防止在按钮过程中出现振铃现象,在计数器加计数、减计数时钟脉冲端与加、减计数按钮之间接入施密特触发器74LS14,以消除振铃现象。

预置数选通端可以接拨码开关,以实现预置数的设置;用开关控制预置数选通端的选通状态,开关闭合时预置数选通端为低电平,选通端有效,预置数送到输出端;开关断开时预置数选通端为高电平,选通端无效,不能将预置数送到输出端。

由两个74LS192级联构成两位十进制计数器的电路如下图所示。

在图中,1V以下的计数器74LS192的时钟可以由“+”、“-”两键分别控制输出电压步进增减,1V以上的计数器74LS192的加、减计数时钟则由低位的进、借位输出提供。

如果需要3位以上的减计数和预置数,则可以在图中的基础上继续级联192、相应的拨码开关及相应的74LS14,直到满足要求为止。

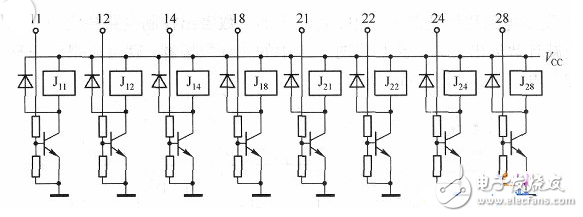

74LS192的输出接驱动继电器激磁线圈的晶体管基极,如下图所示。

为了使晶体管与TTL电平匹配,需要在74LS输出与晶体管基极之间串联适当的电阻,如15~20kΩ的电阻,同时在晶体管基极与发射极之间并联lOkΩ的电阻,以确保在74LS192输出低电位时晶体管处于关断状态。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

74ls192的功能及原理2024-01-22 34088

-

如何去实现基于74ls192芯片和与非门的进制加法计数器设计呢2021-11-02 19499

-

74ls160价格 74ls160十进制计数器简介2021-06-05 18491

-

74ls192计数器应用电路图大全(五款电子骰子/计时/定时电路)2018-05-28 148373

-

基于74ls192设计4/7进制计数器详解2018-01-31 63532

-

74ls160构成24进制计数器2018-01-18 174589

-

基于74LS161的60进制计数器设计方案介绍2018-01-17 71436

-

74ls192和74ls160的区别有哪些2017-12-21 35626

-

十进制可逆计数器74LS192引脚图管脚及功能表2011-05-19 132358

-

74LS161构成的五十(50)进制计数器电路图-原理图2009-03-28 37693

-

74LS192中文资料pdf2008-03-18 7642

全部0条评论

快来发表一下你的评论吧 !