74ls374中文资料汇总(74ls374引脚图及功能_真值表及特性)

芯片引脚图

描述

本文主要介绍的是74ls374中文资料汇总,首先介绍了74ls374引脚图及功能,其次介绍了74ls374逻辑图及真值表,最后阐述了74ls374推荐工作条件及特性,具体的跟随小编一起来了解一下。

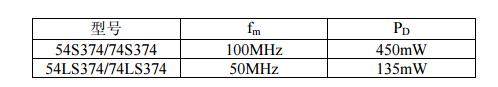

74ls374为具有三态输出的八D边沿触发器,共有54/74S374和54/74LS374两种线路结构型式,其主要电器特性的典型值如下(不同厂家具体值有差别):

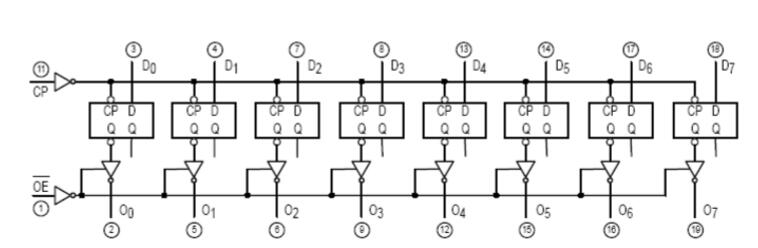

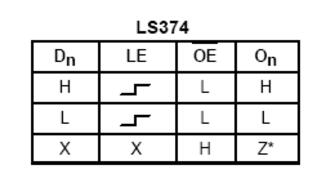

74ls374的输出端O0~O7可直接与总线相连。当三态允许控制端OE为低电平时,O0~O7为正常逻辑状态,可用来驱动负载或总线。当OE为高电平时,O0~O7呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。当时钟端CP脉冲上升沿的作用下,O随数据D而变。由于CP端施密特触发器的输入滞后作用,使交流和直流噪声抗扰度被改善400mV。

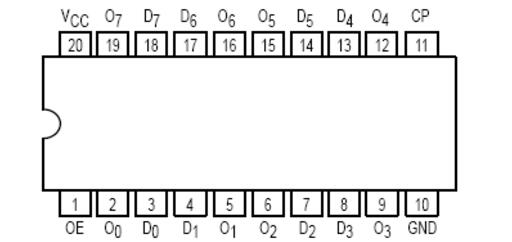

74ls374引脚图及功能

引脚功能

D0~D7————————数据输入端

OE——————————三态允许控制端(低电平有效)

CP——————————时钟输入端

O0~O7————————输出端

74ls374逻辑图

74ls374真值表

74LS374极限值

电源电压…………………………………………7V

输入电压

54/74S374……………………………………5.5V

54/74LS374……………………………………7V

输出高阻态时高电平电压…………………………5.5V

工作环境温度

54XXX…………………………………-55~125℃7

4XXX…………………………………0~70℃

存储温度…………………………………………-65~150℃

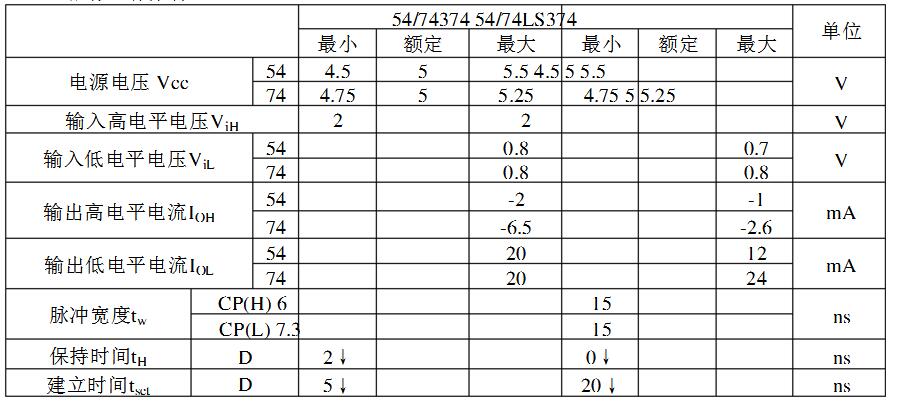

74ls374推荐工作条件

74ls374特性

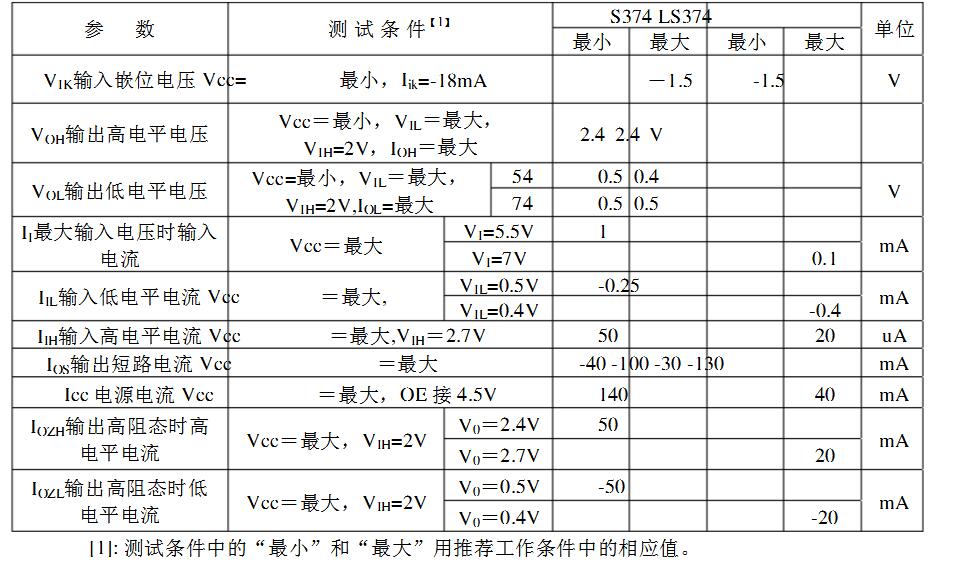

1、静态特性(TA为工作环境温度范围)

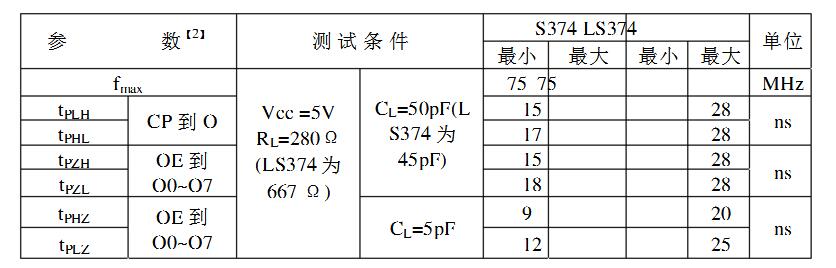

2、动态特性(TA=25℃)

tPLH输出由低到高传输延迟时间

tPHL输出由高到低传输延迟时间

tPZH输出由高阻态到高允许时间

tPZL输出由高阻态到低允许时间

tPHZ输出由高到高阻态禁止时间

tPLZ输出由低到高阻态禁止时间

推荐下载:《74ls374中文资料》

-

74ls160引脚图及功能真值表介绍2022-05-25 176961

-

74ls00引脚图及功能真值表和特性参数2021-06-16 202657

-

74ls374中文资料汇总(74ls374引脚图及功能_工作原理及应用电路)2018-05-28 49985

-

74ls377中文资料汇总(74ls377引脚图及功能_极限值及特性)2018-05-09 28223

-

74ls266中文资料汇总(74ls266引脚图及功能_真值表及特性)2018-05-08 10821

-

74ls152中文资料_74ls152引脚图_功能表_逻辑图_特性参数2018-05-07 25158

-

74ls125中文资料(74ls125引脚图及功能_真值表)2018-05-04 110461

-

74ls02中文资料汇总(74ls02引脚图及功能_真值表及应用电路)2018-04-08 205490

-

74ls93引脚图管脚图及功能真值表2008-12-01 23225

-

74ls11引脚图及管脚功能真值表2008-06-08 52513

-

74ls374引脚图及功能真值表2008-04-01 34509

-

74LS374中文资料.pdf2008-03-14 5113

全部0条评论

快来发表一下你的评论吧 !