LTC2924一款简单且紧凑的电源排序解决方案

描述

诸如电信设备、存储模块、光学系统、网络设备、服务器和基站等许多复杂系统都采用了 FPGA 和其他需要多个电压轨的数字 IC,这些电压轨必须以一个特定的顺序进行启动和停机操作,否则 IC 就会遭到损坏。

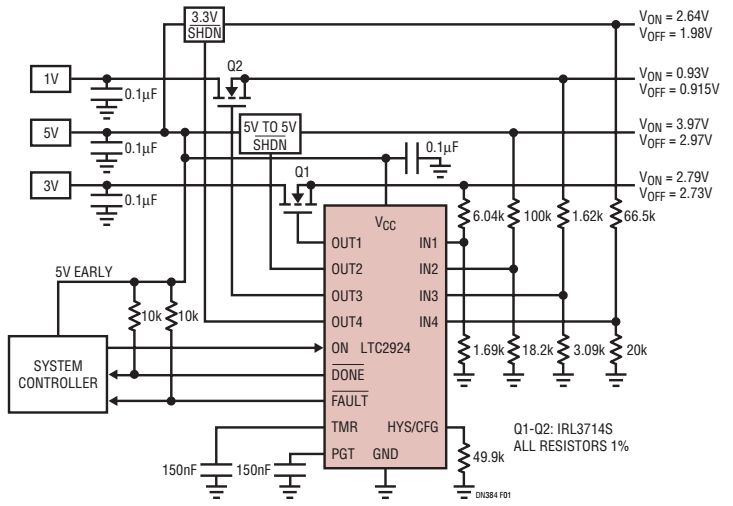

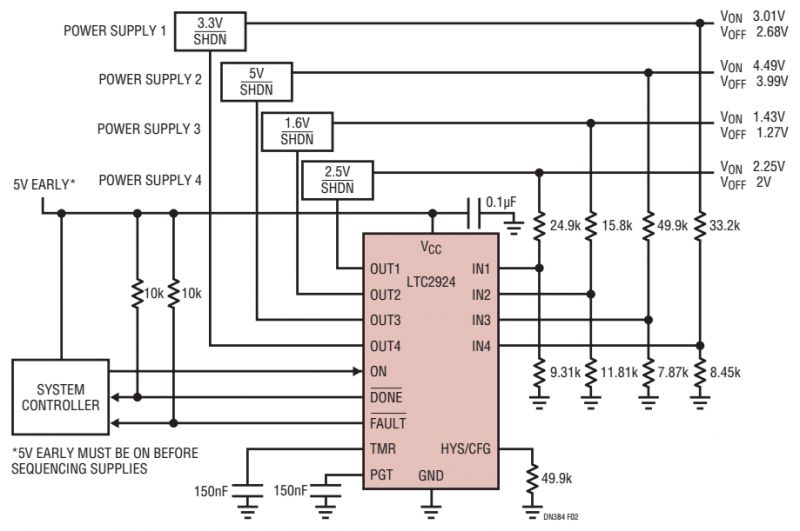

LTC2924 是一款简单且紧凑的电源排序解决方案,采用16引脚SSOP 封装(见图1和图2)。

图1: 采用外部 N 沟道 MOSFET 的典型应用

图2: 采用停机引脚的 4 个电源排序器

工作原理

采用单个 LTC2924 便可轻松完成 4 个电源的排序任务,而且,同样可以很容易地把多个 LTC2924 级联起来,用于对数目不限的电源进行排序。在允许功能度略有下降的情况下,利用单个 LTC2924 就能够对 6 个电源进行排序。

LTC2924 通过输出引脚(OUT1 至 OUT4)来控制 4 个电源的启动和停机顺序以及斜坡速率。每个 OUT 引脚采用了一个与内部充电泵相连的 10μA 电流源和一个与 GND 相连的低电阻开关。这种组合使得这些输出拥有足够的灵活性,以将其直接与多个电源停机引脚或外部 N 沟道MOSFET,开关相连。

LTC2924 通过 4 个输入引脚(IN1 至 IN4)来监视每个被排序电源的输出电压。这些输入采用精准比较器和一个经过修整的带隙电压基准来提供优于 1% 的准确度。4 个通道的上电和断电电压门限均采用阻性分压器来设定。每个通道的上电门限和断电门限可单独地进行选择。

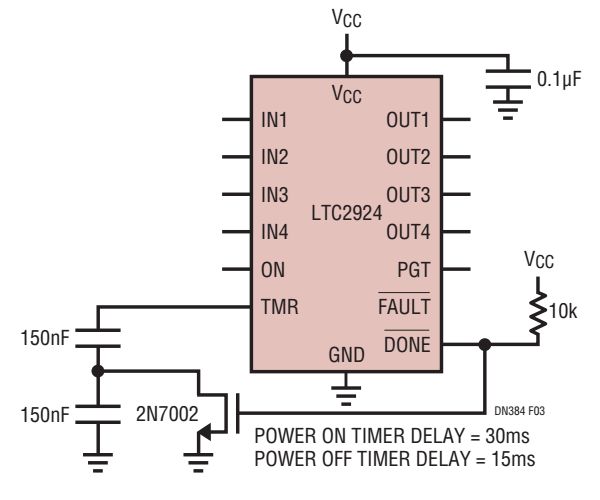

LTC2924 的定时器引脚(TMR)被用来在一个电源的启动操作完成到下一个电源的启动之间提供一个任选延迟。延迟时间通过在 TMR 引脚和地之间布设一个电容器来选择(延迟=200ms/μF),而把 TMR 引脚浮置将去除任何延迟。启动延迟与停机延迟可以不同。图 3 示出了一种停机延迟为启动延迟一半的简单电路。

图3: 设置不同的 ON/OFF 延迟

LTC2924 还包括一个电源良好定时器(PGT)。每当一个电源被使能时,LTC2924 将起动 PGT。如果任一个电源未能在分配的时间间隔之内达到其规定的标称电压,则检测到一个上电故障。

结论

LTC2924 适合众多的电源排序和监视应用。由于所需的外部元件极少并采用了 16 引脚窄式 SSOP 封装,因此,基于 LTC2924 的电源排序解决方案占用的板级空间极小。

电源使能引脚无需设计师进行配置,但仍然具有足够的通用性,能够直接驱动停机引脚或外部 N 沟道 MOSFET。可简单地通过增设一个电容器来实现电源的软起动。如果需要对 4 个以上的电源进行排序,则可把多个 LTC2924 级联起来,以对几乎无限数量的电源进行排序。使 LTC2924 适合特定的应用无需借助软件,而且,可在系统集成期间简单地通过改变电阻值和电容值来对设计进行精调。由于设计简单易行、元件成本低廉且占板面积小,因而使得 LTC2924 成为电源排序和监视用途的绝佳选择。

-

ADM1169:多电源系统的监控与排序解决方案2026-02-28 293

-

基于LM3880/LM3881的简单6通道电源轨排序解决方案2022-11-17 702

-

如何设计一款安静且紧凑的工业用电源2022-11-04 520

-

关于电源排序的解决方案你了解吗2021-11-24 3089

-

一个简单6通道电源轨排序解决方案说明2021-11-10 963

-

LTC2924:四电源序列器产品手册2021-04-24 594

-

四通道电源排序器LTC2924相关资料下载2021-03-29 1364

-

适用于电源排序和监视应用的LTC29242019-09-18 1157

-

电路图LTC3407是一款带有集成电源开关的双同步降压DC / DC转换器2019-07-22 1262

-

采用外部N沟道MOSFET的典型应用电源排序LTC29242019-04-16 2189

-

一个简单6通道电源轨排序解决方案2016-01-29 3188

全部0条评论

快来发表一下你的评论吧 !