浅析PLD总体结构及逻辑实现原理

可编程逻辑

描述

一、基于乘积项(Product-Term)的PLD结构

采用这种结构的PLD芯片有:Altera的MAX7000,MAX3000系列(EEPROM工艺),Xilinx的XC9500系列(Flash工艺)和Lattice,Cypress的大部分产品(EEPROM工艺)

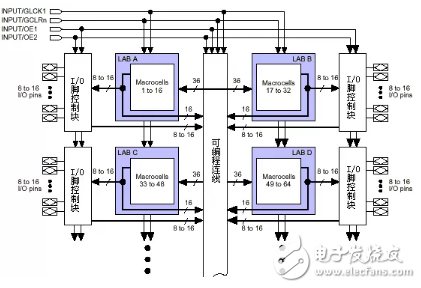

我们先看一下这种PLD的总体结构(以MAX7000为例,其他型号的结构与此都非常相似):

图1 基于乘积项的PLD内部结构

这种PLD可分为三块结构:宏单元(Marocell),可编程连线 (PIA)和I/O控制块。 宏单元是PLD的基本结构,由它来实现基本的逻辑功能。图1中兰色部分是多个宏单元的集合(因为宏单元较多,没有一一画出)。可编程连线负责信号传递,连 接所有的宏单元。I/O控制块负责输入输出的电气特性控制,比如可以设定集电极开路输出,摆率控制,三态输出等。 图1 左上的INPUT/GCLK1,

INPUT/GCLRn,INPUT/OE1,INPUT/OE2 是全局时钟,清零和输出使能信号,这几个信号有专用连线与PLD中每个宏单元相连,信号到每个宏单元的延时相同并且延时最短。

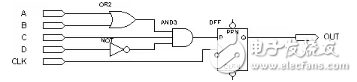

宏单元的具体结构见下图:

图2 宏单元结构

左侧是乘积项阵列,实际就是一个与或阵列,每一个交叉点都是一个可编程 熔丝,如果导通就是实现“与”逻辑。后面的乘积项选择矩阵是一个“或”阵列。两者一起完成组合逻辑。图右侧是一个可编程D触发器,它的时钟,清零输入都可 以编程选择,可以使用专用的全局清零和全局时钟,也可以使用内部逻辑(乘积项阵列)产生的时钟和清零。如果不需要触发器,也可以将此触发器旁路,信号直接 输给PIA或输出到I/O脚。

二、乘积项结构PLD的逻辑实现原理

下面我们以一个简单的电路为例,具体说明PLD是如何利用以上结构实现逻辑的,电路如下图:

图3

假设组合逻辑的输出(AND3的输出)为f,则f=(A+B)*C*(!D)=A*C*!D + B*C*!D ( 我们以!D表示D的“非”)

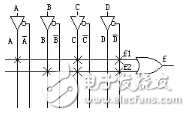

PLD将以下面的方式来实现组合逻辑f:

图4

A,B,C,D由PLD芯片的管脚输入后进入可编程连线阵列 (PIA),在内部会产生A,A反,B,B反,C,C反,D,D反8个输出。图中每一个叉表示相连(可编程熔丝导通),所以得到:f= f1 + f2 = (A*C*!D) +

(B*C*!D) 。这样组合逻辑就实现了。 图3电路中D触发器的实现比较简单,直接利用宏单元中的可编程D触发器来实现。时钟信号CLK由I/O脚输入后进入芯片内部的全局时钟专用通道,直接连接 到可编程触发器的时钟端。可编程触发器的输出与I/O脚相连,把结果输出到芯片管脚。这样PLD就完成了图3所示电路的功能。(以上这些步骤都是由软件自 动完成的,不需要人为干预)

图3的电路是一个很简单的例子,只需要一个宏单元就可以完成。但对于一个复杂的电路,一个宏单元是不能实现的,这时就需要通过并联扩展项和共享扩展项将多个宏单元相连,宏单元的输出也可以连接到可编程连线阵列,再做为另一个宏单元的输入。这样PLD就可以实现更复杂逻辑。

这种基于乘积项的PLD基本都是由EEPROM和Flash工艺制造的,一上电就可以工作,无需其他芯片配合。

-

什么是PLD的定义和应用 PLD与FPGA的区别和联系2025-02-01 7604

-

如何快速入门PLD电路设计2025-01-20 1925

-

什么是pld的基本结构 什么是plc控制原理2023-07-05 7757

-

一文详细了解可编程逻辑器件(PLD)2022-03-22 11234

-

可编程逻辑器件PLD课件下载2021-08-13 1479

-

PLD可编程逻辑器件2021-07-22 2319

-

FPGA与PLD有什么关系?如何区别?2018-08-28 3191

-

EDA技术_PLD基本结构原理2016-07-13 970

-

关于PLD器件2012-10-30 2352

-

可编程逻辑器件技术_pld技术2012-06-16 1297

-

PLD设计方法及步骤2010-09-18 5202

-

基于PLD芯片的时序逻辑设计与实现2009-10-29 917

-

什么是PLD(可编程逻辑器件)2009-06-20 30042

-

消除组合逻辑产生的毛刺—PLD设计技巧2008-09-11 902

全部0条评论

快来发表一下你的评论吧 !