mos管对静电的防护电路

描述

在电子设备设计中,MOS管(金属-氧化物-半导体场效应晶体管)因其高效率和快速开关特性被广泛应用,但它的“脆弱性”也令人头疼——特别是对静电的高度敏感。这种敏感源于其内部结构:栅极与衬底间的绝缘层仅几个纳米厚,如同一层保鲜膜,一旦遭遇静电放电(ESD),极易被击穿,导致器件永久失效。因此,如何设计有效的静电防护电路,成为工程师必须掌握的“必修课”。

静电击穿的致命威胁

静电对MOS管的破坏主要分为两类:一是栅极绝缘层击穿,直接导致器件功能丧失;二是瞬态高压引发的漏极-源极间电流冲击,造成内部结构熔毁。例如,人体在干燥环境中行走时积累的静电电压可达数千伏,若直接接触未保护的MOS管,瞬间放电能量足以让器件“当场罢工”。更隐蔽的风险来自电路设计本身——驱动信号过快的上升时间(di/dt)可能引发寄生振荡,加剧静电击穿的概率。

防护电路设计的三大核心策略

1. 从源头隔绝静电入侵

储存与运输环节是防护的第一道关卡。MOS管应封装于导电泡沫或防静电袋中,这类材料如同“电磁屏蔽罩”,通过内部导电网络将静电电荷均匀泄放,避免局部高压聚集。在PCB组装阶段,操作人员需佩戴接地手环,工作台铺设防静电桌垫,相当于为静电搭建了一条“避雷针路径”,将人体和设备表面的电荷导入大地。

2. 栅极保护:加装“电压保险丝”

栅极作为MOS管的“控制中枢”,最需重点防护。常见方案包括:

并联齐纳二极管:在栅极与源极之间接入反向击穿电压略低于栅极耐受值的二极管,当静电电压超过阈值时,二极管迅速导通泄放电荷,如同在高压洪峰前开启泄洪闸门。

串联限流电阻:在驱动信号输出端与栅极间添加10-100Ω电阻,这相当于给电流通道增设“减速带”,既能抑制开关瞬态的高频振荡,又可降低静电脉冲的峰值电流。

诺芯盛@mos管对静电的防护电路

诺芯盛@mos管对静电的防护电路3. PCB布局的“微观防御体系”

电路板设计中的细节优化能显著提升抗静电能力:

缩短栅极走线:过长的导线会形成“天线效应”,吸收环境中的电磁干扰。将驱动电路靠近MOS管布局,可减少寄生电感,抑制电压尖峰。

增加接地屏蔽层:在敏感信号线周围布置接地的铜箔,形成“电磁隔离带”,阻挡外部静电耦合。

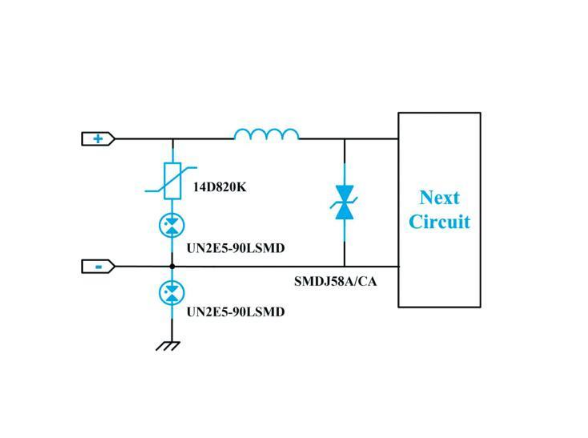

冗余设计:对高可靠性场景,可并联多个MOS管分摊电流压力,或增设TVS二极管(瞬态电压抑制器)构建多级防护网络。

驱动电路的“速度与安全平衡术”

驱动芯片直接控制MOS管的开关速度,但过快的开关会导致漏源极电压剧烈震荡,诱发寄生导通。例如,若驱动电阻过小,开关过程可能在纳秒级完成,此时漏极电感与杂散电容形成谐振回路,产生高达数百伏的瞬态电压。为此,工程师需通过实验确定最优驱动电阻值——通常以开关损耗(发热量)和电压震荡幅度的折中值为准。假设某电源模块工作电压为24V,驱动电阻选20Ω时,开关损耗可能增加5%,但电压尖峰可从50V降至30V,显著降低击穿风险。

失效案例的启示

某工业电源模块频繁出现MOS管炸毁,经检测发现故障集中在仓储环节。进一步分析显示,未使用防静电包装的MOS管在搬运过程中因摩擦积累了静电,上电瞬间栅极被击穿。改进方案中,除更换导电包装外,还在栅极添加了15V齐纳二极管,最终将故障率从3%降至0.1%。这一案例印证了“防静电无小事”的设计哲学——细节疏忽可能引发系统性风险。

-

MOS管的ESD防护措施与设计要点2025-03-10 1683

-

MOS管防护电路解析实测2025-02-27 2309

-

三极管和MOS管抗静电?2023-09-25 1774

-

一文吃透MOS管的构造、特点以及实用电路2023-01-30 6609

-

静电防护方案的保护电路介绍2022-10-19 4372

-

静电为什么能击穿MOS管?如何应对?2022-05-14 1785

-

MOS管为什么会被静电击穿 gs电阻能保护MOS吗2021-09-28 5472

-

MOS管为什么会被静电击穿?2021-02-02 2561

-

MOS管为什么会被静电击穿?gs电阻可保护MOS?2021-01-23 2158

-

【转】电路级静电防护设计技巧与ESD防护方法2019-04-23 2924

-

分享MOS管防护静电的秘密2018-11-01 4450

-

电路级静电防护设计技巧与ESD防护方法2018-10-23 2702

-

MOS管为什么会被静电击穿2017-06-01 6344

-

关于静电防护的设计2015-04-01 9686

全部0条评论

快来发表一下你的评论吧 !