Stratix 10 SoC FPGA器件案例(应用、特性、电路图)

可编程逻辑

描述

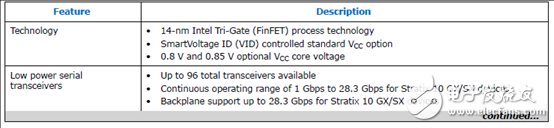

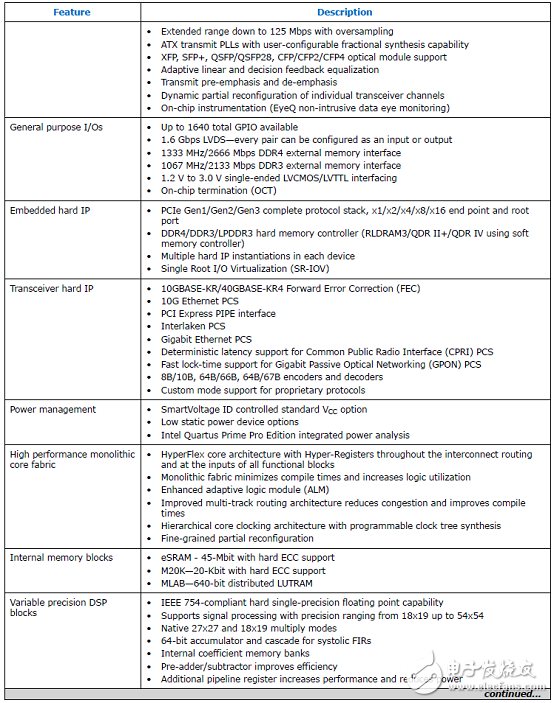

Intel公司的Stratix 10 SoC FPGA系列采用14nm三栅极(FinFET)和异构三维封装系统工艺技术,比以前高性能SoC FPGA提供2x核性能和节省多达70%的功耗, 单片核架构多达550万个逻辑单源(LE),多达96个全双工收发器通路,收发器数据速率高达28.3Gbps,嵌入eSRAM (45 Mbit)和M20K (20 kbit)SRAM存储器区块,基于PLL的分数合成和超低抖动LC振荡器,硬PCI Express® Gen3 x16 IP区块,每个收发器通路中有硬10GBASE-KR/40GBASE-KR4 FEC,每个引脚的硬存储器控制器和PHY支持DDR4速率高达2666Mbps,以及硬定点和IEEE 754兼容硬浮点可变精度数字信号处理(DSP)区块,计算功能达10 TFLOPS,主要用在计算和存储,网络,光传输网络,广播和军用雷达和保密通信,医疗诊断扫描和图像,测试测量以及无线5G网络等.本文介绍了Stratix 10 SoC FPGA器件主要特性和创新要点,框图,以及Stratix 10 SoC FPGA开发板主要特性,框图和电路图.

Intel ’s 14-nm Intel Stratix 10 SX SoCs deliver 2x core performance and up to 70% lower power over previous generation high-performance SoCs. Featuring several groundbreaking innovations, including the all new Intel Hyperflex™ core architecture,this device family enables you to meet the demand for ever-increasing bandwidth and processing performance in you most advanced applications, while meeting your power budget.

Featuring several groundbreaking innovations, including the all new HyperFlex™ core architecture, this device family enables you to meet the demand for ever-increasing bandwidth and processing performance in your most advanced applications, while meeting your power budget.

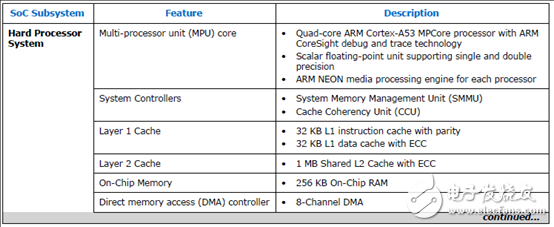

With an embedded hard processor system (HPS) based on a quad-core 64-bit ARM® Cortex®-A53, the Stratix 10 SoC devices deliver power efficient, application-class processing and allow designers to extend hardware virtualization into the FPGA fabric.Stratix 10 SoC devices demonstrate Intel’s commitment to high-performance SoCs and extend Intel’s leadership in programmable devices featuring an ARM-based processor system.

Important innovations in Stratix 10 FPGAs and SoCs include:

• All new HyperFlex core architecture delivering 2X the core performance compared to previous generation high-performance FPGAs

• Industry leading Intel 14-nm Tri-Gate (FinFET) technology

• Heterogeneous 3D System-in-Package (SiP) technology

• Monolithic core fabric with up to 5.5 million logic elements (LEs)

• Up to 96 full duplex transceiver channels on heterogeneous 3D SiP transceiver tiles

• Transceiver data rates up to 28.3 Gbps chip-to-chip/module and backplane

performance

• Embedded eSRAM (45 Mbit) and M20K (20 kbit) internal SRAM memory blocks

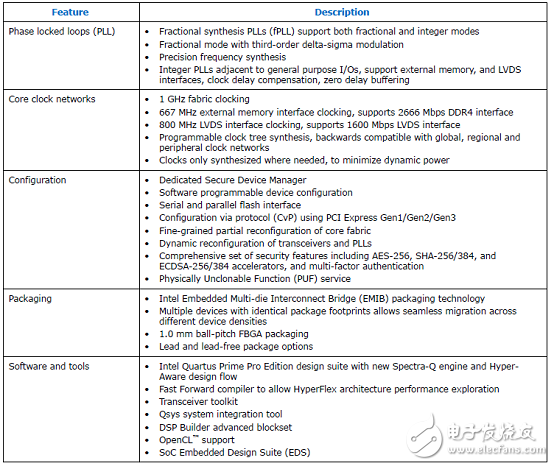

• Fractional synthesis and ultra-low jitter LC tank based transmit phase locked loops

(PLLs)

• Hard PCI Express® Gen3 x16 intellectual property (IP) blocks

• Hard 10GBASE-KR/40GBASE-KR4 Forward Error Correction (FEC) in every

transceiver channel

• Hard memory controllers and PHY supporting DDR4 rates up to 2666 Mbps per pin

• Hard fixed-point and IEEE 754 compliant hard floating-point variable precision digital signal processing (DSP) blocks with up to 10 TFLOPS compute performance with a power efficiency of 80 GFLOPS per Watt

• Quad-core 64-bit ARM Cortex-A53 embedded processor running up to 1.5 GHz in

SoC family variants

• Programmable clock tree synthesis for flexible, low power, low skew clock trees

• Dedicated secure device manager (SDM) for:

— Enhanced device configuration and security

— AES-256, SHA-256/384 and ECDSA-256/384 encrypt/decrypt accelerators and

authentication

— Multi-factor authentication

— Physically Unclonable Function (PUF) service and software programmable device configuration capability

• Comprehensive set of advanced power saving features delivering up to 70% lower

power compared to previous generation high-performance FPGAs

• Non-destructive register state readback and writeback, to support ASIC prototyping and other applications

Stratix 10 SoC FPGA应用:

With these capabilities, Stratix 10 FPGAs and SoCs are ideally suited for the most

demanding applications in diverse markets such as:

• Compute and Storage—for custom servers, cloud computing and data center acceleration

• Networking—for Terabit, 400G and multi-100G bridging, aggregation, packet processing and traffic management

• Optical Transport Networks—for OTU4, 2xOTU4, 4xOTU4

• Broadcast—for high-end studio distribution, headend encoding/decoding, edge

quadrature amplitude modulation (QAM)

• Military—for radar, electronic warfare, and secure communications

• Medical—for diagnostic scanners and diagnostic imaging

• Test and Measurement—for protocol and application testers

• Wireless—for next-generation 5G networks

• ASIC Prototyping—for designs that require the largest monolithic FPGA fabric with the highest I/O count

Stratix 10 SoC FPGA器件主要特性:

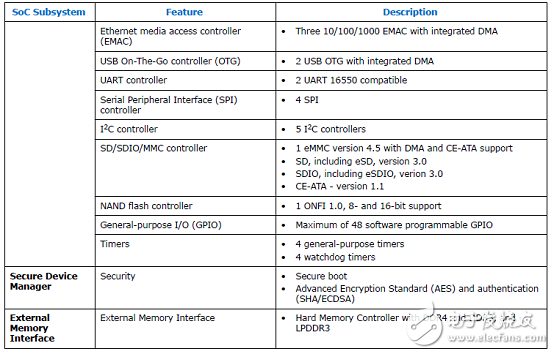

Stratix 10 SoC FPGA器件子系统主要特性:

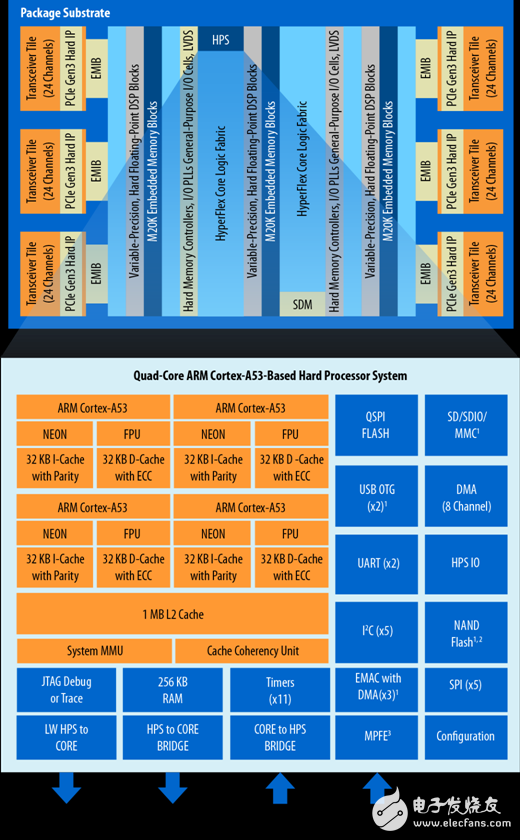

图1. Stratix 10 SoC FPGA器件框图

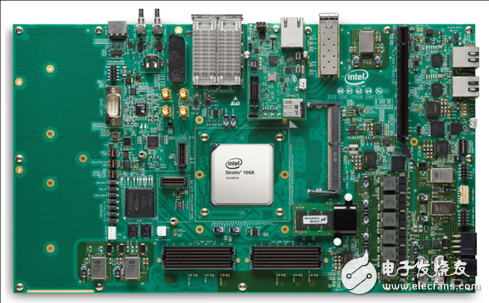

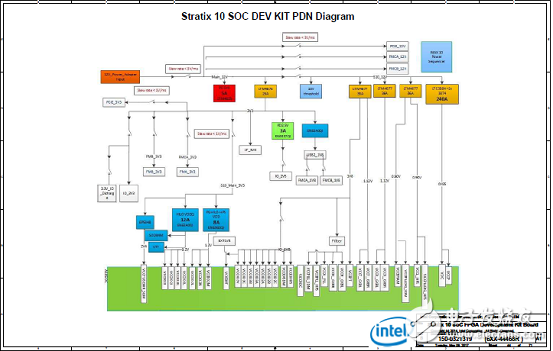

Stratix 10 SoC FPGA开发板

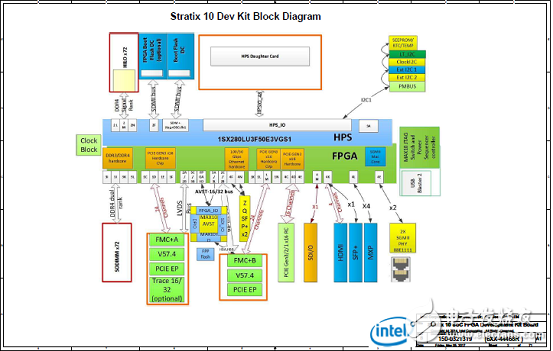

The Intel® Stratix® 10 SoC Development Kit offers a quick and simple approach for developing custom ARM* processor-based SoC designs. The Stratix 10 SoCs offer full software compatibility with previous generation SoCs, a broad ecosystem of ARM software and tools, and the enhanced FPGA and digital signal processing (DSP) hardware design flow.

The Intel Stratix 10 SoC development board provides a hardware platform for developing and prototyping low-power, high-performance and logic-intensive designs using Intel Stratix 10 SoC. The board provides a wide range of peripherals and memory interfaces to facilitate the development of Intel Stratix 10 SoC designs.

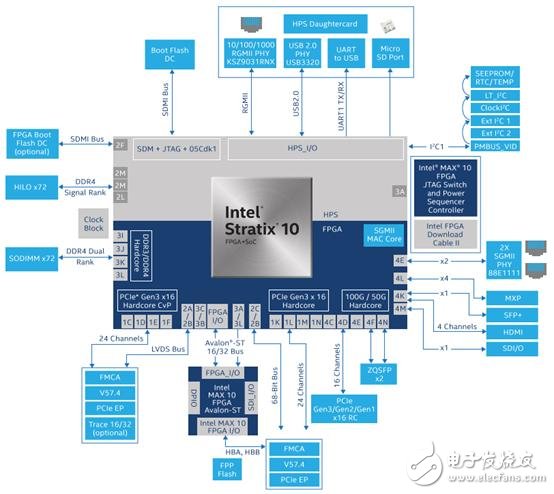

图2. Stratix 10 SoC FPGA开发板框图

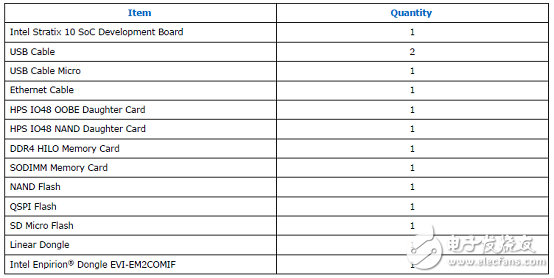

Stratix 10 SoC FPGA开发板包括:

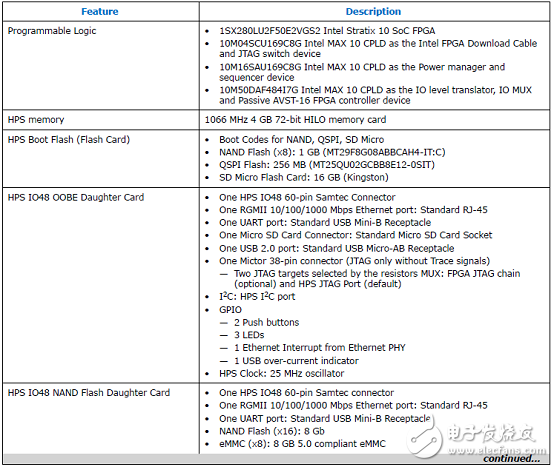

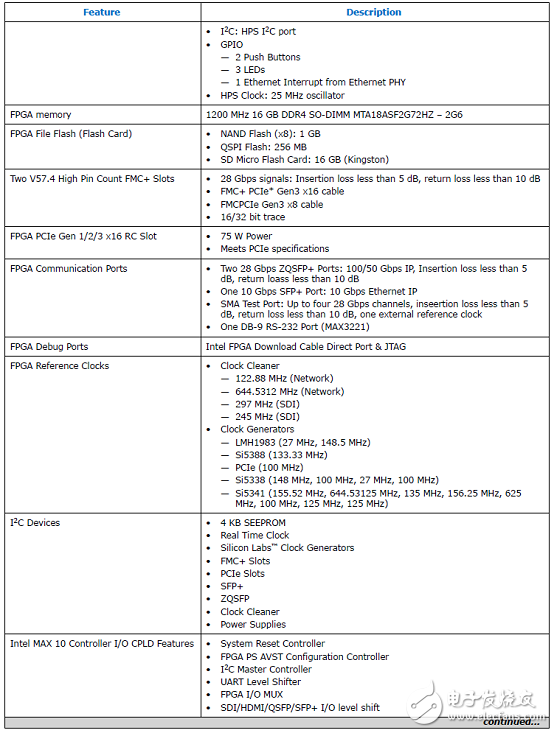

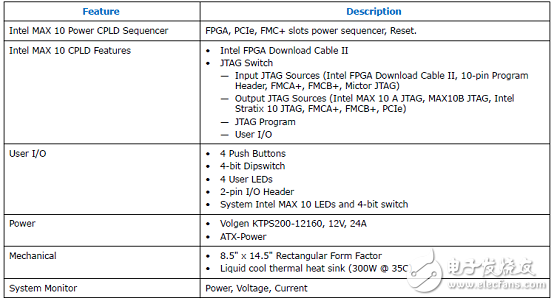

Stratix 10 SoC FPGA开发板主要特性:

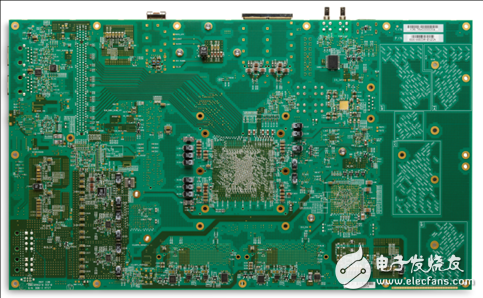

图3. Stratix 10 SoC FPGA开发板外形图(正面)

图4. Stratix 10 SoC FPGA开发板外形图(背面)

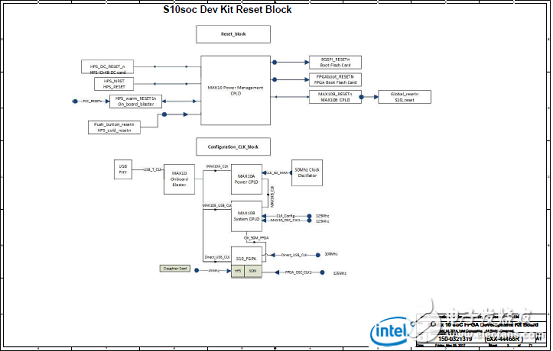

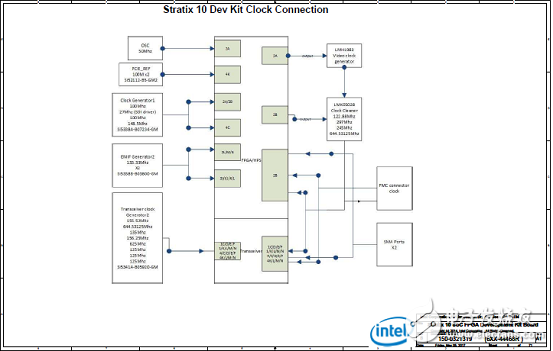

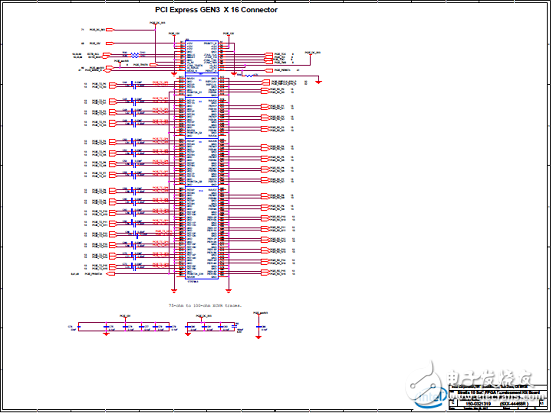

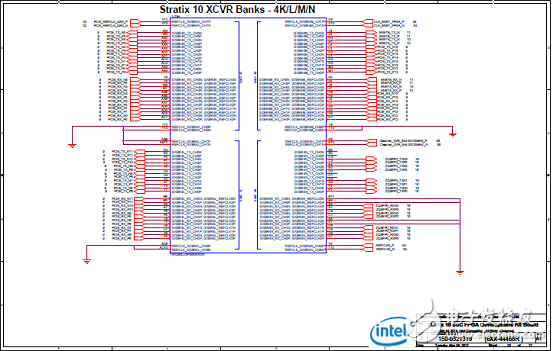

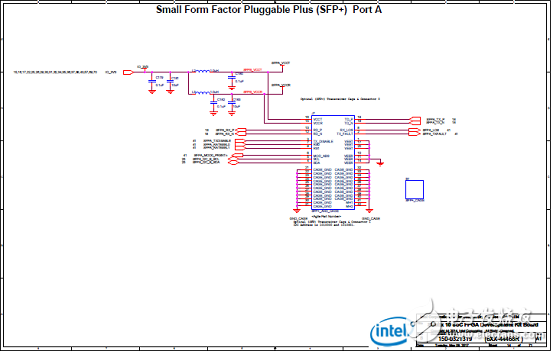

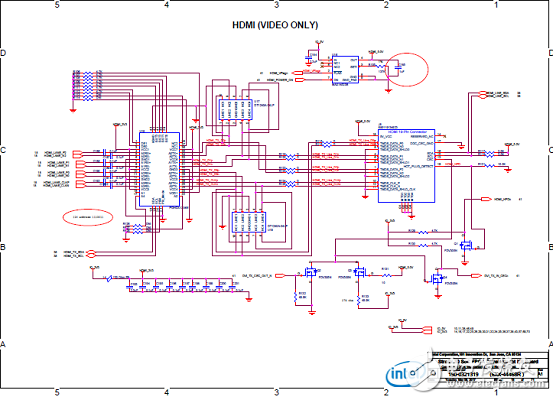

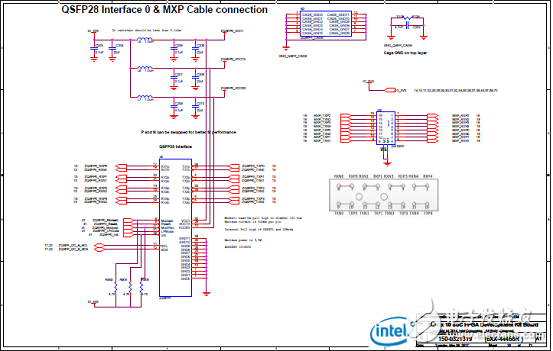

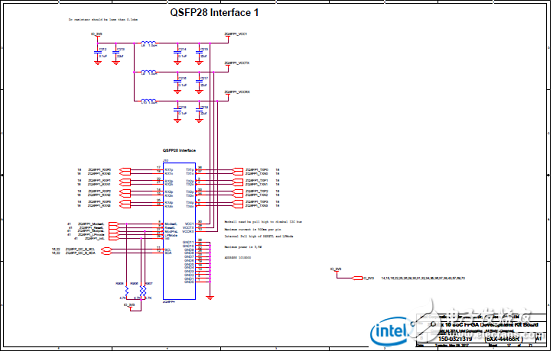

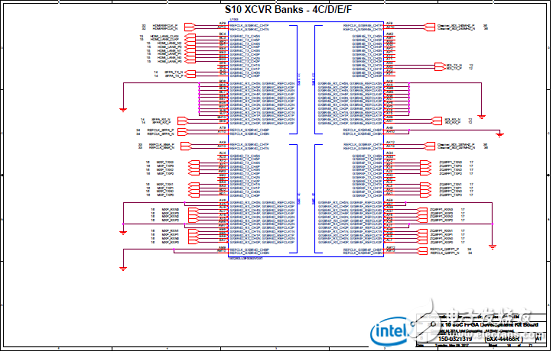

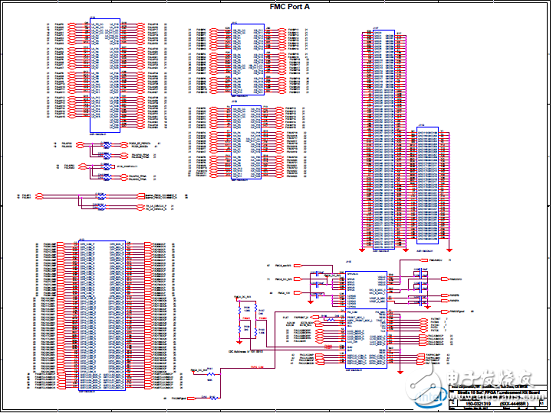

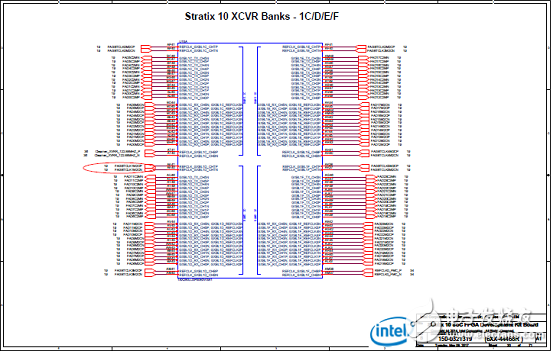

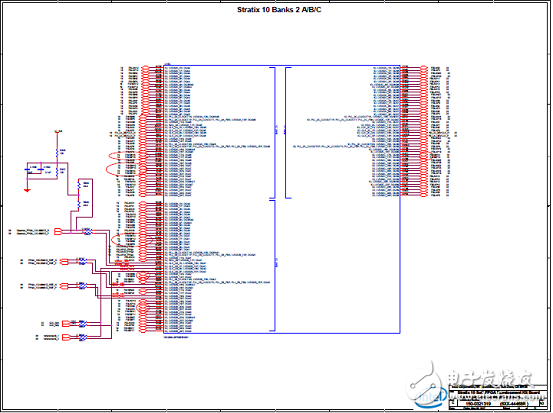

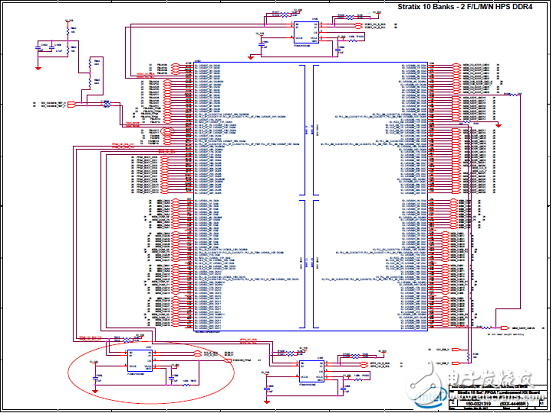

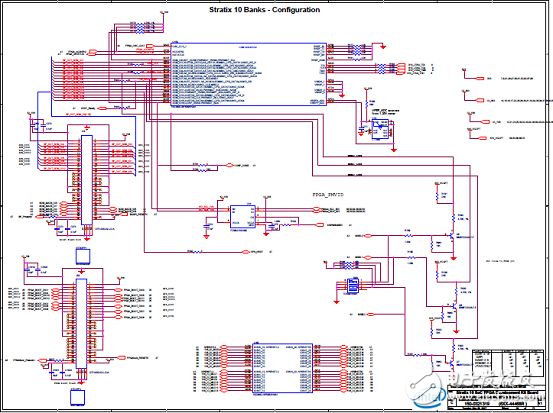

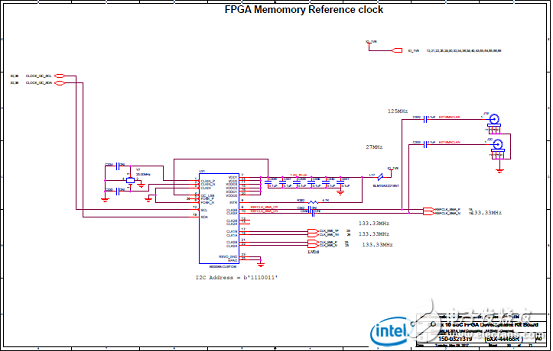

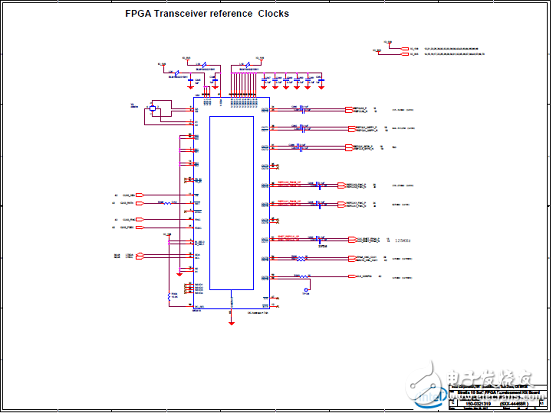

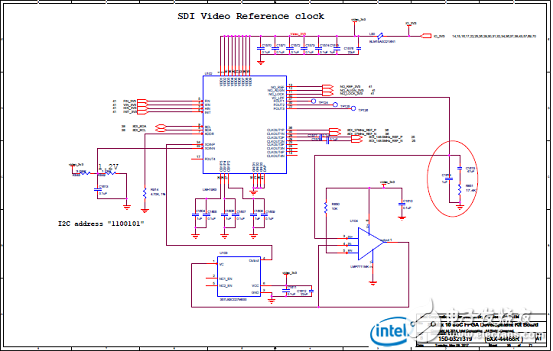

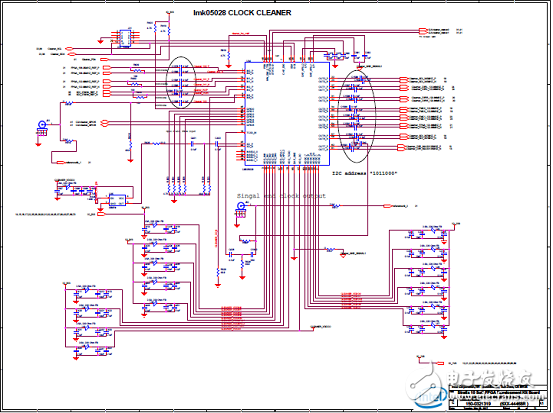

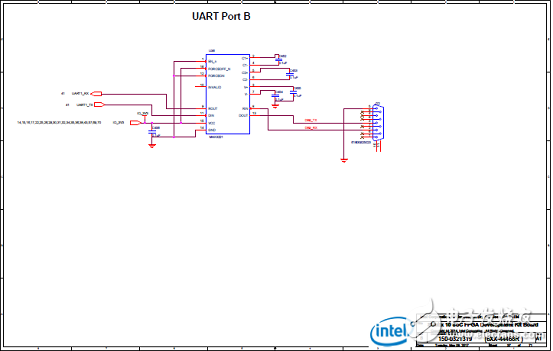

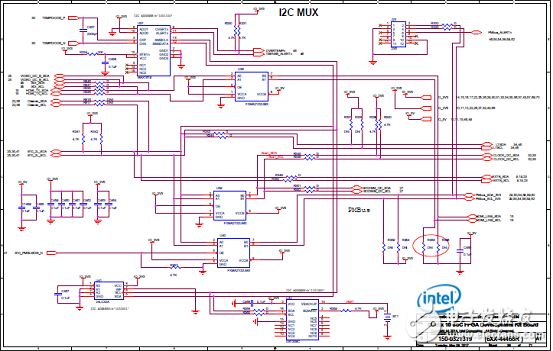

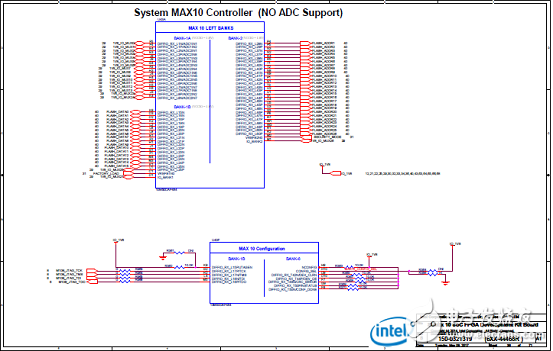

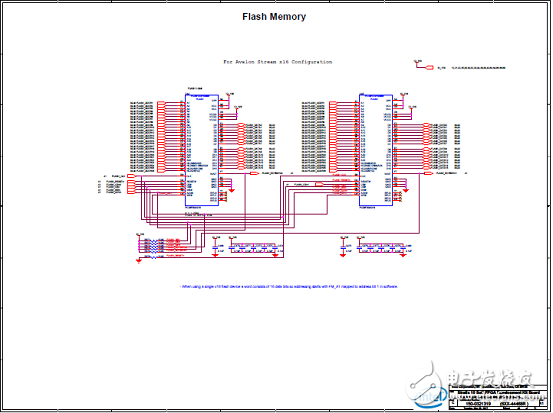

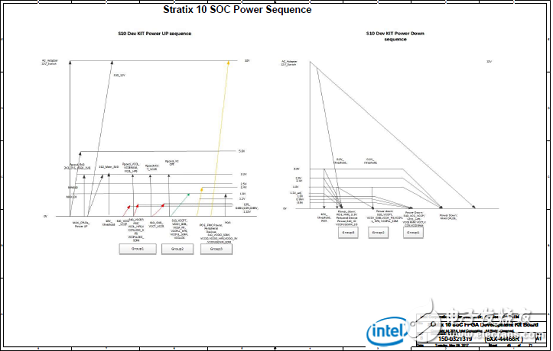

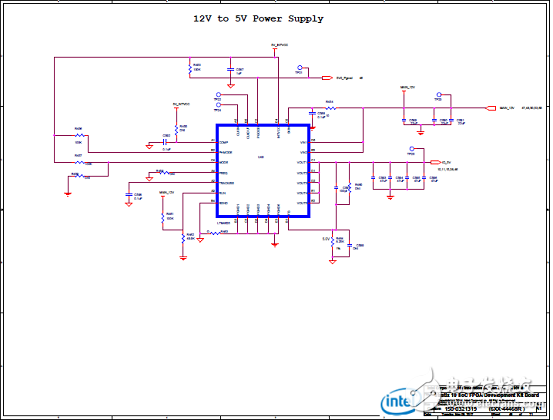

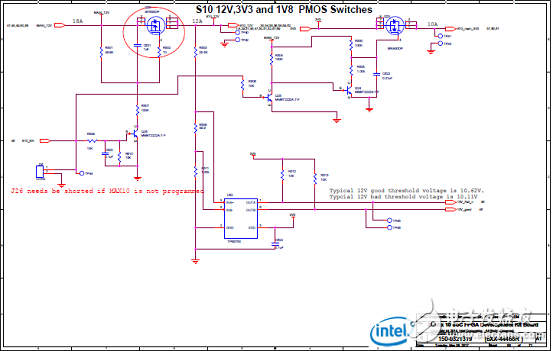

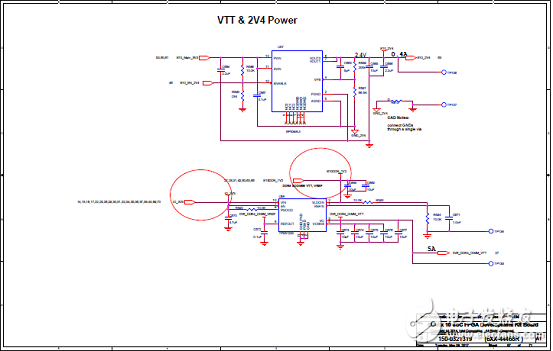

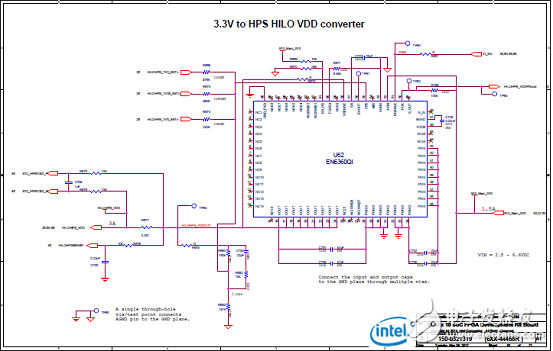

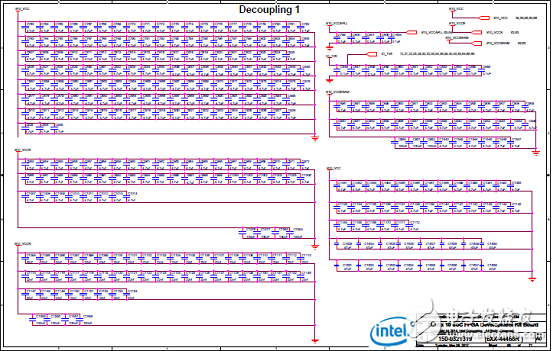

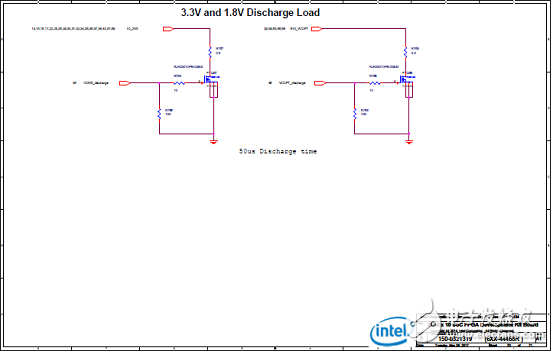

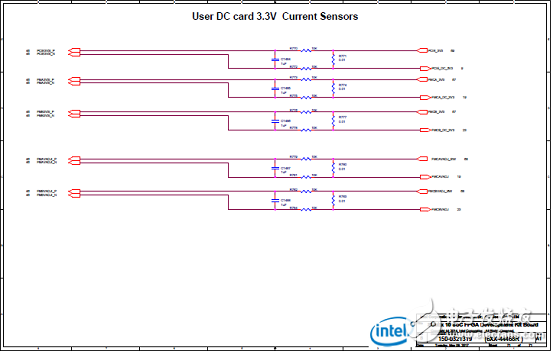

图5. Stratix 10 SoC FPGA开发板电路图(1)

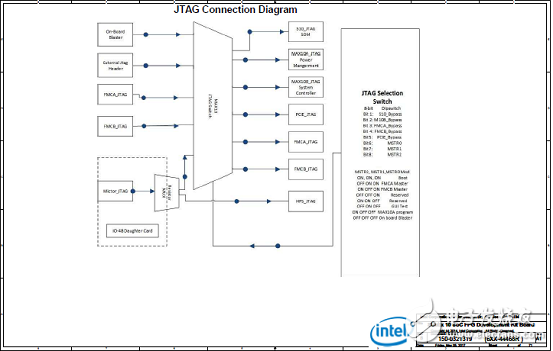

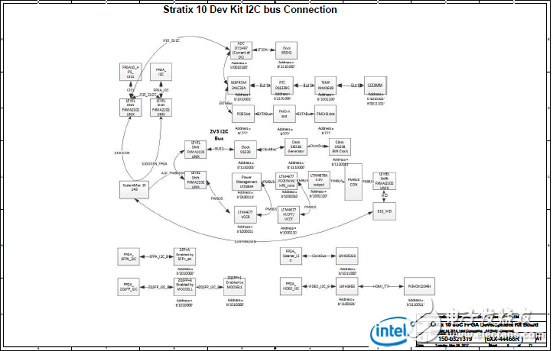

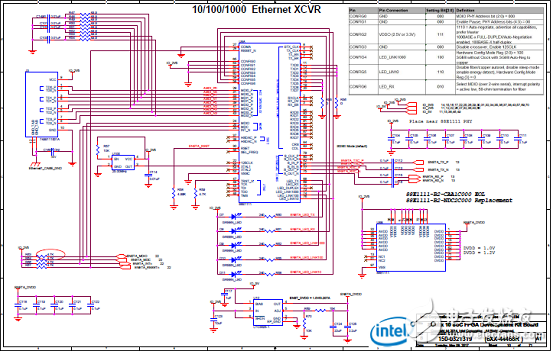

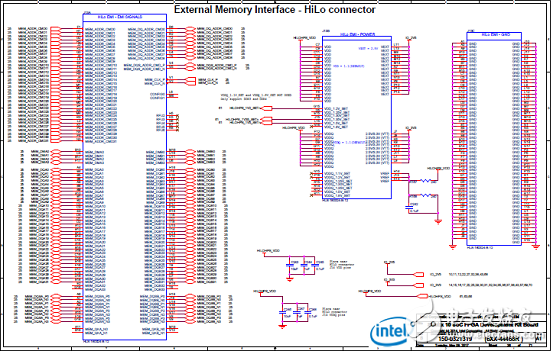

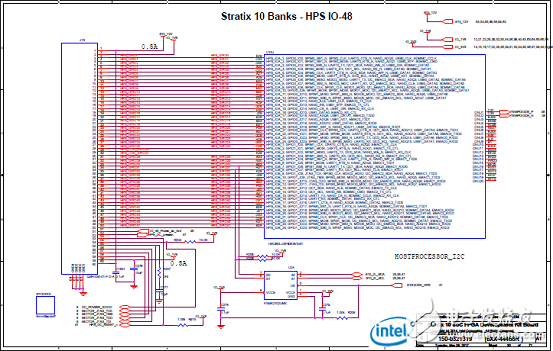

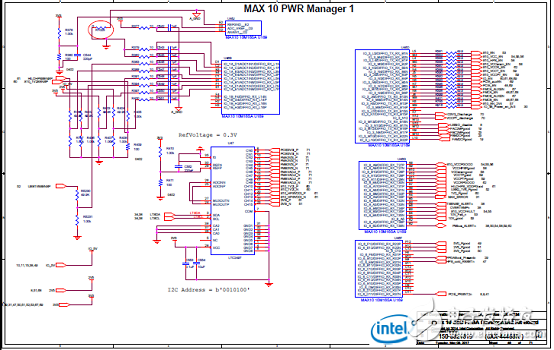

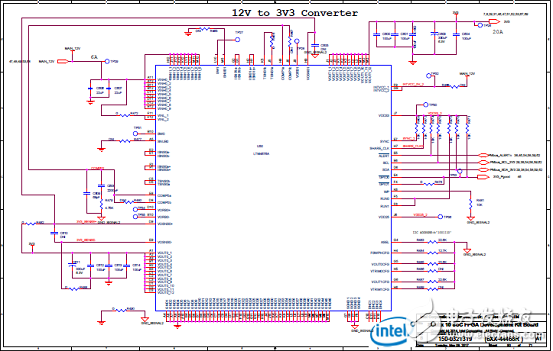

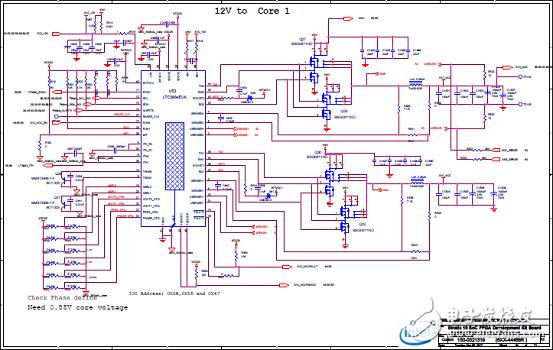

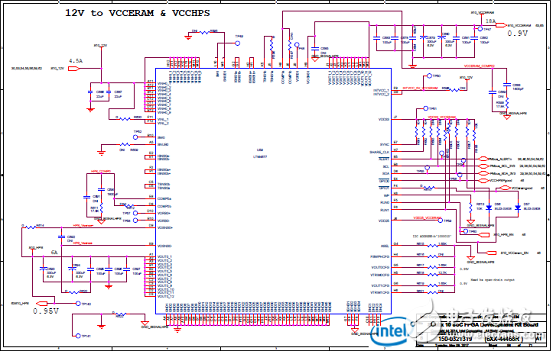

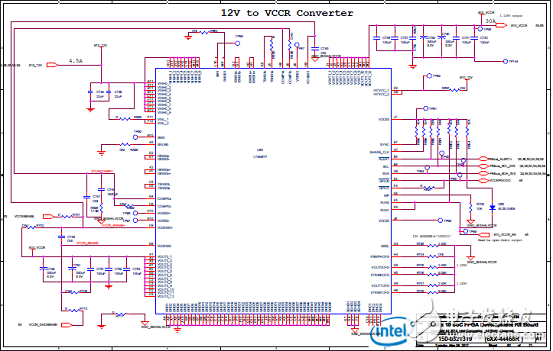

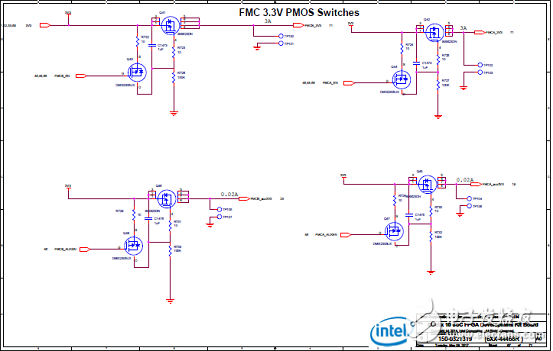

图6. Stratix 10 SoC FPGA开发板电路图(2)

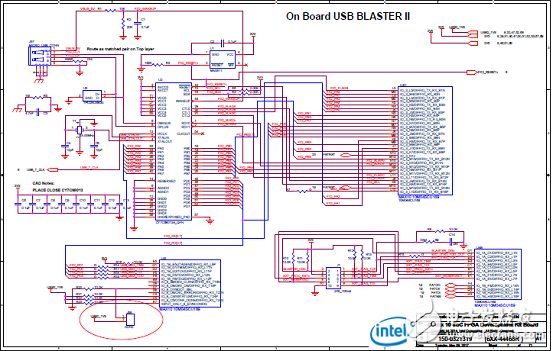

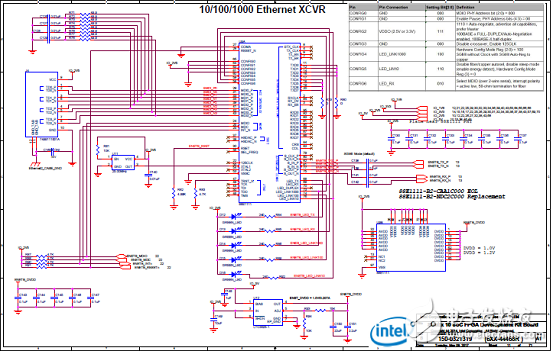

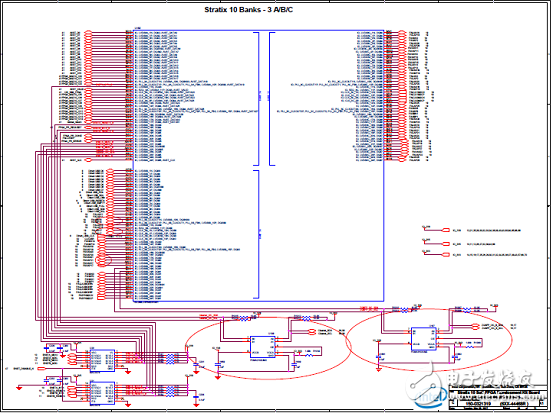

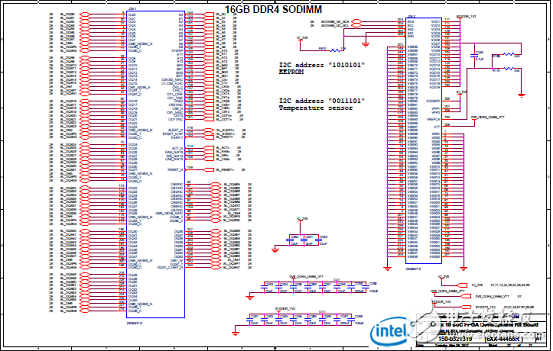

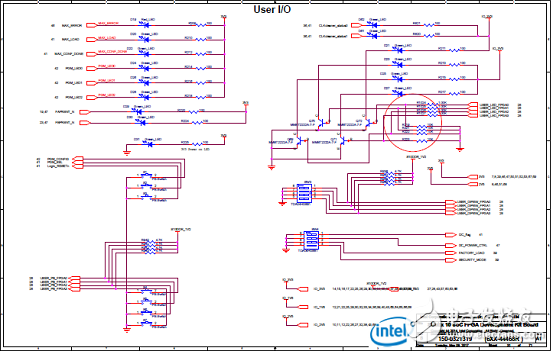

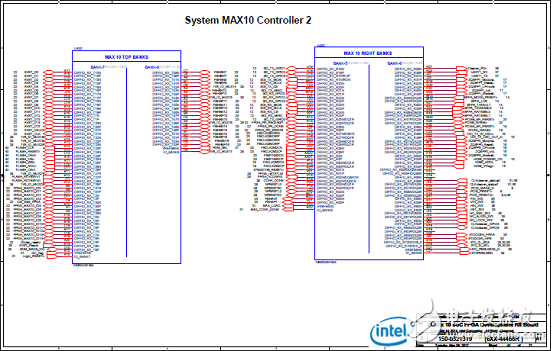

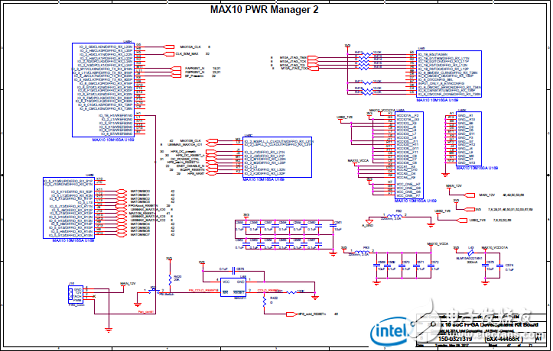

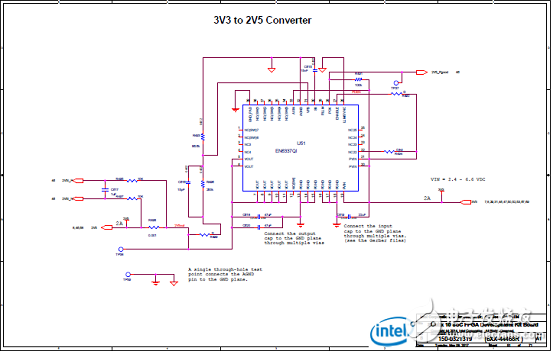

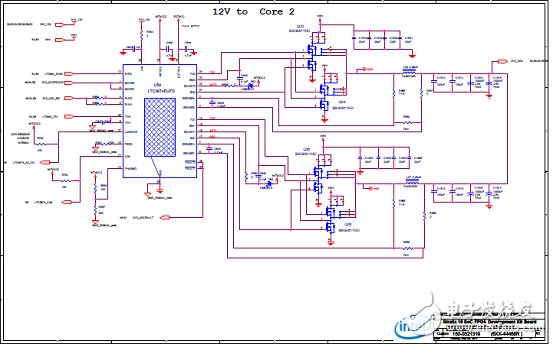

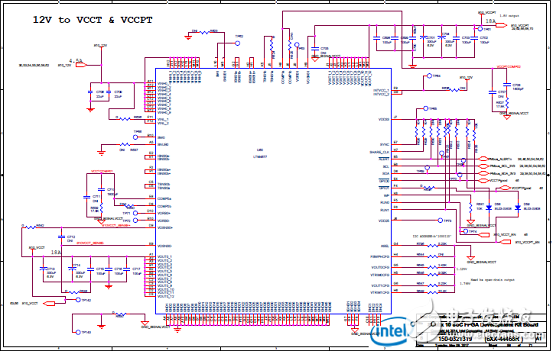

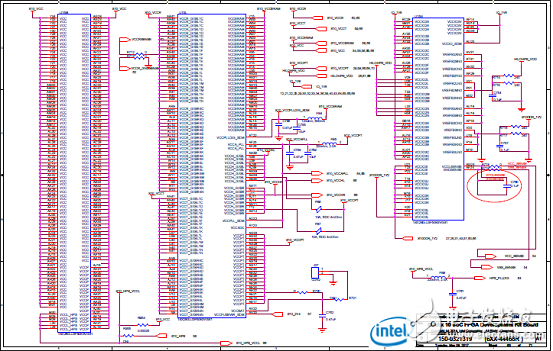

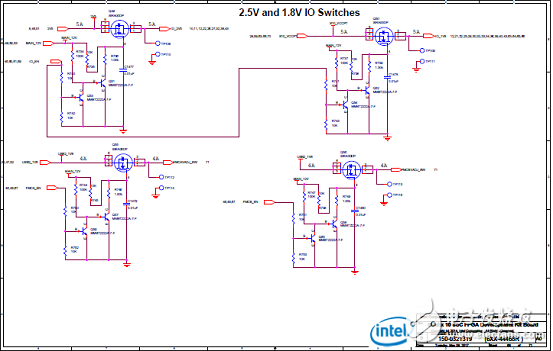

图7. Stratix 10 SoC FPGA开发板电路图(3)

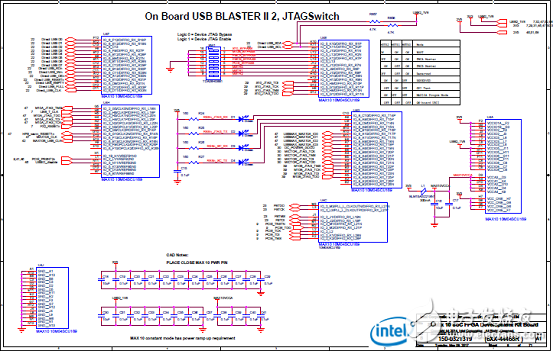

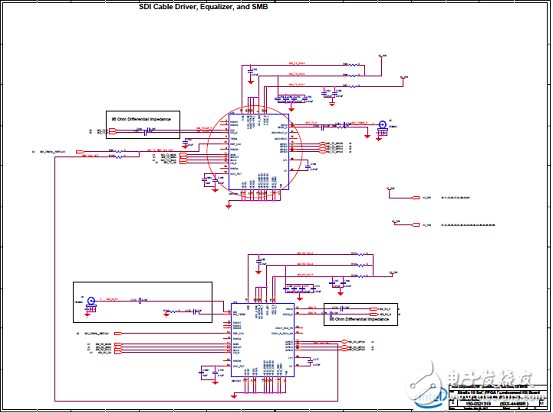

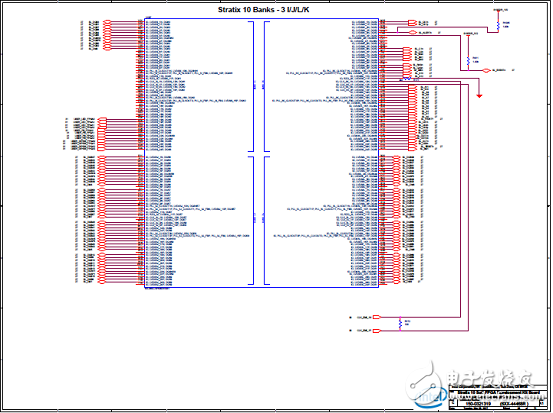

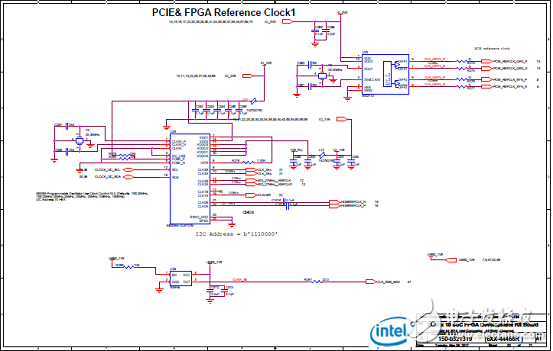

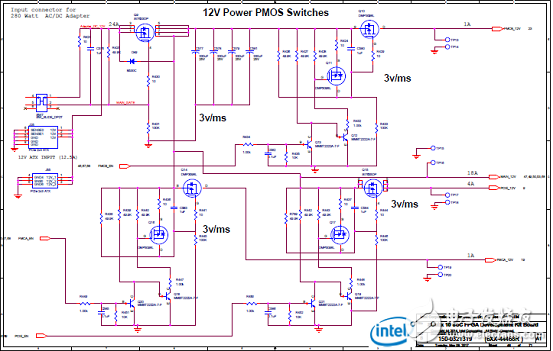

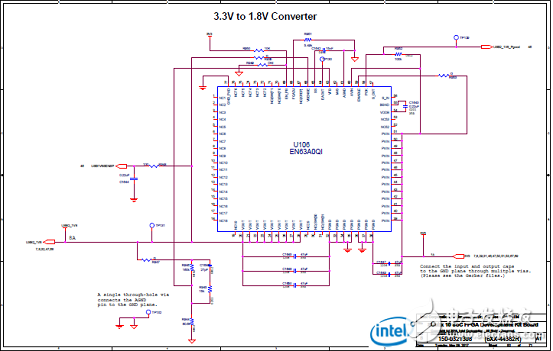

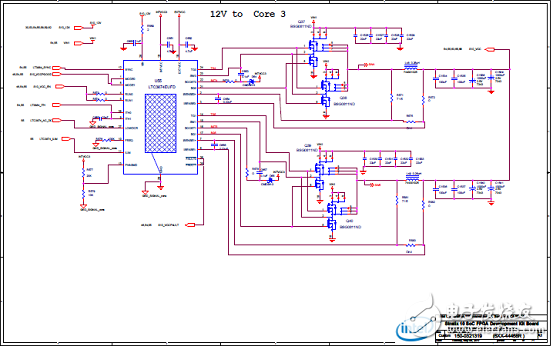

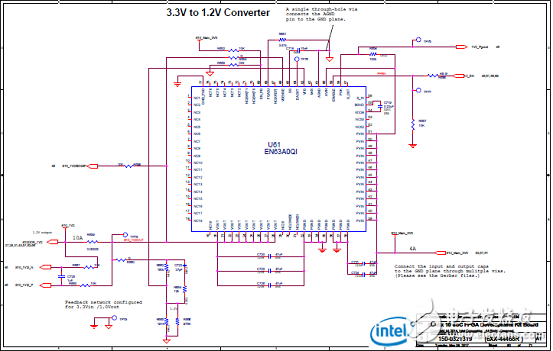

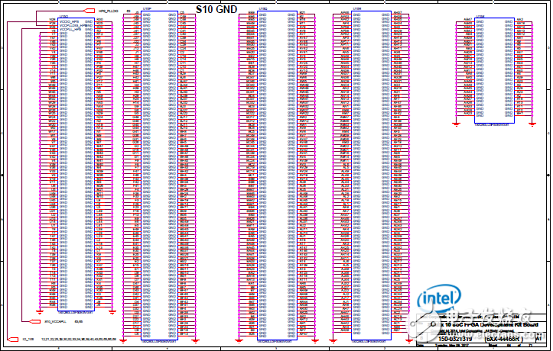

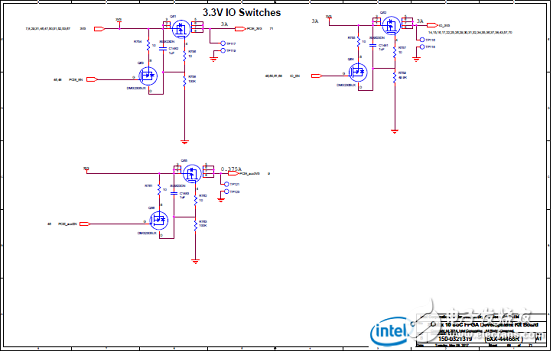

图8. Stratix 10 SoC FPGA开发板电路图(4)

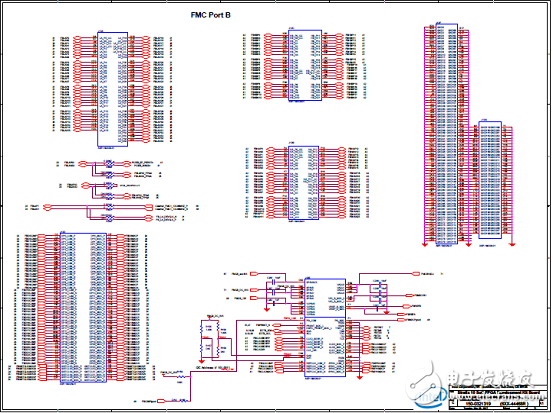

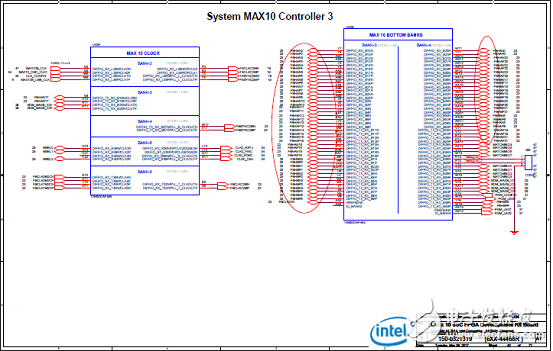

图9. Stratix 10 SoC FPGA开发板电路图(5)

图10. Stratix 10 SoC FPGA开发板电路图(6)

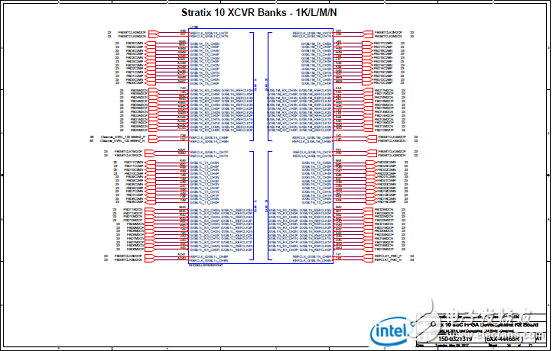

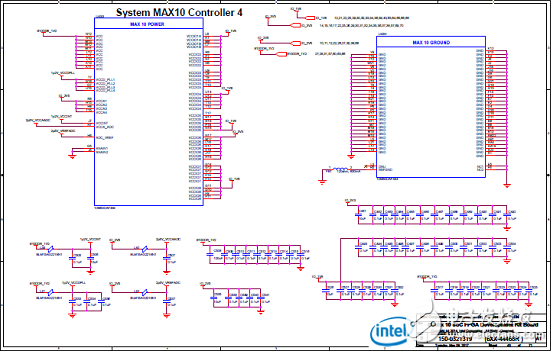

图11. Stratix 10 SoC FPGA开发板电路图(7)

图12. Stratix 10 SoC FPGA开发板电路图(8)

图13. Stratix 10 SoC FPGA开发板电路图(9)

图14. Stratix 10 SoC FPGA开发板电路图(10)

图15. Stratix 10 SoC FPGA开发板电路图(11)

图16. Stratix 10 SoC FPGA开发板电路图(12)

图17. Stratix 10 SoC FPGA开发板电路图(13)

图18. Stratix 10 SoC FPGA开发板电路图(14)

图19. Stratix 10 SoC FPGA开发板电路图(15)

图20. Stratix 10 SoC FPGA开发板电路图(16)

图21. Stratix 10 SoC FPGA开发板电路图(17)

图22. Stratix 10 SoC FPGA开发板电路图(18)

图23. Stratix 10 SoC FPGA开发板电路图(19)

图24. Stratix 10 SoC FPGA开发板电路图(20)

图25. Stratix 10 SoC FPGA开发板电路图(21)

图26. Stratix 10 SoC FPGA开发板电路图(22)

图27. Stratix 10 SoC FPGA开发板电路图(23)

图28. Stratix 10 SoC FPGA开发板电路图(24)

图29. Stratix 10 SoC FPGA开发板电路图(25)

图30. Stratix 10 SoC FPGA开发板电路图(26)

图31. Stratix 10 SoC FPGA开发板电路图(27)

图32. Stratix 10 SoC FPGA开发板电路图(28)

图33. Stratix 10 SoC FPGA开发板电路图(29)

图34. Stratix 10 SoC FPGA开发板电路图(30)

图35. Stratix 10 SoC FPGA开发板电路图(31)

图36. Stratix 10 SoC FPGA开发板电路图(32)

图37. Stratix 10 SoC FPGA开发板电路图(33)

图38. Stratix 10 SoC FPGA开发板电路图(34)

图39. Stratix 10 SoC FPGA开发板电路图(35)

图40. Stratix 10 SoC FPGA开发板电路图(36)

图41. Stratix 10 SoC FPGA开发板电路图(37)

图42. Stratix 10 SoC FPGA开发板电路图(38)

图43. Stratix 10 SoC FPGA开发板电路图(39)

图44. Stratix 10 SoC FPGA开发板电路图(40)

图45. Stratix 10 SoC FPGA开发板电路图(41)

图46. Stratix 10 SoC FPGA开发板电路图(42)

图47. Stratix 10 SoC FPGA开发板电路图(43)

图48. Stratix 10 SoC FPGA开发板电路图(44)

图49. Stratix 10 SoC FPGA开发板电路图(45)

图50. Stratix 10 SoC FPGA开发板电路图(46)

图51. Stratix 10 SoC FPGA开发板电路图(47)

图52. Stratix 10 SoC FPGA开发板电路图(48)

图53. Stratix 10 SoC FPGA开发板电路图(49)

图54. Stratix 10 SoC FPGA开发板电路图(50)

图55. Stratix 10 SoC FPGA开发板电路图(51)

图56. Stratix 10 SoC FPGA开发板电路图(52)

图57. Stratix 10 SoC FPGA开发板电路图(53)

图58. Stratix 10 SoC FPGA开发板电路图(54)

图59. Stratix 10 SoC FPGA开发板电路图(55)

图60. Stratix 10 SoC FPGA开发板电路图(56)

图60. Stratix 10 SoC FPGA开发板电路图(56)

图61. Stratix 10 SoC FPGA开发板电路图(57)

图62. Stratix 10 SoC FPGA开发板电路图(58)

图63. Stratix 10 SoC FPGA开发板电路图(59)

图64. Stratix 10 SoC FPGA开发板电路图(60)

图65. Stratix 10 SoC FPGA开发板电路图(61)

图66. Stratix 10 SoC FPGA开发板电路图(62)

图67. Stratix 10 SoC FPGA开发板电路图(63)

图68. Stratix 10 SoC FPGA开发板电路图(64)

图69. Stratix 10 SoC FPGA开发板电路图(65)

图70. Stratix 10 SoC FPGA开发板电路图(66)

图71. Stratix 10 SoC FPGA开发板电路图(67)

图72. Stratix 10 SoC FPGA开发板电路图(68)

图73. Stratix 10 SoC FPGA开发板电路图(69)

-

英特尔发布全球最大容量的全新Stratix 10 GX 10M FPGA2019-11-06 6460

-

Altera Stratix V GX FPGA开发板电路图2012-08-13 6569

-

MAX 10 FPGA的特性2019-07-01 5652

-

Stratix器件的主要特性是什么? 其典型应用有哪些?2021-04-30 1548

-

Stratix 10 MX FPGA是什么?Stratix 10 MX FPGA有哪些功能?2021-07-09 2151

-

fpga开发板电路图2012-04-19 2709

-

Altera公司 Stratix V GX FPGA开发板电路图2012-08-10 1630

-

Altera全球同步推出10代FPGA和SoC2013-06-13 2797

-

Altera助推客户启动14 nm Stratix 10 FPGA和SoC设计2014-08-07 1110

-

基于Arria 10 SoC FPGA的高性能低成本解决方案2018-06-16 11884

-

Altera® MAX® 10 FPGA介绍(特性、优势、电路图)2018-05-22 6426

-

Stratix 10 FPGA和SoC体系结构和产品细节公布,将云时代的网络通信技术推向了又一个巅峰2018-08-23 1703

-

采用StratixⅡ FPGA器件提高加法树性能并实现设计2020-03-03 1822

-

全球最大容量FPGA——英特尔STRATIX 10 GX 10M2023-03-14 1454

-

英特尔Stratix 10 GX 10M FPGA原型设计系统2023-03-17 1194

全部0条评论

快来发表一下你的评论吧 !