为什么我选择VHDL入门

描述

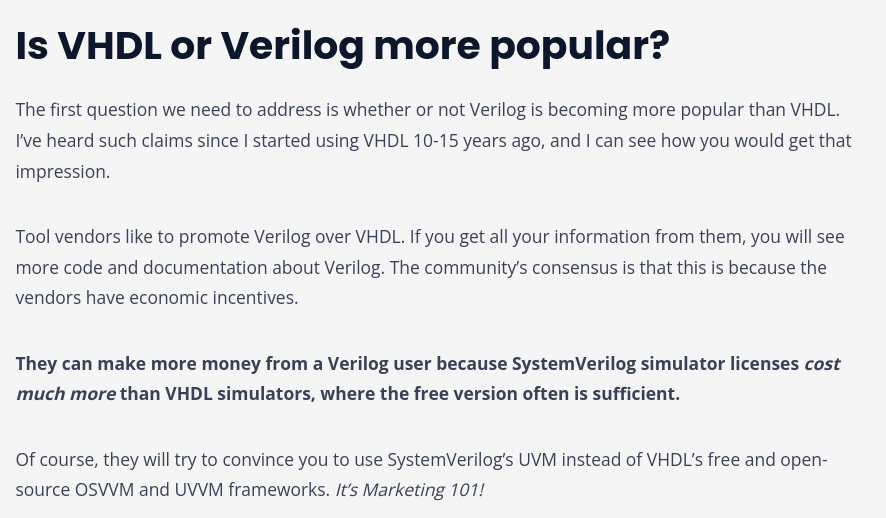

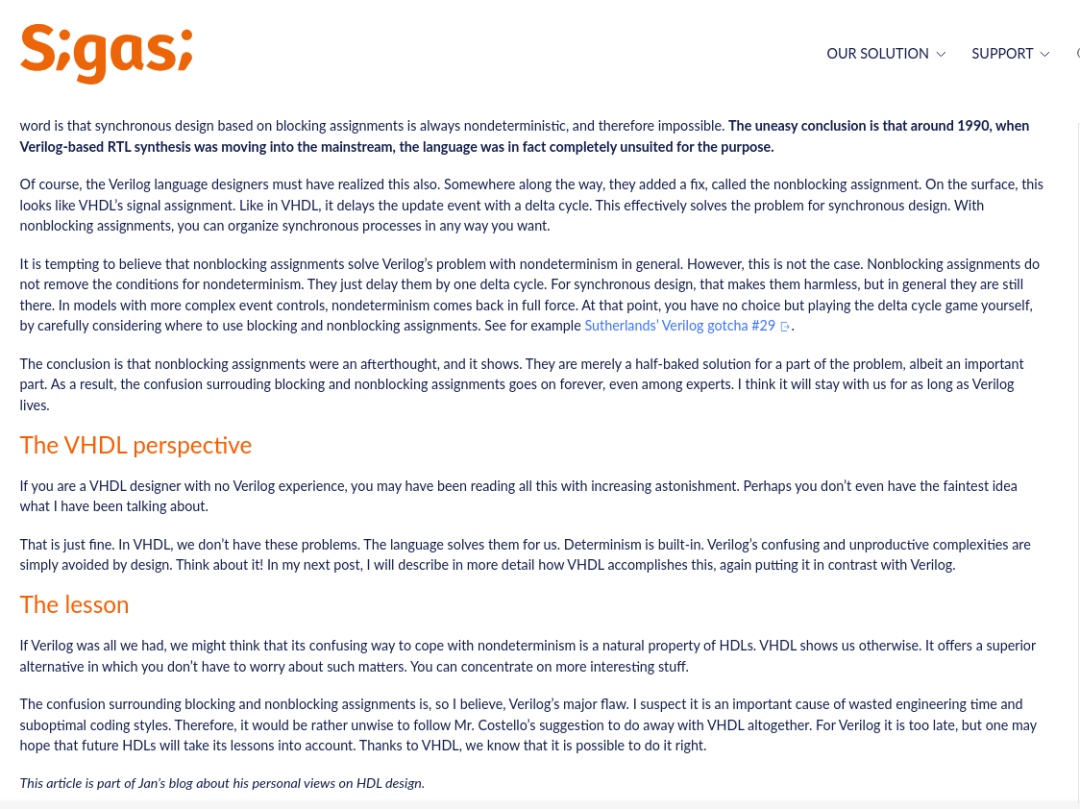

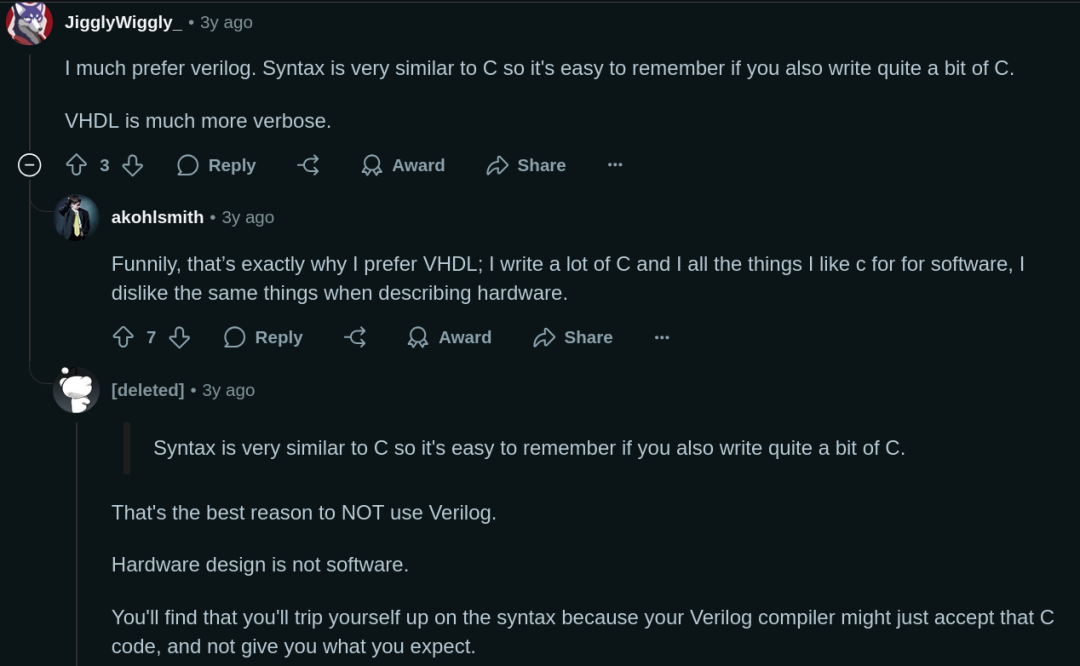

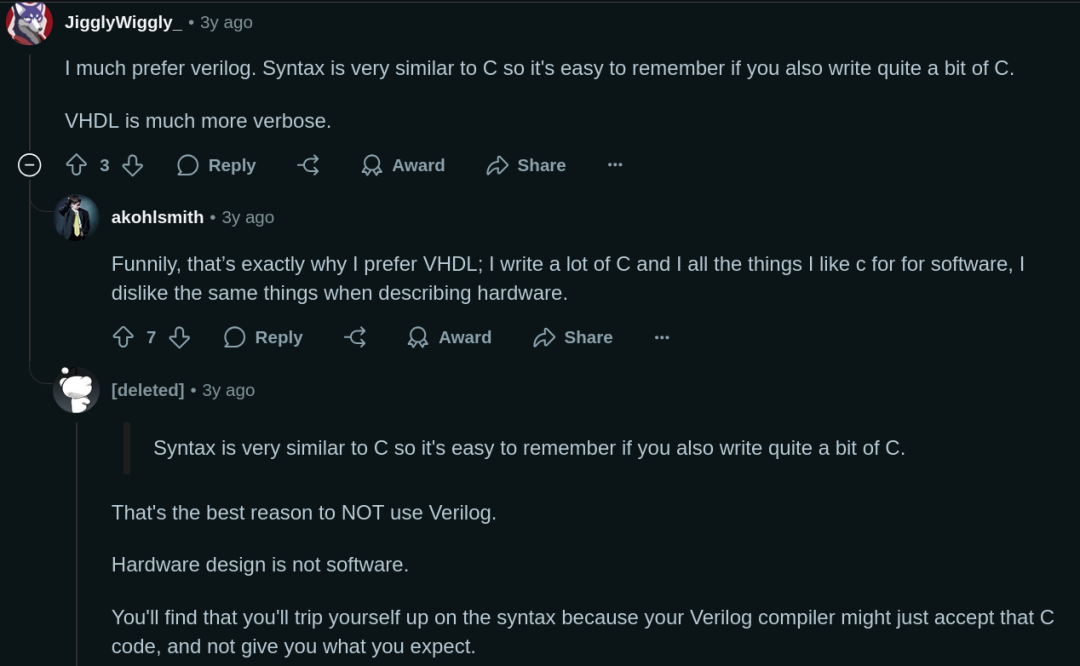

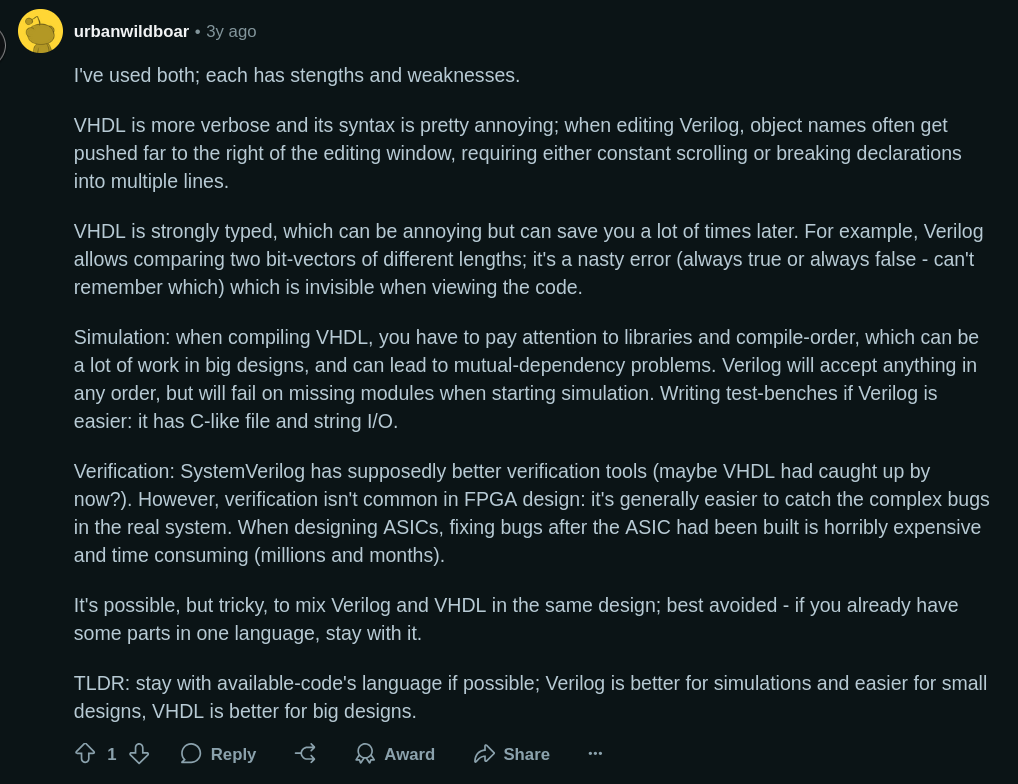

在群里交流提问的时候,大家总是惊讶并疑惑:为什么我要选择 VHDL入门?因为好像 99% 搞 FPGA 开发的人都在用 Verilog。我的选择,是通过网上搜索的讨论而做出的,为了留存,我这里水一篇。从长期来看,两个语言大概率都要学一下;但是从初学角度而言,总要选择一个入门语言。根据网上的信息,总结对比结论:Verilog 的优势:1. Verilog 语法接近C,学习容易;VHDL上手困难,语法繁琐。2. Verilog 是弱类型;VHDL 是强类型。2. 美国的公司主要使用 Verilog,使用广泛,工作岗位更多;美国的军工和欧洲用 VHDL 更多一些。3. 学会了 Verilog 之后,转向 SystemVerilog 更容易,这个是很多人(包括UP主老石的观点)更有前途的 HDL。4. 因为用的人多,所以学习的资料,教学书籍使用 Verilog 的明显比 VHDL 更多。VHDL的优势:1. VHDL 是强类型; Verilog 是弱类型。强类型是缺点是因为增加了代码编写的复杂度;是优势是因为更不容易写错误的代码。2. VHDL 是非常强的确定性,而 Verilog 有时候是非确定性的。(https://www.sigasi.com/opinion/jan/verilogs-major-flaw/)3. VHDL 提供更多的类型定义(同时导致代码繁琐),verilog 只提供少量的类型。4. 学习 VHDL,更能学习数字电路的基础(而学 verilog 只是可以更快的点灯,这是下面一个人的观点)5. 因为VHDL的强类型和确定性,在分析和综合过程中,VHDL 能检查出更多的逻辑错误。 Verilog 更容易接受带有潜在问题的代码。所以我选择 VHDL 的原因是:我是初学者,需要编译器给我更多的指导避免潜在的错误;需要同步学习更多数字电路逻辑的知识;使得代码更具结构性;编写代码浪费的时间其实并不是最重要的,测试和调试代码逻辑才是更耗时的部分,所以如果可以通过增加一些编写的时间,而大幅缩小测试调试的时间,是绝对值得的(如同 Rust 对 C/C++)。观点截图

支持 Verilog 的观点

支持 Verilog 的观点

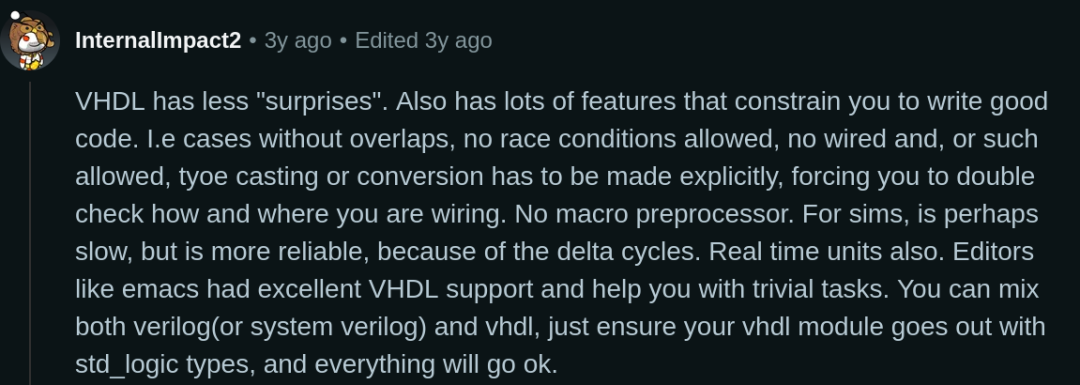

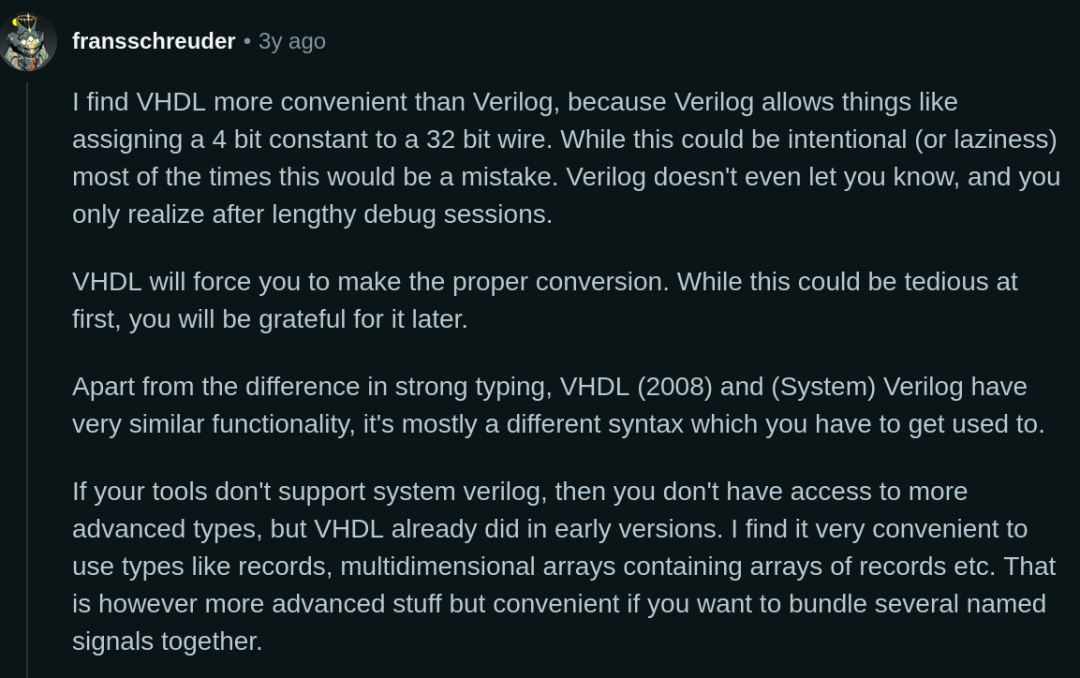

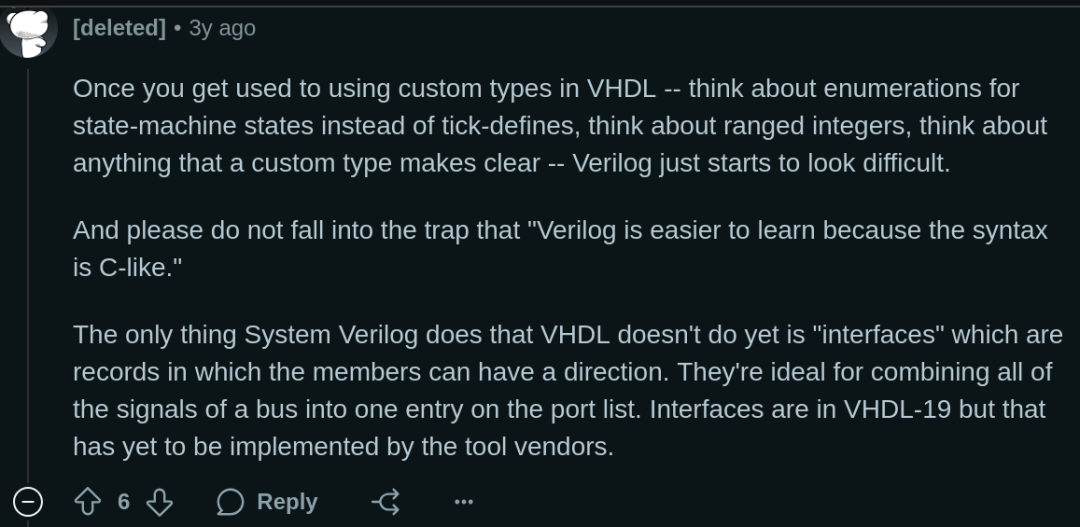

支持 VHDL 的观点

支持 VHDL 的观点

https://vhdlwhiz.com/should-i-learn-vhdl-if-verilog-is-becoming-more-popular/

https://www.sigasi.com/opinion/jan/verilogs-major-flaw/

https://digilent.com/blog/verilog-vs-vhdl/?srsltid=AfmBOopW22oVlEJQsfh9kTQePkD-7TUmSL58-S9MFdGj_i25Z1Kb20I3

https://www.fpga4student.com/2017/08/verilog-vs-vhdl-explain-by-example.html

支持 Verilog 的观点

支持 Verilog 的观点

支持 VHDL 的观点

支持 VHDL 的观点

https://www.reddit.com/r/FPGA/comments/upcaj5/verilog_vs_vhdl/

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MaxplusII-VHDL语言入门2008-07-24 7253

-

VHDL入门2012-08-16 2293

-

VHDL入门教程2017-02-05 3788

-

如何找到Spartan 3A入门套件中的vhdl代码2019-07-17 1549

-

VHDL语法入门2020-05-11 1260

-

数字电路EDA入门——VHDL程序实例集2009-07-20 809

-

数字电池EDA入门之VHDL程序实现集2009-12-07 635

-

VHDL语言快速入门必读2015-10-29 776

-

VHDL实用教程2015-11-02 478

-

VHDL入门--EDA资料2016-11-21 631

-

PFGA与VHDL快速工程实践从入门到提高2016-11-10 1151

-

vhdl例化2016-12-16 709

-

VHDL的基本语法ppt资料2017-05-09 902

-

VHDL硬件描述语言入门教程资料免费下载2019-04-08 1822

-

数字电路EDA入门之VHDL程序实例集2022-04-07 808

全部0条评论

快来发表一下你的评论吧 !