瑞萨RZ T2H更换DDR流程和工具介绍

描述

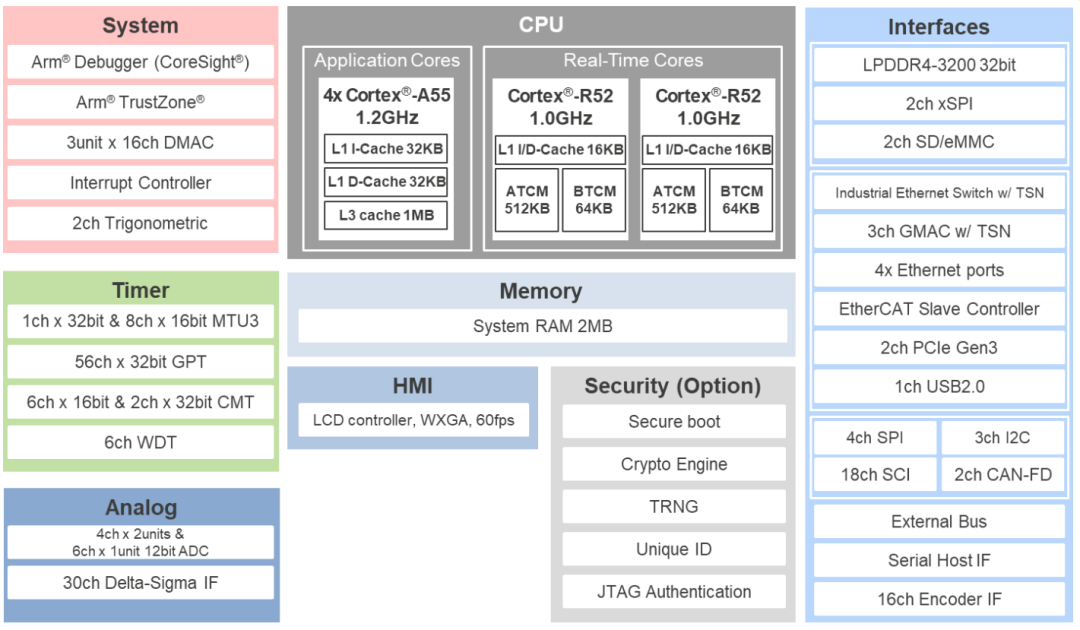

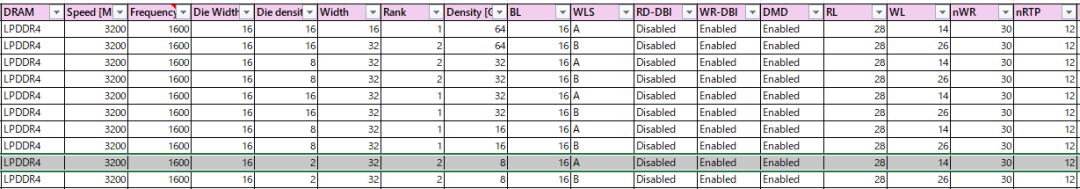

瑞萨RZ T2H是由2个R52核和4个A55核构成。支持LPDDR4,其传输可以达到3.2Gbps(1600 MHZ),总线宽度为32位,两个rank,最大支持64Gb容量。

图RZ T2H框图

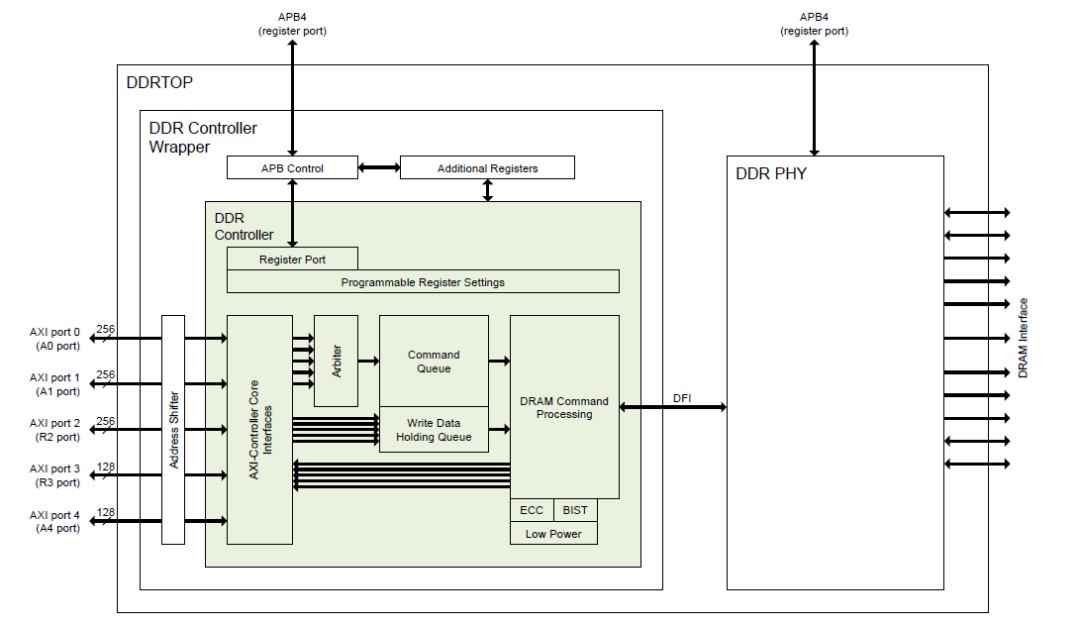

DDR的系统框图

RZ T2H LPDDR4子系统是由MC (Memory Controller)和PHY构成,支持JEDEC标准 JESD209-4D。

其MC功能为:

完全流水线化的指令、读数据和写数据接口,用于连接内存控制器。

高级Bank预取功能,以提高内存吞吐量。

可编程寄存器接口,用于控制内存参数和协议,包括自动预充电(Auto Pre-Charge)。

控制器复位时可对内存进行完全初始化。

支持加权轮询(Weighted Round-Robin)仲裁机制,用于仲裁来自多个端口的请求。

支持ECC(错误校正码)功能,包括单比特和双比特错误报告、单比特错误校正,并支持通过编程方式去除ECC存储。

支持外部DRAM的内建自测试(BIST,Built-In Self Test)。

PHY的功能:

指令总线眼图(Bus Eye)训练,相对于时钟信号CK进行校准。

写入调平(Write Leveling),用于补偿CK-DQS之间的时序偏差(Timing Skew)。

写入训练(Write Training),用于对DQs、DM和DQS进行去偏(Deskew):

基于指令的FIFO读/写(WR/RD),支持用户自定义模式(User Patterns)。

内部DQS时钟树振荡器,用于确定是否需要周期性训练以及所需的训练幅度。

数据总线VREFDQ训练,用于优化写入信号质量。

读取训练(Read Training),用于对DQs、DM和DQS进行去偏:

通过DRAM模式寄存器(Mode Registers)进行DQ位(Bit)去偏训练。

通过DRAM阵列进行DQS对DQ眼中心(Eye Centering)训练。

通过PHY主接口自动执行周期性再训练。

LVSTL(低电压摆幅差分信号)I/O校准 及ODT(终端电阻)校准。

支持软件可控的DQ位和AC位交错(Swizzling),以优化数据传输。

瑞萨提供了一整套的工具,方便客户根据自己的情况选择LPDDR4的物料。

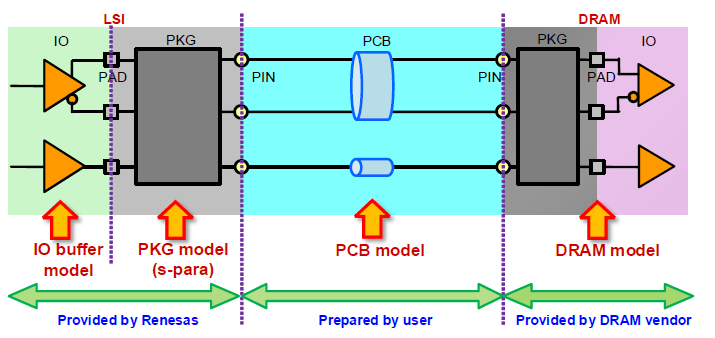

这一套工具,包括PCB设计指导、PCB验证指导、硬件原理图用户指导手册等。瑞萨官网上可以下载到IBIS文件和PKG Model文件,用于客户更换DDR后的仿真工作。

信号完整性模型

瑞萨提供I/O缓冲模型(IO Buffer Model)和封装模型(PKG Model)。用户需要准备PCB模型(PCB Model)。DRAM模型(DRAM Model) 由DRAM厂商提供。

同时,瑞萨提供了非常易用的gen_tool,帮助客户生成新的swizzle文件。

用以生成支持客户选择DDR型号的flash loader,u-boot和Linux内核程序。

以下以某客户将RZ T2H EVB上的美光MT53E2G32D4DE-046WT更换成海力士H54G36AYRVX246为例说明软件适配过程(前提是PCB硬件Layout已经通过了SI/PI测试)

客户将DDR颗粒大小从64Gb换成了8Gb,DQA/DQB的线序也做了调整。

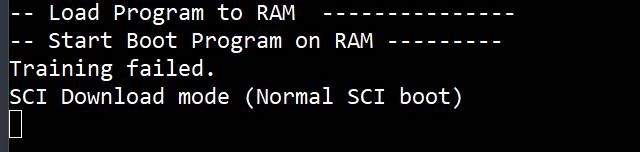

使用默认Flash Loader程序,通过Log可以看出,Training Failed:

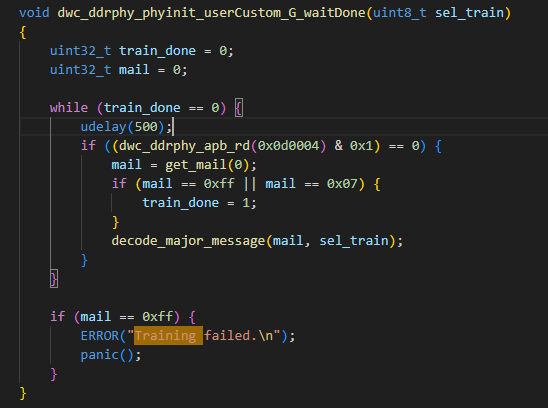

从Flash Loader源代码中发现这个Fail的原因是DDR初始化失败:

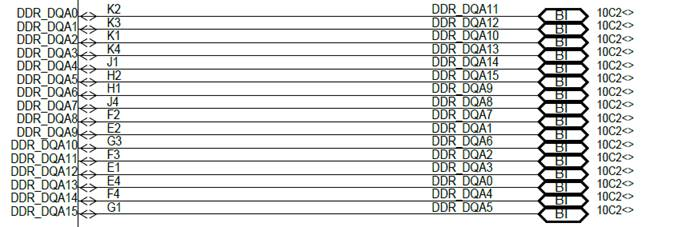

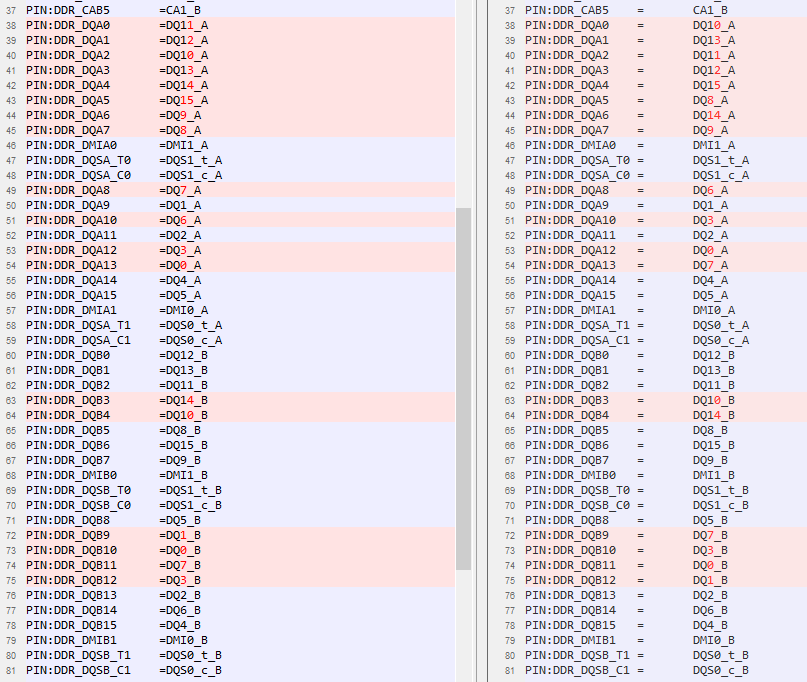

原理图方面,T2H EVB的DQA是:

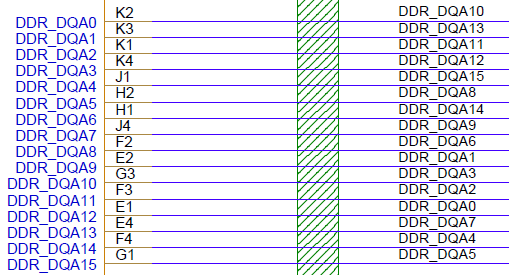

而客户的DQA线序做了调整:

需要使用Renesas的DDR适配工具重新生成适配修改的代码;

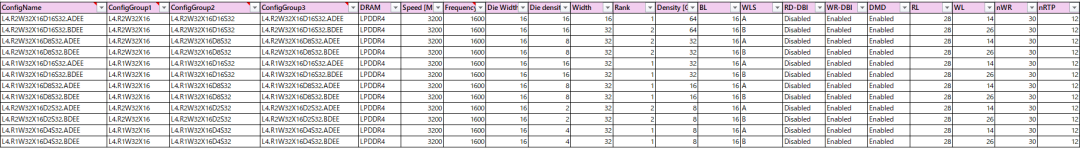

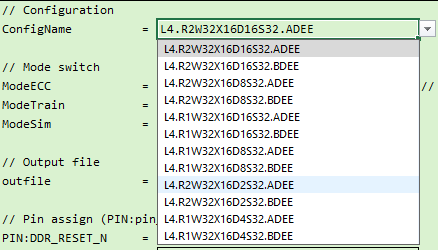

我们在gen_tool中,选择L4.R2W32X16D2S32.ADEE,

即各个参数如下表(浅色的一行):

调整后,更换LPDDR4的差异主要集中在:DQA/DQB,以及DDR的颗粒密度上:

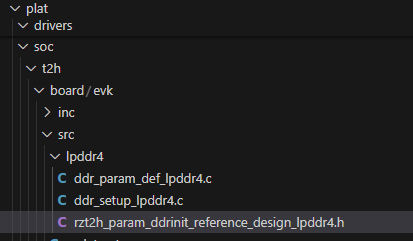

再运行gen_tool,生成rzt2h_param_ddrinit_reference_design_lpddr4.h文件。

将该文件拷贝到/flash_programmer/plat/soc/t2h/board/evk/src/lpddr4/,替换rzt2h_param_ddrinit_reference_design_lpddr4.h文件。

重新编译,得到新的flash loader文件:

*./rzt2_flash_programmer/project/flash-programmer/src/output/HDR NM

*./rzt2_flash_programmer/project/flash-programmer/src/output/Flash_Programmer_SCIF_CR52_RZT2H_EVK.mot

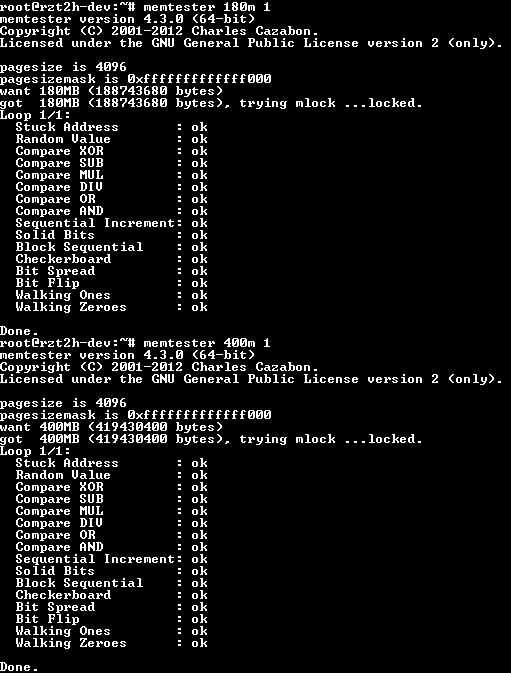

同时,需要在BL2,FIP(trust-firmware-a和uboot)和设备树文件处,修改LPDDR4的驱动,重新用YOCTO构建uboot和内核、dtb文件。运行memtester 180m和memtester 400m验证DDR更换是否成功:

验证完毕,说明DDR更换的软件和硬件都已成功。

简要总结一下更换DDR流程:

1.硬件设计PCB阶段,必须做SI/PI仿真。

2.通过瑞萨提供的工具生成DDR头文件。

3.根据头文件生成flash programmer。

4.生成FIP(包含uboot)文件。如果大小不同,需要修改设备树文件。

RZ T2H完整的软硬件设计规范、参考例程、工具等,请点击下方链接获取更多资料。

-

RZ/T2H和RZ/N2H MPU:工业级应用的高性能之选2026-04-01 165

-

米尔RZ/T2H MPU支持支持多轴实时控制,助力工业以太网2026-03-20 83

-

新品!瑞萨RZ/T2H驱控一体单芯、多轴实时控制,助力工业以太网2026-03-19 677

-

Renesas RZ/T2H 评估板:功能特性与使用指南2025-12-26 1306

-

瑞萨RZ/T2H平台多核异构的应用场景分析2025-12-15 2789

-

瑞萨RZ/T2H PCIe通信的调试方法2025-11-20 6024

-

RZ/T2H MPU数据手册和产品介绍#集成了强大的应用处理能力和精确的实时控制功能2025-05-21 1509

-

瑞萨交流日进行中,米尔演讲-RZ/T2H高性能模组赋能工业产品创新2025-03-13 1101

-

瑞萨电子量产高性能工业设备MPU RZ/T2H2024-12-27 1522

-

瑞萨电子RZ MPU家族精品RZ/N2L产品介绍2024-12-23 1795

-

RZ T2H PCIe裸机程序开发和Linux下的配置介绍2024-12-18 3019

-

工业MPU新标杆,多协议工业以太网+运动控制 - 瑞萨RZ/T2H 新产品2024-12-06 1591

-

瑞萨RZ/T2H新产品量产上市2024-12-04 2307

-

产品详解 | 瑞萨电子RZ/T2L MPU2024-03-21 2378

全部0条评论

快来发表一下你的评论吧 !