基于ADS的接收机码元同步算法实现详细讲解

模拟技术

描述

摘要:数字通信系统中,码元同步对于实现信号的准确判决码元和降低系统误码率起着关键作用。本文介绍了在ADS仿真环境下实现16QAM接收机码元同步算法。采用的定时误差提取算法消除了传统算法在16QAM系统中引起的时钟抖动问题,实现了接收信号和发送信号同步。并对该算法在ADS环境下进行了仿真,仿真结果表明该算法实现了码元同步的功能,并对干扰有较强的抵抗能力。

0 引言

在数字接收机中,为了在抽样判决时刻准确判决发送过来的码元,需要提供一个确定抽样判决时刻的定时脉冲序列。这个定时脉冲序列的重复频率必须与发送的数码脉冲序列一致(即接收、发送双方必须同步,具有相同的主频率),同时在最佳判决时刻对接收码元进行抽样判决。这样的定时脉冲序列称为码元同步。

16QAM(Quadrature Amplitude Modulation)接收机要完成16QAM信号的解调首先要完成码元同步,再通过随后的均衡、载波恢复等模块完成信号的解调。因此码元同步算法的实现是至关重要的一部分。

1 码元定时同步原理及其在ADS中的设计

数字化的解调器中,经过下变频所得的基带信号通过匹配滤波器,然后以时钟周期为Ts的固定采样频率进行采样、量化后进入码元同步环路。

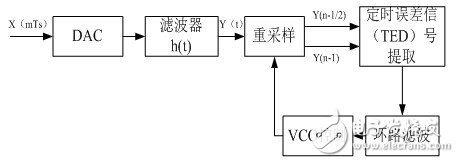

图1 码元同步模块的结构

在论文中,具体采用的定时同步模块如图1所示,它由内插滤波器(由DAC、滤波器和重采样等效实现)、定时误差提取(TED)、环路滤波器以及VCO控制器组成。从图中可看出:信号经过内插后,每个符号内有两个采样点,再进行时钟误差提取,得到的误差信号经过环路滤波器后送给VCO,最后控制内插完成同步。即通过采样点提取时钟控制信号调整采样时钟来达到同步。

下面分别介绍各模块的原理。

1.1 内插滤波器原理

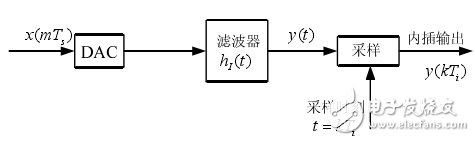

内插滤波器实际上实现的是一个数据的速率转换可以假设它的模型如图2所示。

图2 速率转换

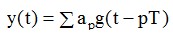

假定接收端固定采样时钟为 ,符号周期为T。内插器接收的信号为

,符号周期为T。内插器接收的信号为 ,通过DAC及滤波器后

,通过DAC及滤波器后 ,得到一个连续时间的输出:

,得到一个连续时间的输出:

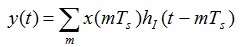

(1-1)

(1-1)

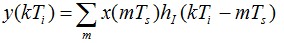

现在,对于y (t),在每个时刻 时对其再次进行采样,其中,k为正整数。T为内插器周期,它与符号周期是同步的。

时对其再次进行采样,其中,k为正整数。T为内插器周期,它与符号周期是同步的。

(1-2)

(1-2)

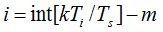

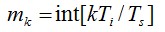

对于上式(5-2),m为输入序列指针,定义滤波器指针为:

(1-3)

(1-3)

同样,定义基本指针为:

(1-4)

(1-4)

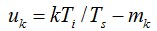

分数间隔为:

(1-5)

(1-5)

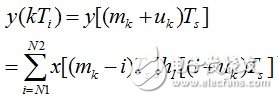

内插公式可以重新写为:

(1-6)

式(1-6)为数字内插滤波器的基本方程。

引入参数 ,

, 是有实际意义的。它们表示了

是有实际意义的。它们表示了 ,

, 之间的调整关系。其中,

之间的调整关系。其中,  决定了计算第k个内插值

决定了计算第k个内插值 的N=N2-N1+1个信号样值,

的N=N2-N1+1个信号样值, 指示了内插估值点,并决定用来计算内插值

指示了内插估值点,并决定用来计算内插值 的N个插值滤波器脉冲响应样值。一般情况下,

的N个插值滤波器脉冲响应样值。一般情况下, 是个无理数且对每次内插都是变化的,直到定时稳定时,

是个无理数且对每次内插都是变化的,直到定时稳定时, 将稳定在某一个定值上。

将稳定在某一个定值上。

1.2 定时误差(TED)信号的提取

Gardner码元同步算法是一种异步时钟恢复方法,本地生成码元时钟,采用插值方法得到抽样时刻码元值,不需要满足采样时钟与码元时钟是整数倍关系的要求。Gardner码元同步算法中,输入的基带信号经过插值后得到2倍码元速率的抽样数据,抽样数据经过反馈支路控制数控振荡器输出频率从而调整码元时钟,采样得到最佳采样点,完成时钟的锁定和跟踪。

Gardner算法不需要判决反馈,每个数据需要两个采样点,其中一个是strobe点,即符号最佳观察点;另一个是midstrobe点,即两个最佳观察点之间的采样点。一个在符号判决点附近,另一个在两个符号判决点中间附近,并且与载波相位偏差无关,因此定时调整可先于载波恢复完成,定时恢复环和载波恢复环相互独立,这给解调器的设计和调试带来了方便。

假设接收信号为: ,式中

,式中 为传输的复数数据,

为传输的复数数据, 为基带成型滤波波形,对

为基带成型滤波波形,对 的采样值可能产生定时误差,Gardner算法提取的定时误差为:

的采样值可能产生定时误差,Gardner算法提取的定时误差为:

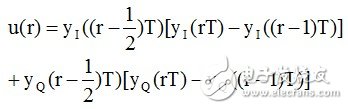

(2-1)

其中索引r表示符号数目,同相I和正交Q方向的第r个符号的判决值分别表示为 和

和 。同样,将r和(r-1)两个判决点中心位置的采样值表示为

。同样,将r和(r-1)两个判决点中心位置的采样值表示为 和

和 。整个误差是I和Q两个方向的定时误差之和,且此误差与载波相位无关。

。整个误差是I和Q两个方向的定时误差之和,且此误差与载波相位无关。

式中 ,

, 表示同相和正交分量,T为符号周期。Gardner算法适用于跟踪和捕获模式。

表示同相和正交分量,T为符号周期。Gardner算法适用于跟踪和捕获模式。

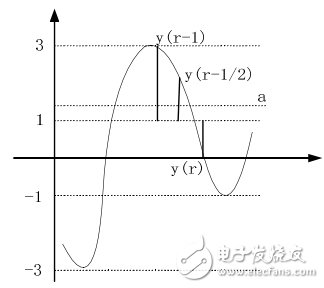

图3 16QAM解调后波形

在16QAM调制信号中,例如果符号从-1变为1,1变为-1,-3变为3,3变为-3等的时候,则没有定时误差时,中间点的平均值应为零。而有定时误差时,将会产生一个非零的值,它的大小与差错的大小成正比。另外一些情况,当没有定时误差时,中间点的平均值并不是零。例如符号从3变为-1,当没有定时误差时,中间点的平均值是1,如图3所示。

如果直接把Gardner算法运用在16QAM解调系统中,定时误差检测的结果有些点上是正确的,有些点上是错误的。对于大量数据,这些错误的平均值是零,因为没有定时误差的情况,中间点可能是0,-1,1,-2,2,其平均值为零。因此这些错误会导致定时时钟的抖动,通过滤波器可以减小这些抖动。

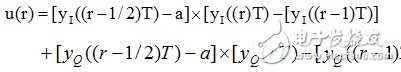

为了消除这些抖动。我们对Gardner算法做了进一步改进,其改进后算法为:

(2-2)

其中

当定时超前,误差为负,定时滞后,误差为正。Gardner算法具有两个特点:一是每个符号只需要两个采样点,且以码元速率输出误差信号;二是估计算法是独立于载波相位的,不受载波相位偏移的影响,即可以在载波相位同步之前,进行定时误差估计。

1.3 压控振荡器(VCO Voltage Controlled Oscillator)

定时恢复环的内插滤波器由VCO控制,它接受定时误差信号,给内插滤波器提供内插运算所需的参数 和

和 ,压控振荡器的时钟频率为1/

,压控振荡器的时钟频率为1/ 。

。

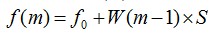

VCO的输出频率f(m):

,

,

为VCO预设基本频率,

为VCO预设基本频率, 为VCO控制信号,由定时误差信号经环路滤波器滤波后提供,VCO的输出频率随着

为VCO控制信号,由定时误差信号经环路滤波器滤波后提供,VCO的输出频率随着 的变化而变化,当

的变化而变化,当 稳定时,输出频率也就保持稳定。S为VCO对误差信号的敏感度。VCO输出每出现一次过零点,则产生一个定时调整抽样脉冲

稳定时,输出频率也就保持稳定。S为VCO对误差信号的敏感度。VCO输出每出现一次过零点,则产生一个定时调整抽样脉冲 ,从而可以决定

,从而可以决定 ,也就是决定哪些采样信号值参加内插运算。

,也就是决定哪些采样信号值参加内插运算。

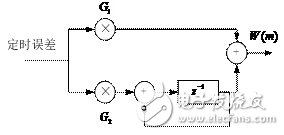

1.4 环路滤波器

采用二阶数字滤波器对定时误差信号进行滤波如图4,以减小定时误差信号的抖动。环路滤波器系数和定时误差S曲线系数以及数控振荡器控制灵敏度共同决定环路相对等效噪声带宽 。

。

图4 二阶数字滤波

选定环路相对等效噪声带宽 和阻尼系数,就可以求出二阶数字滤波的参数

和阻尼系数,就可以求出二阶数字滤波的参数 ,

, 。

。

2 ADS中的仿真结果分析

ADS,即HP Advanced Design System的简称。它是Agilent Technologies公司新推出的一套电路辅助设计软件。Agilent Technologies公司把已有产品:HP MDS(Microwave Design System)和HP EEsof IV(Electronic Engineering Software)两者的精华有机的结合起来,并增加了许多新的功能,构成了功能强大的ADS软件。ADS可应用于整个现代通信系统及其子系统,能对通讯系统能进行快速、便捷、有效的设计和仿真。

ADS软件分为Digital Signal Processing Network和Analog/RF Network两个仿真设计模块。接收机的仿真是在Digital Signal Processing Network中完成,里面加载了很多常用的通信器件,可供调用。

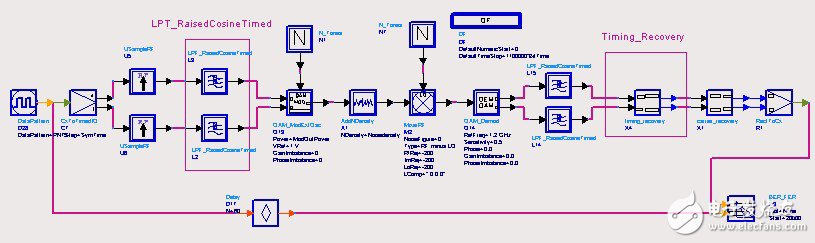

在ADS中,建立仿真模型,本文仿真基于16QAM调制、1.8GHHz中频、720Mbps码速率中频采样的全数字解调系统(如图5),研究了高速全数字解调中码元同步的关键技术。

图5 通信系统误码率仿真工程

仿真设计:1、系统中,码元的长度为5.6nsec。在发送端的低通成型滤波器(LPT_RaiseCosineTimed)中加入2nsc的延时来仿真码元抖动。

2、改变VCO的预设基本频率 来仿真接受端时钟偏差,VCO的敏感度S为1MHz/V。

来仿真接受端时钟偏差,VCO的敏感度S为1MHz/V。

仿真结果:

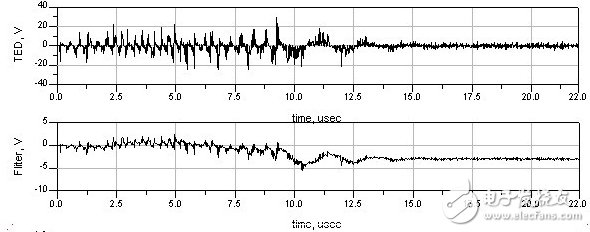

图6 时钟恢复环中误差信号、环路滤波后的信号

图6为从码元同步模块中测量出来的误差信号、环路滤波后的信号。从图中可得出,VCO根据反馈回来经过滤波后的误差信号(如图6下)来实时调整采样的频率,直到VCO输出时钟频率 等于2倍码元速率为止,就达到了平衡状态,此时定时误差为零(如图6上)。

等于2倍码元速率为止,就达到了平衡状态,此时定时误差为零(如图6上)。

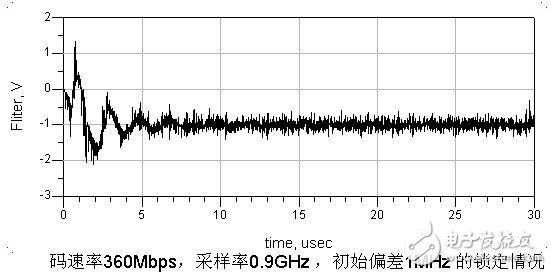

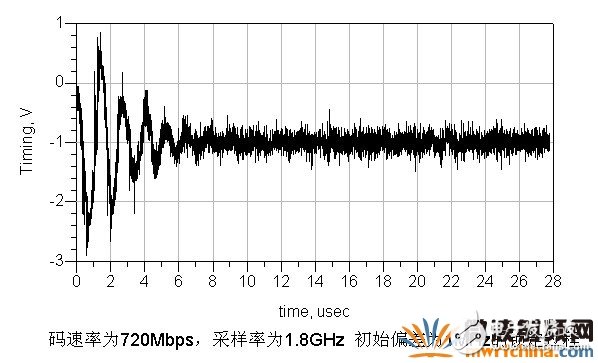

图7 不同码元速率的锁定过程

图7所示分别为1.8GHz采样率,码元速率720Mbps,初始偏差1MHz,信噪比20dB时码元同步的锁定情况;和0.9GHz采样率,码速率360MHz,初始偏差1MHz ,信噪比20dB时码元同步的锁定情况。仿真证明这种码元同步方法能够正确生成码元时钟满足高码速要求,并且适应不同码速率。能正确生成码元时钟满足高码速要求,并且适应不同码速率。

测试环境

测试项目无码元同步模块时误码率(BER)有码元同步模块时误码率(BER)

理想系统4.554E-64.554E-6

抖动8.730E-59.039E-6

接收时钟偏差Bias=0.5MHz0.0174.554E-6

Bias=1MHz0.0364.554E-6

Bias=1.5MHz0.0414.554E-6

Bias=2MHz0.0540.065

抖动和偏差0.0481.937E-5

表1 仿真系统中的码元抖动、时钟偏差时的误码率

通过上表说明,如图5所示的系统中,码元同步模块对于的信号的抖动和接收端时钟的频率偏差有较强的纠正能力。抖动为半个码元长度时,模块将误码率从1.730E-5降到了9.039E-6。对于时钟的频率偏差纠正能力尤为突出,达到3MHz的范围(748.5MHz~~751.5MHz)内都可以锁定。当同时加入码元抖动和时钟偏差时,系统也表现出了较强的纠错能力。

3 结束语

本文简要介绍了在ADS仿真器中,设计一个16QAM接收机的码元同步模块,以消除恢复时钟偏差和I、Q两路信号的不同步引起的码元抖动的问题。并针对16QAM这种调制方式,提出了改进的误差提取算法。仿真显示可以满足不同速率下的接收机要求。

-

AI接收机的工作原理和实现过程2025-11-17 7063

-

采用ADS实现接收机码元同步算法2019-06-27 1571

-

基于独立DSP 平台的实时卫星导航接收机的设计实现2010-04-07 760

-

一种DRM数字广播接收机的同步算法2010-06-22 907

-

DS/FH混合扩频接收机解扩及同步技术的FPGA实现2006-03-11 1823

-

一种基于ADS的雷达接收机系统设计方法2009-11-12 1588

-

毫米波接收机射频前端ADS仿真设计2011-07-05 1514

-

基于ADS的接收机码元同步算法实现2012-11-17 890

-

基于ADS仿真器中,设计一个16QAM接收机的码元同步模块方案2019-03-20 2699

-

MPPSK数字接收机位同步算法设计与实现2017-12-21 803

-

如何利用AD9361的接收机平台捕捉ADS-B信号2019-07-17 5783

-

如何使用ADS实现接收机射频前端的仿真2020-09-23 1386

-

如何使用ADS实现接收机码元同步算法的设计2020-08-28 959

-

如何使用FPGA实现ADC的TR UWB数字接收机性能2021-02-01 1340

-

基于FPGA的GPS接收机实现2021-04-09 1536

全部0条评论

快来发表一下你的评论吧 !