FPGA学习:电源电路设计

可编程逻辑

描述

与任何电子元器件一样,FPGA器件需要有电源电压的供应才能工作。尤其对于规模较大的器件,其功耗也相对较高,其供电系统的好坏将直接影响到整个开发系统的稳定性。所以,设计出高效率、高性能的FPGA供电系统具有极其重要的意义。

不同的FPGA器件、不同的应用方式会有不同的电压电流的需求。如图2.4所示,简单的归纳,可以将FPGA器件的电压需求分为三类:核心电压、I/O电压和辅助电压。

图2.4 FPGA器件的供电电压

核心电压是FPGA内部各种逻辑电路正常工作运行所需要的基本电压,该电压用于保证FPGA器件本身的工作。通常选定某一款FPGA器件,其核心电压一般也都是一个固定值,不会因为电路的不同应用而改变。核心电压值可以从官方提供的器件手册中找到。

I/O电压顾名思义便是FPGA的I/O引脚工作所需的参考电压。在引脚排布上,FPGA与ASIC最大的不同,便是FPGA所有的可用信号引脚基本都可以作为普通I/O使用,其电平值的高低完全由器件内部的逻辑决定。当然了,它的高低电平标准也受限于所供给的I/O电压。任何一片FPGA器件,它的I/O引脚通常会根据排布位置分为多个bank。同一个bank内的所有I/O引脚所供给的I/O电压是共用的,可以给不同的bank提供不同的I/O电压,它们彼此是不连通的。因此,不同bank的不同I/O电压为FPGA器件的不同接口应用提供了灵活性。这里举一个例子,Cyclone IV系列器件的某些bank支持LVDS差分电平标准,此时器件手册会要求设计者给用于LVDS差分应用的bank的I/O电压供2.5V电压,这就不同于一般的LVTTL或LVCOMS的3.3V供电需求。而一旦这些用于LVDS传输的I/O bank电压供给为2.5V,那么它就不能作为3.3V或其他电平值标准传输使用了。

除了前面提到的核心电压和I/O电压,FPGA器件工作所需的其它电压我们通常都称为辅助电压。例如FPGA器件下载配置所需的电压,当然了,这里的辅助电压值可能与核心电压值或I/O电压值是一致的。很多FPGA的PLL功能块的供电会有特殊要求,也可以认为是辅助电压。由于PLL本身是模拟电路,而FPGA其他部分的电路基本是数字电路,因此PLL的输入电源电压也很有讲究,需要专门的电容电路做滤波处理,而它的电压值一般和I/O电压值不同。此外,例如Cyclone V GX系列FPGA器件带高速Gbit串行收发器,通常有额外的参考电压;MAX10系列器件的ADC功能引脚电路也需要额外的参考电压;一些带DDR3控制器功能的FPGA引脚上通常也有专门的参考电压……诸如此类的参考电压我们都可以归类为FPGA的辅助供电电压,在实际电源电路连接和设计过程中,都必须予以考虑。

目前比较常见的供电解决方案主要是LDO稳压器、DC/DC芯片或电源模块。LDO稳压器具有电路设计简单、输出的电源电压纹波低的特点,但是它的一个明显劣势是效率也很低;而基于DC/DC芯片的解决方案能够保证较高的电源转换效率,散热容易一些,输出电流也更大,是大规模FPGA器件的最佳选择;而电源模块简单实用并且能够有更稳定的性能,只不过价格通常比较昂贵,在成本要求不敏感的情况下,是FPGA电源设计的一种最为简单快捷的解决方案。以笔者多年的经验来看,在LDO稳压器、DC/DC芯片或电源模块的选择上,一般遵循以下原则:

● 电流低于100mA的电压可以考虑使用LDO稳压器产生,因为电路简单、使用元器件少、PCB面积占用小,且成本也相对低廉。

● 对电源电压的纹波极为敏感的供电考虑使用LDO,如CMOS Sensor的模拟供电电压、ADC芯片的参考电压等。

● 除了上述情况,一般电流较大、对电源电压纹波要求不高的情况,都尽量考虑使用DC/DC电路,毕竟它能够提供大电流供电,且提供最好的电源转换效率。

● 对于电源模块,笔者见到最多的是军工等成本不敏感、板级PCB空间较大的应用中使用,它其实是LDO稳压器和DC/DC电路优势的整合。

通常而言,对于FPGA器件的电源方案的选择以及电源电路的设计,一定要事先做好前期的准备工作,如以下几点是必须考虑的:

● 器件需要供给几档电压,压值分别是多少?

● 不同电压档的最大电流要求是多少?

● 不同电压档是否有上电顺序要求?(大部分的FPGA器件是没有此项要求的)

● 电源去耦电容该如何分配和排布?

● 电源电压是否需要设计特殊的去耦电路?

关于设计者需要确定的各种电气参数以及电源设计的各种注意事项,其实在器件厂商提供的器件手册(handbook)、应用笔记(application notes)或是白皮书(white paper)中一般都会给出参考设计。所以,设计者若希望能够较好的完成FPGA器件的电源电路设计,事先阅读大量的官方文档是必须的。

说到电源,也不能不提一下地端(GND)电路的设计,FPGA器件的地信号通常是和电压配对的。一般应用中,统一共地连接是没有问题的,但也需要注意特殊应用中是否有隔离要求。FPGA器件的引脚引出的地信号之间通常是导通的,当然也不能排除有例外的情况。如果漏接个别地信号,器件通常也能正常工作,但是笔者也遇到过一些特殊的状况,如Altera的Cyclone III器件底部的中央有个接地焊盘,如果设计中忽略了这个接地信号,那么FPGA很可能就不干活了,因为这个地信号是连接FPGA内部的很多中间信号的地端,它并不和FPGA的其它地信号直接导通。因此,在设计中也一定要留意地信号的连接,电源电路的任何细小疏忽都有可能导致器件的罢工。

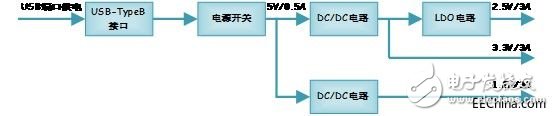

在我们所设计的这个实验平台上,如图2.5所示,由PC的USB端口进行供电,通常可以提供5V/0.5A的电压和电流。5V电压输入到两个DC/DC电路分别产生3.3V和1.2V的电压,DC/DC芯片支持的最大电流可以达到3A,当然我们的FPGA器件实际上根本不需要这么大的电流。之所以采用DC/DC电路产生3.3V和1.2V电压,是考虑到3.3V是FPGA的I/O电压,也是板上大多数外设的供电电压,它的电流相对较大;而1.2V是FPGA器件的核电压,电流也较大;因此,它们使用DC/DC电路更合适,既可以保证较大电流需求,也能够实现更好的电源转换效率。而2.5V电压使用3.3V转2.5V的LDO电路,是由于2.5V仅仅只是FPGA的下载配置电路使用,电流相对较小,它对转换效率要求也不高,使用简单的LDO电路来得更“经济实惠”一些。

图2.5电源电路示意图

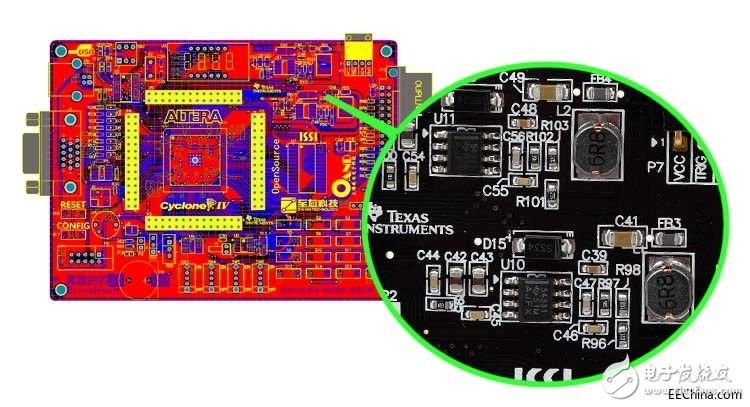

如图2.6所示,这是电源电路的layout示意图,为了获得更大的电流供给能力、更高的电源转换效率,我们只能不惜使用更多的分离元器件和更大的布板空间来“妥协”。

图2.6 电源电路的layout

-

FPGA电路设计电源问题2014-06-13 2685

-

FPGA实战演练逻辑篇17:FPGA电源电路设计2015-04-22 2962

-

电路设计[FPGA]设计经验分享2019-01-03 2887

-

FPGA板级电路设计的五要素2019-01-25 3918

-

电源设计实用教程——电子系统的电源电路设计2019-09-24 5259

-

电源电路设计实例2008-05-13 1590

-

射频电路设计学习(定稿)2015-11-10 1438

-

基于FPGA的惯性平台测试保护电路设计2016-01-04 596

-

电源电路设计2016-04-15 1372

-

电路设计[FPGA]设计经验2016-05-20 742

-

基于FPGA的串口通信电路设计2017-01-24 862

-

新手如何学习FPGA外围硬件电路设计2017-02-11 29142

-

DSP和FPGA的HDLC协议通讯电路设计2017-10-19 1197

-

FPGA的硬件电路设计教程和FPGA平台资料简介2020-07-06 2412

-

FPGA CPLD数字电路设计经验分享.2021-09-18 1426

全部0条评论

快来发表一下你的评论吧 !