TPS54494 集成 FET 的 4A 双通道同步降压开关数据手册

描述

TPS54494 是一款双通道自适应导通时间 D-CAP2™ 模式同步降压转换器。这 TPS54494使系统设计人员能够完成各种终端设备的电源总线套件 稳压器具有经济高效、低元件数量和低待机电流解决方案。主要的 TPS54494 的控制回路使用 D-CAP2™ 模式控制,可提供非常快速的瞬态 响应,无需外部补偿组件。自适应准时控制支持无缝 在较高负载条件下的 PWM 模式和轻负载下的 Eco 模式™作之间转换。 省油模式™允许TPS54494在较轻的负载条件下保持高效率。这 TPS54494 能够适应低等效串联电阻 (ESR) 输出电容器,例如 POSCAP 或 SP-CAP 以及超低 ESR 陶瓷电容器。该设备提供方便且 在 4.5V 至 18V 的输入电压下高效运行。

TPS54494 采用 4.4 mm × 5 mm 16 引脚 TSSOP (PWP) 和 4 mm × 4 mm 16 引脚封装 VQFN (RSA) 封装,额定环境温度范围为 –40°C 至 85°C。

*附件:tps54494.pdf

特性

- D-CAP2 控制模式

- 快速瞬态响应

- 无需外部元件即可进行环路补偿

- 与陶瓷输出电容器兼容

- 宽输入电压范围:4.5 V 至 18 V

- 输出电压范围:0.76V 至 7V

- 针对低占空比应用优化的高效集成 FET

- 90 mΩ(高侧)和 60 mΩ

(低侧)

- 90 mΩ(高侧)和 60 mΩ

- 高初始参考精度

- 4A CH1 / 2A CH2 连续负载电流

- 低侧 r

DS(开)无损电流感应 - 固定软启动 : 1 ms

- 非灌电流预偏置软启动

- Powergood 公司

- 700 kHz 开关频率

- 逐周期过流限制控制

- OCL/UVLO/TSD 保护

- 用于过载保护的打嗝定时器

- 具有集成

Boost PMOS 开关的自适应栅极驱动器 - 由于热补偿r 导致的 OCP 常数

DS(开)4000ppm/°C 时 - 16 引脚 HTSSOP、16 引脚 VQFN 封装

- 自动跳过 Eco 模式,可在轻负载下实现高效率

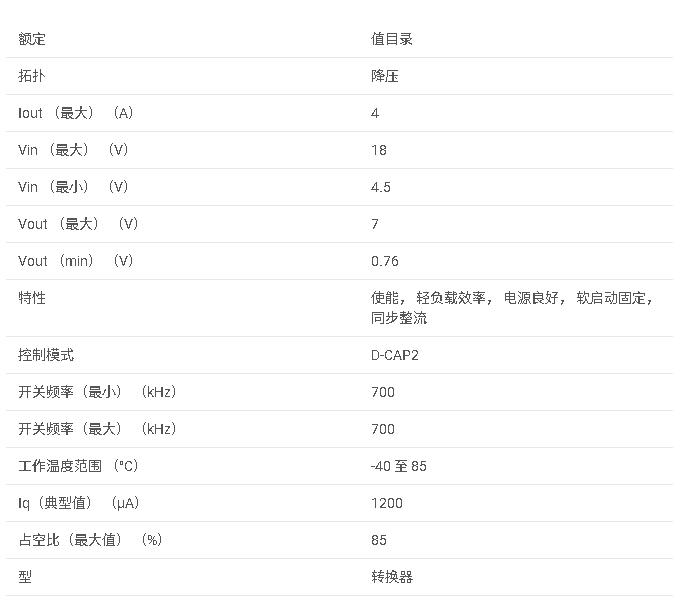

参数

方框图

1. 产品概述

TPS54494 是一款4A/2A双通道同步降压(Buck)转换器,集成了高效FET,专为低占空比应用优化。该转换器采用D-CAP2™控制模式,提供快速瞬态响应,无需外部补偿元件,支持陶瓷输出电容器,适用于数字TV电源、网络家庭终端、数字机顶盒(STB)、DVD播放器/录像机等多种应用。

2. 主要特性

- 双通道同步降压转换器:每个通道集成N沟道MOSFET,提供4A(CH1)和2A(CH2)的连续负载电流。

- D-CAP2™控制模式:实现快速瞬态响应,无需外部补偿。

- 宽输入电压范围:4.5V至18V。

- 宽输出电压范围:0.76V至7V。

- 高效率:支持Eco-mode™操作,提高轻载效率。

- 固定软启动时间:每个通道具有1ms的固定软启动时间。

- 多种保护功能:包括过流限制、OCL/UVLO/TSD保护、打嗝定时器。

3. 功能描述

3.1 PWM操作

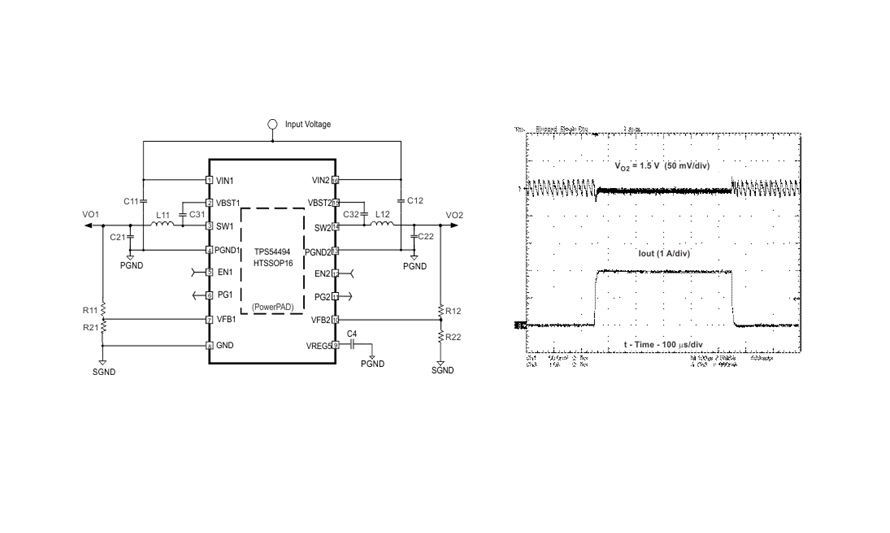

TPS54494的主控制环路采用自适应导通时间脉冲宽度调制(PWM)控制器,结合D-CAP2™控制模式,实现伪固定频率和低外部元件配置,支持低ESR和陶瓷输出电容器。

3.2 Auto-Skip Eco-mode™控制

在轻载条件下,TPS54494通过Auto-Skip Eco-mode™功能提高效率。当输出电流减少到重载条件的某个阈值以下时,转换器进入不连续导电模式,减少能量损耗。

3.3 软启动和预偏置软启动

每个通道具有1ms的固定软启动时间,通过内部DAC逐渐提高参考电压来实现输出电压的平稳上升。此外,TPS54494还包含防止从预偏置输出中拉取电流的电路。

3.4 电流检测和过流保护

过流保护通过逐周期谷值检测控制电路实现,监测低侧FET的开关电压来检测过流情况。当检测到过流时,转换器保持低侧开关导通,直到测量电压降至电流限制对应的电压以下。

3.5 其他保护功能

- 欠压保护(UVLO) :监测VREG5引脚的电压,当电压低于UVLO阈值时关闭转换器。

- 热关断(TSD) :监测转换器温度,当温度超过阈值时关闭转换器以防止损坏。

4. 应用与实现

4.1 设计指南

设计过程需要确定输入电压范围、输出电压和输出电流等参数。输出电压通过连接在输出节点和VFBx引脚之间的电阻分压器设置。输出滤波器采用LC电路,需选择合适的电感和电容值以确保稳定性。

4.2 布局考虑

- 保持输入电流环路尽可能小。

- SW节点应尽可能小且短,以减少寄生电容和电感。

- 将模拟和非切换组件远离切换组件。

- 从信号地到功率地进行单点连接。

- 不允许切换电流在器件下流动。

- 使VINx和PGNDx的布线图案尽可能宽。

5. 封装与订购信息

TPS54494提供HTSSOP(PWP)和QFN(RSA)两种封装选项,具有16个引脚。详细的封装和订购信息可参考数据手册中的“封装选项附录”部分。

6. 注意事项

- 在处理集成电路时,应遵循适当的静电放电(ESD)预防措施。

- TI提供的技术和可靠性数据、设计资源等“按原样”提供,不附带任何形式的保证。客户有责任选择适合的TI产品并验证其应用。

-

TPS54494降压转换器评估模块使用指南2026-04-24 126

-

TPS54494降压转换器评估模块用户指南2024-12-03 312

-

具有集成 FET (SWIFT™) 的 2A 双通道同步降压转换开关TPS54294数据表2024-04-26 451

-

具有集成FET的4.5 V至18V 输入、4A 输出单路同步降压转换TPS54427数据表2024-04-22 445

-

带集成FET的3-A输出单同步降压开关TPS54327数据表2024-04-12 448

-

集成 FET 的 2A 双通道同步降压开关TPS54295数据表2024-04-09 403

-

带有集成场效应晶体管的 4A/2A 双通道同步降压转换器TPS54494数据表2024-04-08 438

-

带有集成场效应晶体管 (FET) 的 2A/3A 双通道同步降压转换器TPS542941数据表2024-04-07 502

-

DN1044-双通道42V、4A单片同步降压静音开关2,静态电流为6.2μA2021-05-17 1438

-

具有6.2μA静态电流的双通道42V 4A单片同步降压静音开关22019-08-22 2065

-

TPS54494 具有集成 FET 的 4A 双通道同步降压开关2018-10-16 430

全部0条评论

快来发表一下你的评论吧 !