简谈数字电路设计中的抖动

描述

大家好,到了每日学习的时候了。今天我们来聊一聊数字电路设计中的抖动。

既然说到了抖动,那么什么是抖动?那首先我们就来了解一下什么是抖动。

随着通信系统中的时钟速率迈入GHz级,抖动在数字设计领域中日益得到人们的重视。在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。抖动反映的是两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关。除此之外,还有一种由于周期内信号的占空比发生变化而引起的抖动,称之为半周期抖动。总的来说,jitter可以认为在时钟信号本身在传输过程中的一些偶然和不定的变化之总和。

************************************************************************************************************************

一、抖动的几个重要概念

1. 抖动的基本概念

在理想情况下,一个频率固定的完美的脉冲信号(以1MHz为例)的持续时间应该恰好是1us,每500ns有一个跳变沿。但不幸的是,这种信号并不存在。实际上,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。在绝大多数文献和规范中,时间抖动(jitter)被定义为高速串行信号边沿到来时刻与理想时刻的偏差,所不同的是某些规范中将这种偏差中缓慢变化的成分称为时间游走(wander),而将变化较快的成分定义为时间抖动(jitter Wander反映的主要是时钟源随着时间、温度等的缓慢变化,影响的是时钟或定时信号的绝对精度。在通信或者信号传输中,由于收发双方都会采用一定的时钟架构来进行时钟的分配和同步,缓慢的时钟漂移很容易被跟踪上或补偿掉,因此wander对于数字电路传输的误码率影响不大,高速数字电路测量中关心的主要是高频的jitter。

2. 抖动的分类

抖动有两种主要类型:确定性抖动和随机性抖动。

确定性抖动是由可识别的干扰信号造成的,这种抖动通常幅度有限,具备特定的(而非随机的)产生原因,而且不能进行统计分析。随机抖动是指由较难预测的因素导致的时序变化。例如,能够影响半导体晶体材料迁移率的温度因素,就可能造成载子流的随机变化。另外,半导体加工工艺的变化,例如掺杂密度不均,也可能造成抖动。

3. 抖动的测试方法

由于信号边沿的时间偏差可能是由于各种因素造成的,有随机的噪声,还有确定性的干扰。所以对这个时间偏差通常是随机的,而是有一定的统计分布,在不同的应用场合这个测量的结果可能是用有效值(RMS)衡量,也可能使用峰峰值(peak-peak)衡量,更复杂的场合还会对这个时间偏差的各个成分进行分解和估计。因此抖动的精确测量需要大量的样本以及复杂的算法。

************************************************************************************************************************

二、抖动的测量方法

可以通过许多基本测量指标确定抖动的特点,基本的抖动参数包括:

1. 周期抖动(Period jitter)

测量实时波形中每个时钟和数据的周期的宽度。这是最早最直接的一种测量抖动的方式。这一指标说明了时钟信号每个周期的变化。

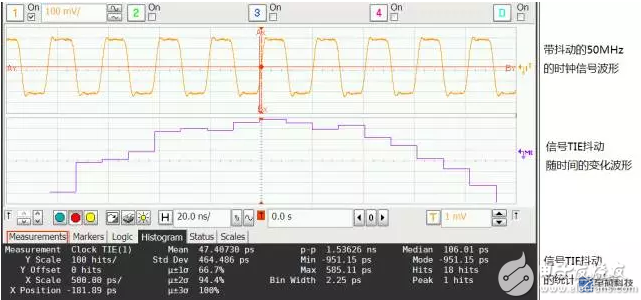

如图为带抖动的50MHz的时钟信号进行周期抖动测量的结果,借助于相应的抖动分析软件,观察到信号周期随时间的变化曲线,以及信号周期的最大值、最小值、周期变化的峰峰值、周期变化的方差等。

2. 周期到周期抖动(Cycle to Cycle jitter)

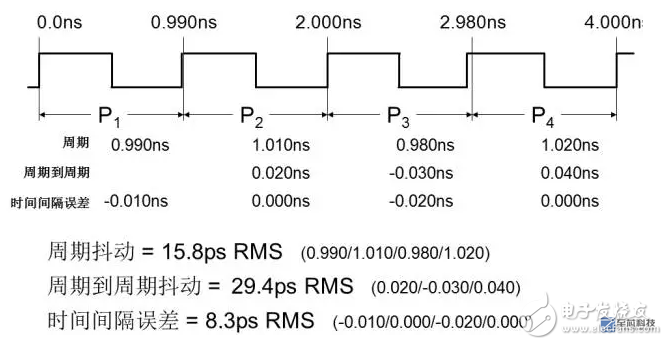

为了衡量时钟信号相邻周期的变化快慢,有时会用“周期到周期抖动”进行衡量,测量任意两个相邻时钟或数据的周期宽度的变动有多大,通过对周期抖动应用一阶差分运算,可以得到周期间抖动。这个指标在分析琐相环性质的时候具有明显的意义。

有些特殊的应用(比如针对DDR2/3的时钟信号)还定义了N-cycle jitter,即相邻N个时钟周期的抖动变化。下图是对同一个50MHz的时钟波形进行Cycle-Cycle抖动测量和统计的结果。

3. 时间间隔误差抖动(Time Interval Error)

所谓时间间隔误差,是指被测信号边沿相对于其参考时钟有效边沿的抖动。

测量时钟或数据的每个活动边沿与其理想位置有多大偏差,它使用参考时钟或时钟恢复提供理想的边沿。TIE在通信系统中特别重要,因为他说明了周期抖动在各个时期的累计效应。

下图是对同一个50MHz的时钟信号进行TIE抖动的分析和统计结果。

************************************************************************************************************************

三、结论

从前面举的例子可以看到,对于同一个信号,用不同的方式进行测量和衡量,得到的结果可能是不一样的。如图所示,对于同一个带抖动的时钟信号,对其进行周期抖动测量、周期到周期抖动测量以及时间间隔误差抖动测量,得到的结果可能是不一样的。

因此,对于一个信号进行抖动测量之前需要先明确关注的抖动类型,否则测量结果的物理含义是不明确的。

对于更复杂的数字信号来说,除了关心其抖动的RMS值以及峰峰值以外,还会关心该抖动的不同组成成分,因为不同成分的抖动对于电路的影响是不一样的,相应的应对手段也不一样。比如很多高速总线都会对高速数字信号的随机抖动成分(Random Jitter)、周期性抖动(Periodic Jitter)、ISI抖动(Inter-Symbol Interference jitter)等进行进一步的分解和研究。

抖动是数字信号,特别是高速数字信号非常重要的一个概念,越是高速的信号,其比特周期越短,对于抖动的要求就越严格。

今天就聊到这里,各位,加油!

-

华为《高速数字电路设计教材》2014-09-01 0

-

简谈数字电路设计中的抖动2018-02-25 0

-

基于LabVIEW的数字电路设计和仿真2010-03-30 995

-

高速数字电路设计2007-10-16 3225

-

数字电路设计2009-08-26 2830

-

数字电路设计的信号完整性问题探讨2011-09-07 1986

-

高速数字电路设计大全2017-01-17 970

-

高速数字电路设计-华为2021-04-21 863

-

FPGA CPLD数字电路设计经验分享.2021-09-18 1086

-

高速数字电路设计教材-华为2022-06-13 794

-

数字电路设计的基本流程2022-07-10 7799

-

高速数字电路设计.zip2022-12-30 394

全部0条评论

快来发表一下你的评论吧 !