ad9854应用电路图大全(五款ad9854信号发生/频率发生器/正交信号源电路)

IC应用电路图

描述

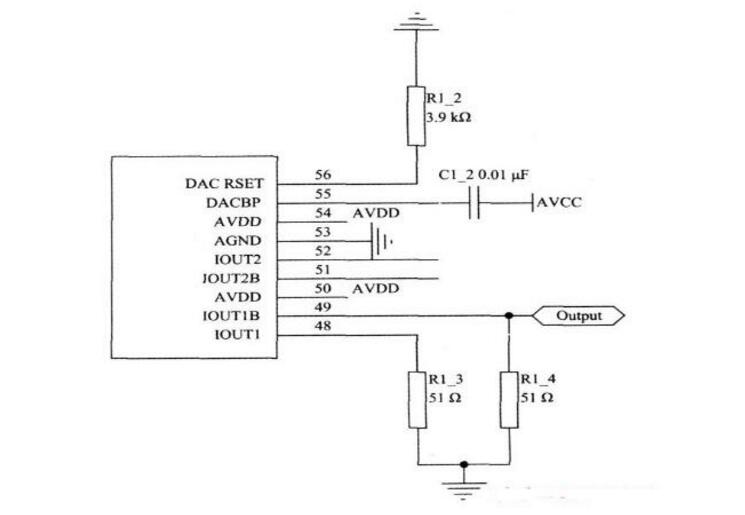

ad9854应用电路图一:信号发生电路

这里采用了AD9854 这款DDS 芯片, 它在300 MHz 时钟驱动下, 按照乃奎斯特采样定律可以产生最高150 MHz 的信号,为了得到信号较好的频率则一般只得到最高100 MHz 的信号。若要得到高于100 MHz 的信号, 则可采用其高次谐波得到。基于AD9854 的信号发生电路如图 所示:

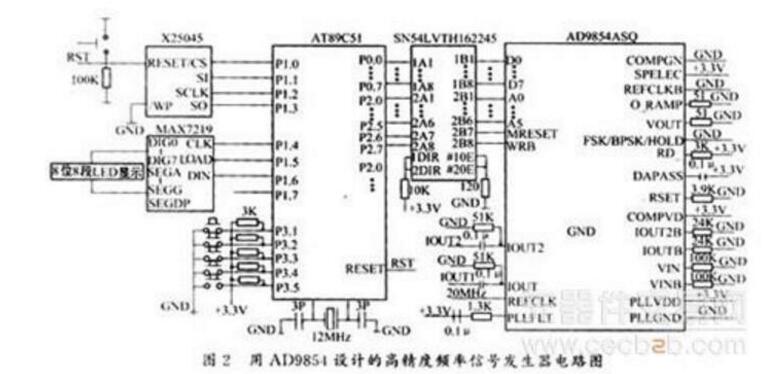

ad9854应用电路图二:高精度频率发生器

下面给出一种用AD9854开发高精度频率信号发生器的简易方法,开发者只需要熟悉MCS-51单片机编程即可。该系统具有开发周期短,开发成本低的特点,也可以作为探索AD9854功能的一种方法,它的电路原理图见图2。

系统主要由DDS芯片AD9854、单片机AT89C51、看门狗定时器X25045和LED显示驱动芯片MAX7219组成。在这个系统中提供了8位七段LED显示器,其中前五位为输出频率值,显示范围为00.000~99.999MHz,后三位为幅度显示位,显示范围为0~999,表示幅值从零幅度到满幅度的变化。

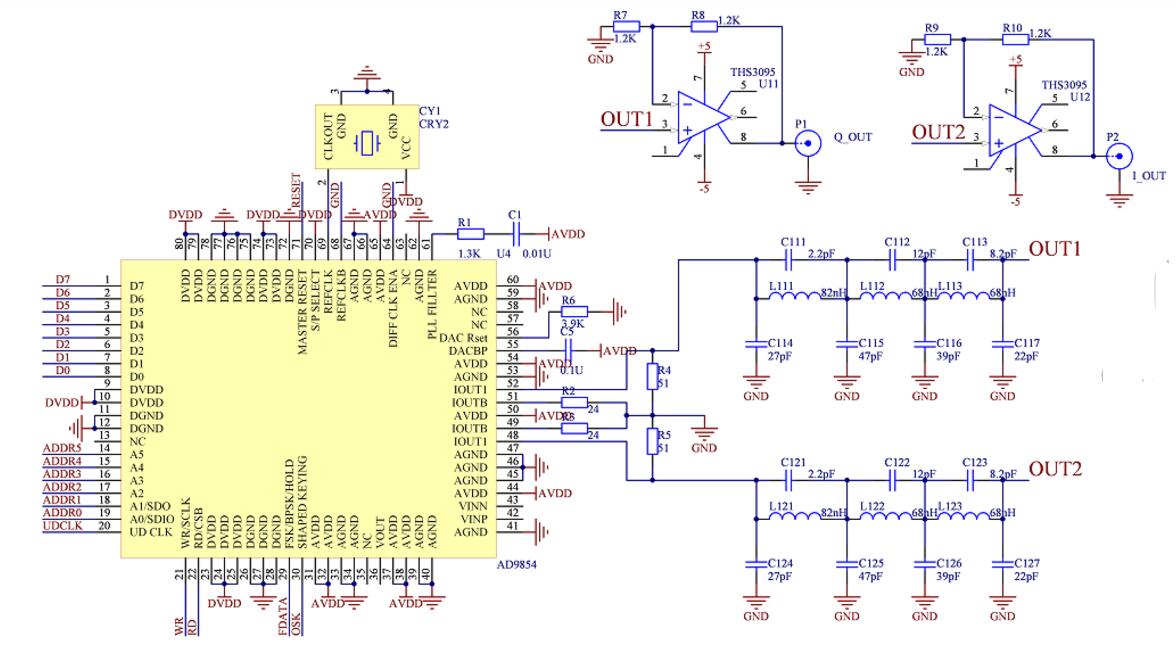

ad9854应用电路图三:正交信号源

正交信号源选择了DDS芯片AD9854,具体实现电路见下图。对AD9854进行编程控制,使之输出两路幅度相同并且正交的信号,然后对输出信号进行滤波,使得正弦波变得更加平滑,滤波之后再把输出峰值为512mV的信号放大2倍到1.24V。

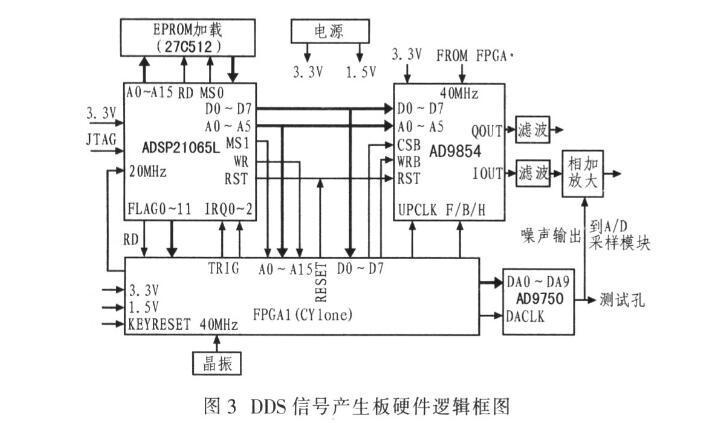

ad9854应用电路图四:信号产生

信号产生系统硬件主要有AD9854,ADSP21065L,带通滤波器,FPGA噪声产生电路,DDS输出中频信号增益控制,噪声信号相加电路,以及相关的时钟,电源,FPGA控制等功能单元。DDS模块主要由AD9854,ADSP21065L和相应的FPGA控制逻辑构成。ADSP21065L根据FPGA的控制时序来设置DDS的工作方式和控制字。图3为信号产生系统的硬件逻辑框图。

具体模块功能说明:

(1)DDS控制模块 ADSP21065L外部输入20 MHz时钟,最高工作在60 MHz,主要控制AD9854,向AD9854写控制字,中断输入IRQ0~IRQ2接FPGA,外部采用上拉电平。其中,一个作为雷达的重频周期信号,一个作为雷达波形的时序信号,而另一个保留。Flag0~Flag11是双向输入引脚,主要为AD9854产生3个控制信号,也可作为外部的输入控制信号,要求外部可控。ADSP-21065L的外部供电电源为3.3 V,采用板上(REG1117)直流变换器实现。ADSP21065L的加载采用EPROM(27C512)方式,用JTAG调试。FPGA采用Cyclone系列的EP1C3T144,主要产生各种控制信号和时序信号。FPGA的输出信号有:输出 1路复位信号到DSP和AD9854,AD9854的控制信号CS、WR、UPCLK和F/B/H。20 MHz的DSP时钟信号和40 MHz的AD9854时钟信号。

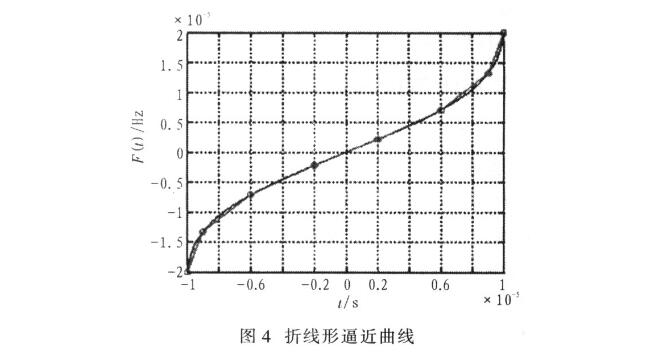

(2)DDS信号产生模块 DDS AD9854的最高工作频率是300 MHz,它主要接收ADSP-21065L的控制字,产生脉冲雷达波形。当外部输入40 MHz时,内部频率倍增器设置其工作频率为200 MHz。其工作电压3.3 V,也可由外部输入的直流电源经过本板的两片REG1117型DC-DC变换器变换得到。AD9854有5种可编程的工作模式,选择一种模式需要编程控制寄存器(并行地址1FH)中的mode0,mode1,mode2。5种可编程的工作模式为:单音调(模式000);非斜升的FSK(模式001);斜升FSK(模式010);线性调频脉冲(模式011);相位编码(模式100)。对于NLFM信号,采用线性调频折线逼近式实现,如图4所示。因此,将调频区域分为几段,每段用不同的线性调频逼近,即第一段更新频率字,后面每段起更新频率增量字,时间增量字就能实现折线型NLFM信号。

(3)电源模块 该信号产生模块的输入电源具有+5 V和-5 V,需要产生3.3 V,1.5 V,利用5片REG1117实现。其中1片为DSP,2片为AD9854,2片分别为FPGA产生3.3 V和1.5 V。若其余的I/O设备也需使用3.3 V,则与FPGA共用。

ad9854应用电路图五:高精度频率合成器

AD9854的300M系统时钟可以通过4X和20X可编程控制电路由较低的外部基准时钟得到。直接的300M时钟也可以通过单端或差分输入。AD9854还有单脚输入的常规FSK和改进的斜率FSK输出。

ad9854相关文章:

ad9854中文资料汇总(ad9854引脚图及功能_内部结构及应用电路)

ad9854相关下载:

-

自己设计的基于AD9854可调频率和占空比的信号源附电路原理图2018-11-19 2615

-

基于AD9854的正交扫频信号源设计2018-05-18 7853

-

ad9854单片机程序详细说明(ad9854结构框图及电路)2018-05-17 24748

-

ad9854中文资料汇总(ad9854引脚图及功能_内部结构及应用电路)2018-05-16 27667

-

基于AD9854的信号发生器设计2017-12-09 9090

-

DDS工作原理及基于AD9854的信号发生器的设计2017-11-16 1940

-

ad9854产生线性调频脉冲信号2017-11-03 5554

-

【DIY信号发生器】AD9854方案2014-06-17 6917

-

使用AD9854设计函数信号发生器2014-04-30 3986

-

基于AD9854数控信号发生器的设计2013-04-15 3232

-

基于AD9854的高精度高频信号发生器2009-10-27 1119

全部0条评论

快来发表一下你的评论吧 !