基于FPGA控制AD9854产生正弦波

FPGA/ASIC技术

描述

ad9854工作原理

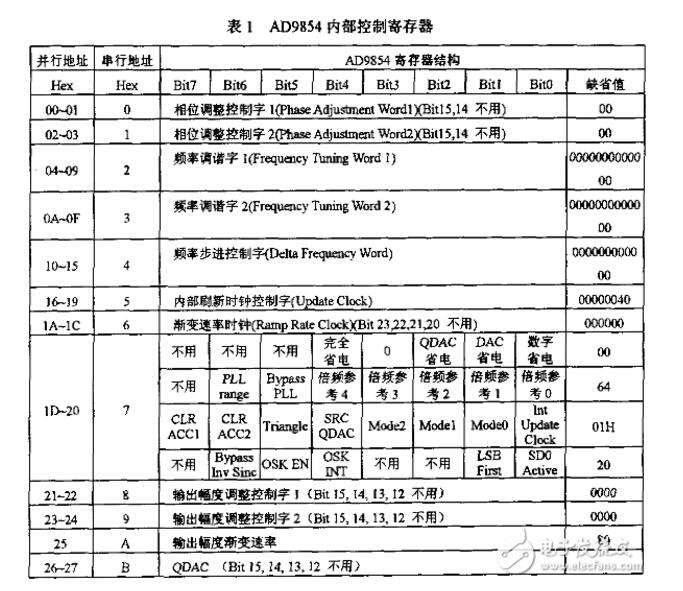

AD9854采用80脚LQFP封装,其内部共有40个8位的控制寄存器,分别用来控制输出信号频率、相位、幅度、步进斜率等,以及一些特殊控制位。下表给出了控制寄存器的分布情况。

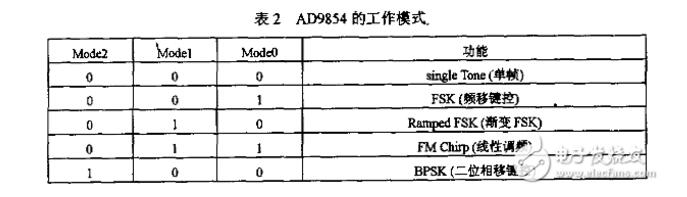

AD9854能够产生多种形式的额输出信号,工作模式的选择是通过对控制寄存器IFH中的三个位(Mode2、Mode1、Mode0)的控制来实现的。见下表。

事实上,除上述工作方式外,通过不同工作方式的组合控制,还可以产生更多的输出信号形式(例如,非线性调频信号)。下面分别予以介绍。

单频模式(SingleTone)

这是AD9854复位后的缺省工作模式。输出频率由写入控制寄存器04H~09H中的48位频率调谐字1(FrequcncyTuningWordI--FTW)决定,相位由控制寄存器00H~01H中的14位相位调谐字决定,1和Q通道的输出信号幅度可分别由控制寄存器21H~22H、23H~24H中的两个12位幅度调整控制字决定。此时,频率调谐字2(FTW2,0AH~0DH)和相位调谐字2(02H~03H)不用。

频率调谐字(FTW)=(fout&TImes;2N)/fsysglk

其中,fout;输出信号频率(0~fsysglk/2);

N,相位累加器的分辨率,这里是48位;

fsysglk,系统时钟。

值得注意的是,1和Q通道的输出在任何时侯都是正交的。另外,所有频率的改变都是相位连续的。

频移键控模式(FSK)

两个频率F1、F2分别由FTW1和FTW2中的值决定,输出哪个频率由Pin29的电平决定。Pin29为“0“,输出F1;Pin29为“I”输出F2。

频率渐变FSK(RampedFSK)

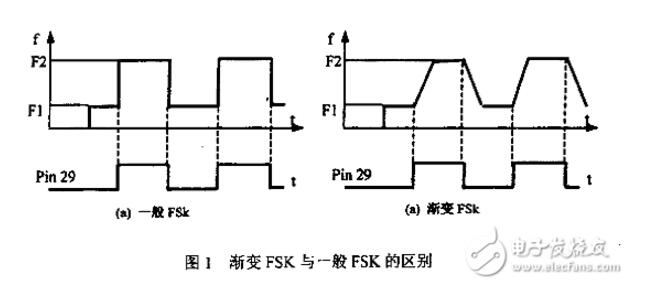

AD9854提供一种频率渐变的FSK输出模式,可改善输出信号的带宽性能。其输出滤形与传统的FSK的差别见图1。

此时,频率由Fl到F2的变化不是突变的,而是按一定的斜宰逐渐从F1变化到F2.该斜率由20位的渐变速率时钟(RampRateClock-RRC,1AH~1CH)和48位的频率步进字《(DetaFrequencyWord--DFW,10H~15H)寄存器中的值共同决定。

FTW1寄存器中置低频控制字,FTW2寄存器中置高频控制字;RRC寄存器中置渐变过程中每个中间频率的持续时间控制字。48位的DFW寄存器中的值决定了每次频率步进量。频率的上升或下降由Pin29上的电平决定。Pin29为“0”,上升:Pin29为“1“,下降。当到达终点频率后则停止渐变并保持该终点频率。

A.自动三角波形频率输出。若置位控制寄存器1FH中的Triangle位,则无需Pin29脚上的电平控制,AD9854就能按照RRC和DFW寄存器中的设置产生从Fl到F2,然后立刻再从F2到F1的锯齿形频率输出。

B.控制位CLRACCI(]FH寄存器中):当该位置“1”时,则停止现行的频率渐变过程,回到起始频率重新开始下一个渐变过程。

C.控制位CLRACC2(1FH寄存器中):该位置“1”时,AD9854输出直流信号(0Hz)。

二位相移键控模式{BPSK)

这种工作方式的控制类似于FSK模式。两个输出相位P1和P2分别由两个14位相位调整控制字寄存器(00H~0lH,02H~03H)决定;Pin29上的电平决定用哪个作起始相位。输出信号的烦率由FTW1寄存器中的值决定。

相位分辨率=360度/2的14次方=0.022033691度

线性调频模式(FMChirp)

AD9854按用户所要求的频率分辨率、调频斜率、扫频方向和频宰范围产生精确的线性或非线性调频信号。此时,寄存器FTWl中装入的值决定起点频率;频率步进量由寄存器DFW决定;中间频率持续时间由寄存器RRC决定,Pin29为“保持(Hoid)”功能,高电平时.Chirp过程暂停,输出频率保持此前值不变,直至Pin29又重新变为低电平后,再以原来的斜率继续原Chirp过程。

需要注意的是,Chirp模式只规定了起点频率,而没有设定终点频率,所以需要由用户来决定何时停止该过程。若没有及时发出停止指令,频率会持续上升到fsysglk/2为止。

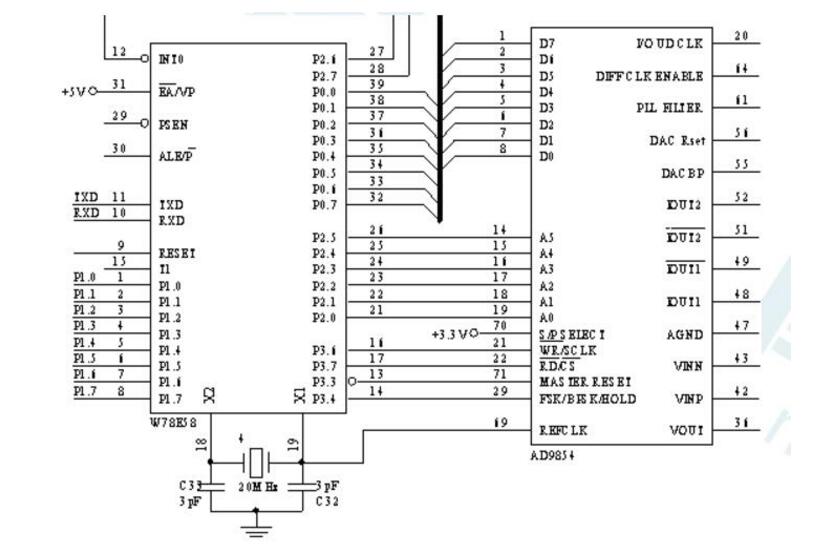

AD9854应用电路图

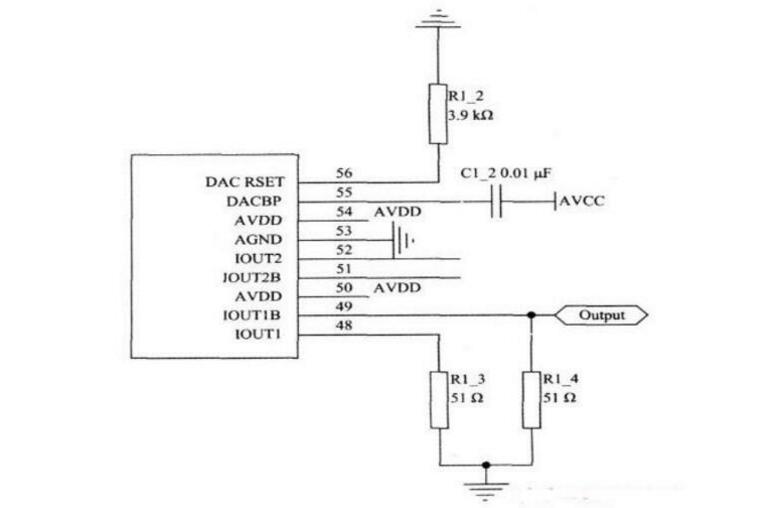

这里采用了AD9854 这款DDS 芯片, 它在300 MHz 时钟驱动下, 按照乃奎斯特采样定律可以产生最高150 MHz 的信号,为了得到信号较好的频率则一般只得到最高100 MHz 的信号。若要得到高于100 MHz 的信号, 则可采用其高次谐波得到。基于AD9854 的信号发生电路如图所示:

键盘共设有16个键,由P1.0~P1.3四条行线和P1.4~P1.7四条列线构成。其中包括数字键、单位键及功能键,用来对所需信号的频率、幅度及功能进行控制,最后输出的信号频率、幅度等信息通过液晶显示屏显示出来。显示部分采用国显公司的GXM1602NSL液晶模块,它的核心是HD44780。与W78E58的数据传输采用8位并行传输,可显示两行共32个点阵字符。HD44780支持用户自定义字符,故可以通过编程将频率、幅度、波形等汉字及数字信息显示出来。还采用了通信接口(RS232)与PC机相联,PC机的控制命令可以通过TXD(Pin10)和RXD(Pin11)与W78E58进行交互,控制信号源的输出。

基于FPGA控制AD9854产生正弦波

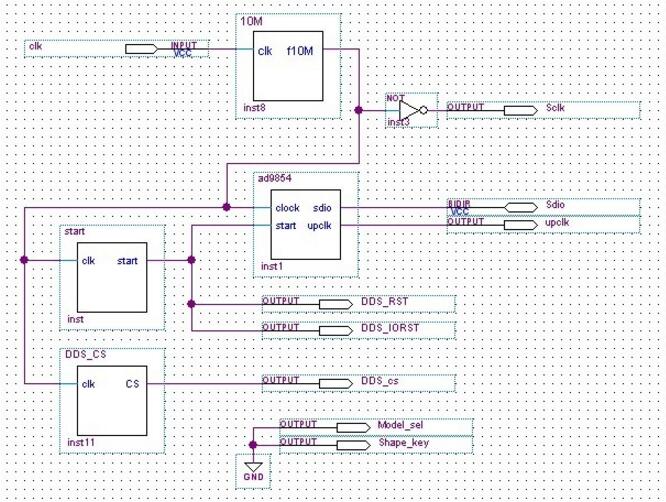

用FPGA控制AD9854产生雷达信号源,这里主要向大家介绍如何在FPGA中利用verilog语言(硬件描述语言)控制AD9854产生正弦波。由于我们采用SPI总线的形式实现,主要涉及到时钟信号、片选信号以及正弦波的控制字编写。首先向大家展示一下顶层框图,我们是在QUARTUSII8.1环境下运行的。具体见图一:

从上图可以看出,基于FPGA控制产生正弦波,主要包含以下几部分:

A:时钟分频部分;B:DDS控制信号部分;C:AD9854控制字部分。

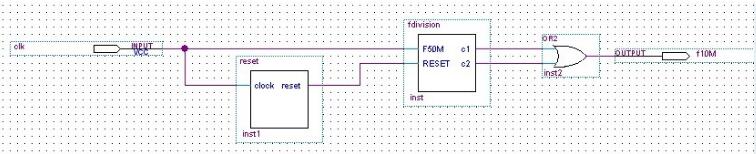

(一)时钟分频部分

由于我们从外部输入的为50MHZ,而对于SPI总线,根据其协议,时钟一般为100KHZ或者400KHZ,我们用的是10MHZ,涉及到5分频电路设计。具体设计见下图所示:

(二)DDS控制信号部分

AD9854芯片的复位信号,模式选择信号以及片选信号,都在这部分包含,在这里我们将模式选择和波形关键字信号引脚,直接引至地线处理。AD9854复位和I/O口复位信号都是依靠时钟信号的。片选信号是在时钟信号出现一段时间后产生DDS芯片的片选信号。

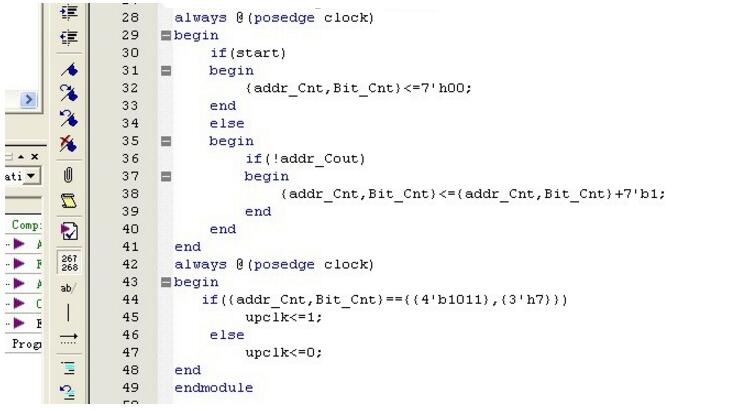

(三)AD9854控制字部分

这部分主要涉及如何很好的把握时序,我们将预先计算好的控制存在预定的存储器中,通过时钟同步信号有序的读取这些控制字。具体关键部分见下图:

-

如何判断AD9854芯片2013-11-08 3311

-

AD9854产生三角波调频信号2014-05-14 4172

-

求解答:stm32驱动AD98542015-04-10 6730

-

求430单片机控制ad9854产生6Mhz正弦信号的程序和硬件连接方式2015-05-05 5057

-

请教一下AD9854的使用2015-08-08 3120

-

求解AD9854幅度的输出问题2016-12-13 4066

-

fpga如何控制AD9910产生正弦波2017-07-01 3348

-

用ad9854产生单音正弦波外部io update工作不正常2018-09-20 1777

-

AD9854输出波形有失真2018-09-25 2790

-

利用AD9854生成一个迸发型的正弦波是否可行2018-12-20 3030

-

AD9854 ASK矩形输出不正确2018-12-21 1663

-

为什么ad9854产生的正弦波幅度会随频率变化?2019-07-18 3123

-

用ad9854产生单音正弦波,外部io update工作不正常是什么原因?2023-12-19 756

-

基于AD9854产生MSK调制信号详细说明2018-05-16 7648

-

AD9854的FPGA程序免费下载2020-11-16 1148

全部0条评论

快来发表一下你的评论吧 !