对比ARM、DSP,深入了解FPGA

描述

自1985年首款FPGA诞生以来,FPGA已经是一名在电子信息领域征战了30年的老兵,这名战功赫赫的老兵如今已经正式开赴了一个新的战场。但是FPGA并不是万能的。相对于串行结构处理器,其设计的灵活性是以工作量的增加为代价的。FPGA与ARM、DSP(如下图所示)的比较如下。

一、从语言本身的差异来看,基于Verilog HDL和VHDL的硬件语言与C/C++相比,在代码灵活性、开发效率等方面还有较大差距。通常一段十几行的C语言代码使用硬件语言实现后,代码量会增加到几十行之多。同时,在进行硬件语言描述时,一个合格的FPGA工程师不仅要实现相应的逻辑功能,还要在头脑里浮现编写的代码所生成的逻辑结构,并考虑到门延时对系统时序的影响。这样才能够设计出稳定高效的逻辑结构,减少后期时序调整的工作。

二、从语言本身的差异来看,基于Verilog HDL和VHDL的硬件语言与C/C++相比,在代码灵活性、开发效率等方面还有较大差距。通常一段十几行的C语言代码使用硬件语言实现后,代码量会增加到几十行之多。同时,在进行硬件语言描述时,一个合格的FPGA工程师不仅要实现相应的逻辑功能,还要在头脑里浮现编写的代码所生成的逻辑结构,并考虑到门延时对系统时序的影响。这样才能够设计出稳定高效的逻辑结构,减少后期时序调整的工作。

三、从工作频率来看,ARM、DSP等处理器采用的是成熟的内核结构,具有较好的时序特性,其最高频率通常为600MHz~1.25GHz。为提高处理能力,TI等芯片厂商采用多核的设计方式,设计了具有8核DSP、8核ARM的处理器,每个核心的最大工作频率可 达1.25GHz,通过设置可以开启和关闭其中的内核来灵活地协调功耗与处理能力之间的矛盾。目前TI公司正在设计具有8核ARM+8核DSP的处理器,来满足高速系统中集中运算的需求。而在FPGA的设计中,不同的系统具有不同的最高工作频率,该频率可以在编译报告中获得。对于Altera公司的FPGA,通过TimeQuest工具调整时序,可以提升设计工程的最高频率。一个具有良好设计的FPGA工程的最高频率可达150MHz以上。

四、从执行方式来看,基于嵌入式平台的C/C++语言在已有的硬件结构中执行,只需正确配置相关寄存器即可。而使用硬件语言的设计需自行设计硬件结构,在生成结构前还要经过前仿真、综合、布局布线、后仿真等步骤,开发周期较长。这一情况在较为复杂的FPGA工程设计中尤为严重。例如,一个添加了4个DDR2的IP的工程在i5处理器、4G内存的计算机上,编译时间甚至在20min以上。

五、从算法应用来看,ARM、DSP等处理器中集成了加法器、乘法器等运算单元,尤其是在DSP中,可以在一个周期内进行8×8位甚至16×16位的乘法运算。同时,这些处理器还支持浮点运算能力。而FPGA对这部分运算并不擅长,即使在较为简单的加法运算中,若进行加法的两个数据具有较高的位宽,由于传统的加法中的进位方式是串行结构,所以在其生成的结构中会产生较长的门延时,从而会降低时序的余量,甚至会降低系统编译后的最高工作频率。

六、从算法设计来看,在ARM、DSP等处理器中设计算法前,需要提前构思算法的流程图,然后进行代码的编写。而在FPGA设计中,主要包含三种设计方式:面向状态的设计,面向活动的设计和面向结构的设计。

(1)面向状态的设计是以状态机为代表的设计方式,即通过控制信号和时序信号触发状态机进行状态的迁移。状态机的设计是FPGA开发中必不可少的环节,这部分内容将 在7.2.2节中详细叙述。

(2)面向活动的设计是以数据流和流程图为代表的设计方式。尤其是在传输系统、实时算法设计中,常使用基于数据流的设计方式。常见的数据流的操作方式包括数据的寄存器同步缓冲、数据传递、数据运算与流水设计、数据的存取等。

(3)面向结构的设计常用于较大的系统设计中,用于描述模块与模块、单元与单元之间的互联关系,主要包括数据信号与控制信号。根据不同的层次描述,主要可以分为系统级结构描述、寄存器级结构描述、门级结构描述等。

为了解决这些硬件工程师所面临的问题,Altera Xilinx等FPGA公司不遗余力地对开发平台进行了完善,如下以Altera的解决方案为例。

对于第一点提及的设计语言的问题,Altera推出了Qsys(SOPC)等片上软核,使工程师在FPGA中同样可以使用更为灵活的C语言进行编程。Qsys(SOPC)中包含了片内、片外存储器、定时器及各种接口等IP,使工程师可以按需定制自己的片内处理器。使用这种方式,在一定程度上缓解了硬件描述语言开发周期过长的缺点,也成为一种对FPGA系统进行前期功能验证的有效手段。

对于第二点提及的通用模块或接口占用开发周期的问题,Altera和供应商设计了大量具有知识产权的IP(Intellectual Property,知识产权),包括运算类、通信类、数字信号处理类、门类、输入/输出类、接口类、JTAG扩展类、存储类等多种类别。这些IP是经过严格测试和优化过的,其中部分IP免费,上面提到的SOPC中应用的大部分IP都是免费的。

值得注意的是,尽管大部分基本功能的IP可以在不同系列的FPGA间通用,依然有一些IP并不支持所有系列的FPGA,使用这些IP在不同系列的FPGA间进行工程移植时需要注意。所使用的IP是否支持当前芯片,可以在Quartus II的MegWizard管理器中查阅,也可以在官网中查阅。Altera支持的所有IP及其适用系列可参考以下网址:http://www. altera.com.cn/products/ip/ip-index.jsp。

对于第三点提到的工作频率的问题,不同的处理器具有不同的应用领域。在高速数据处理过程中,ARM、DSP等固然可达到较高的工作频率,然而相对于FPGA,其高速的优势仅体现在串行结构的算法中。在FPGA的设计中,可利用其硬件设计的灵活性,采用并行算法或将串行算法改造为并行算法,然后在FPGA中实现。经测试,在工作频率为1GHz的DSP中(TMS320C6416),对SDRAM中分辨率为2048×2048的图像进行中值滤波后重新写入SDRAM,耗时为7s;而在FPGA中,完全可以在图像输入时进行实时处理,仅消耗几个时钟周期的处理,近似可认为0延时—实时。

对于第四点提及的编译时间过长的问题,Altera致力于开发新版本的平台,提升编译效率的同时,增加了增量编译的功能。配合区域锁定,可以锁定已编译过且在后续修改中没有改动过的模块,对这部分模块不进行重新编译,从而可减少编译时间。

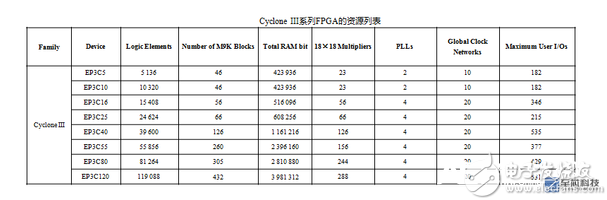

对于第五点提及的运算能力的问题,Altera FPGA中内嵌了多个DSP块。每个DSP块中包含加法器和乘法器结构,根据系列不同,具有不同的数据位宽。多个DSP块中的加法器和乘法器可以互相拼接,从而支持更高位宽的运算。结合相关的运算类IP,可以流水线的形式完成运算,每个周期输出一次计算结果。表1.10为Cyclone III系列FPGA的资源列表。可以看到,与DSP相比,Cyclone III的乘法器资源还是比较丰富的,这使得在FPGA内部进行并行运算成为可能。

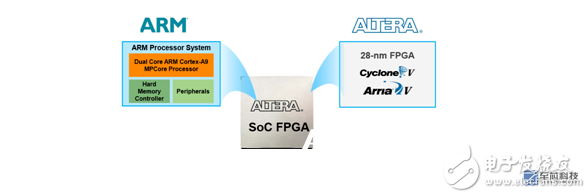

最后,Altera又推出了嵌入了双核28nm的ARM Cortex-A9的FPGA,同时以足够的DSP块和足够的乘法器资源,完善了FPGA+DSP+ARM架构,并以单片SoC FPGA的模式,解决了过往FPGA力所不能及的缺陷,解决了未来多IC集成的前瞻性问题,如图1.28所示。而这却仅仅只是一个开始,在未来Altera FPGA的发展中,更多的以实现FPGA+DSP+ARM为架构,并行实现高速运算,解决过去的难题,不断地突破极限。在未来的数字系统设计中,这必然是一种趋势。

-

深入了解示波器2013-11-14 6138

-

深入了解DSP与ARM的区别与联系2014-01-02 3602

-

深入了解LabVIEW FPGA资料分享2015-05-27 5208

-

Zigbee各版本对比,让你深入了解2016-02-29 5658

-

深入了解DSP2019-05-16 2347

-

对比ARM、DSP,深入了解FPGA2021-06-28 2766

-

深入了解DSP和ARM的关系2021-07-01 722

-

DSP/MCU/ARM/CPLD/FPGA对比分析哪个好?2021-10-22 1615

-

ARM/DSP/FPGA的区别是什么?对比分析哪个好?2021-11-05 1721

-

深入了解示波器入门手册2013-03-27 1473

-

FPGA与ARM、DSP的区别2017-03-15 1190

-

FPGA,arm,stm32,dsp特点对比2021-11-19 1542

-

带你深入了解示波器2022-02-07 964

-

深入了解安全光栅2023-06-25 2152

-

深入了解 GaN 技术2023-12-06 7645

全部0条评论

快来发表一下你的评论吧 !