如何使用QuartusⅡ软件来编写FPGA?

电子说

描述

如何使用QuartusⅡ软件来编写FPGA

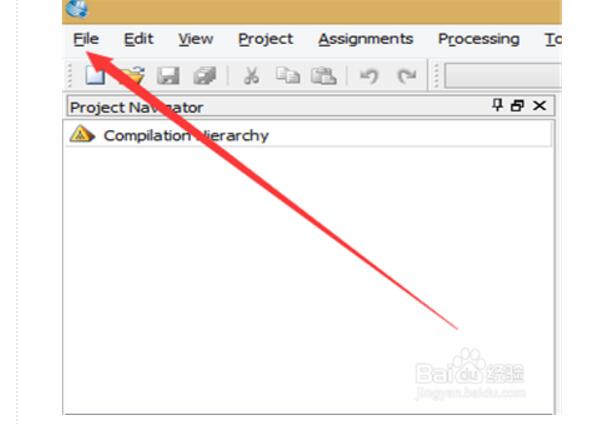

1、首先现在桌面上找到Quartus II软件,之后双击打开。打卡之后会有一个初始界面(如图)。

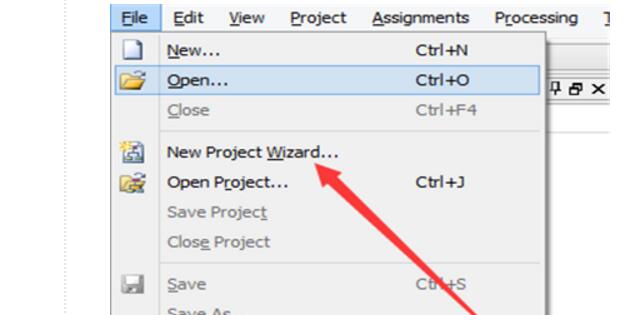

2、在此界面左上方找到File点击,出现菜单选择New Progect wizard选项点击。

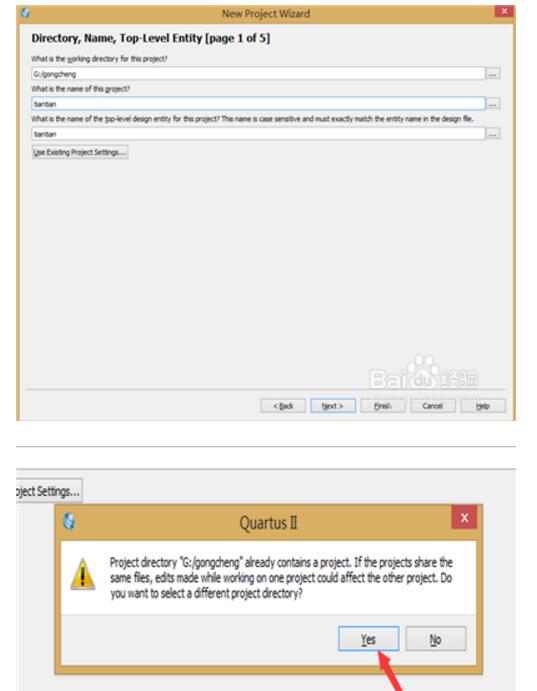

3、弹出新的界面之后,点击下方的下一步即可。新界面选好自己事先准备的文件夹,之后给工程起名字。点击下方下一步。此时会弹出一个英文框点击其中的No.

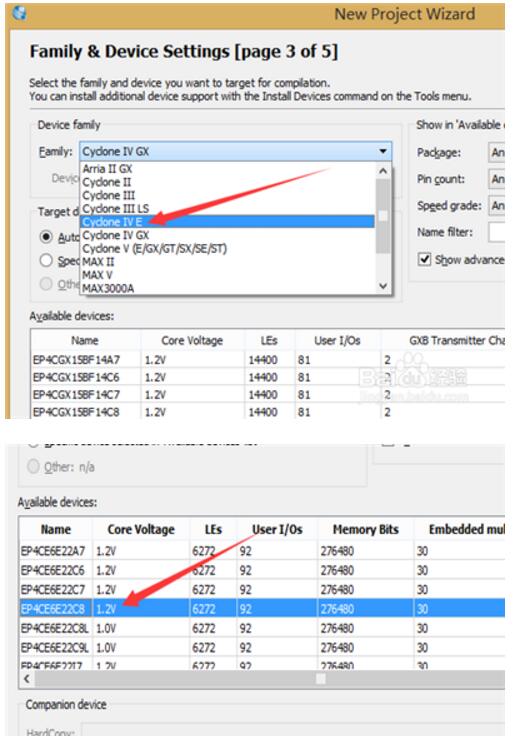

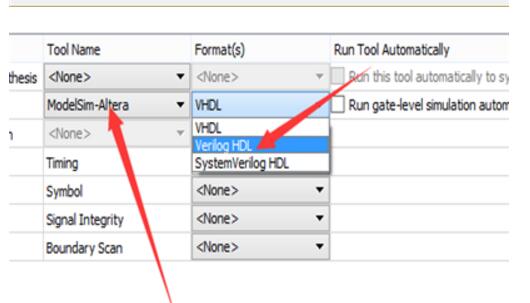

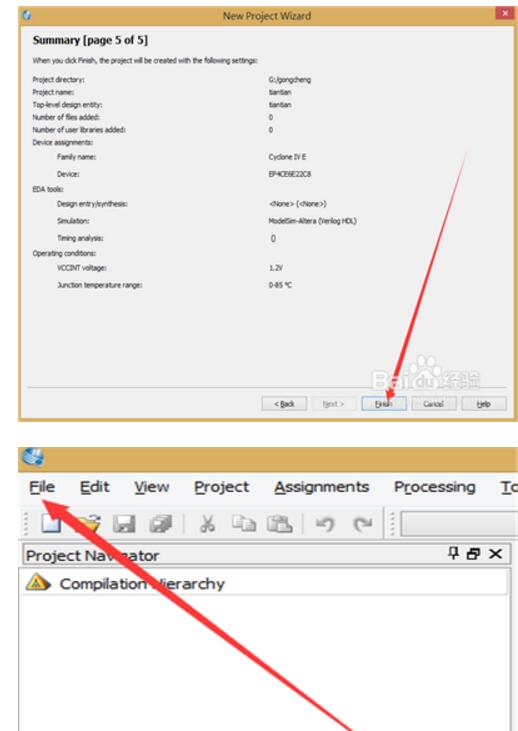

4、之后弹出的界面就可以不加改动直接选择下方的下一步知道下图界面出现,按图选择选项(Cyclone IV E),芯片类型选择EP4CE6E22C8芯片之后点击下一步之后按图三选择(ModelSim-Altera和Verilog HDL这两个选项),点击下一步。

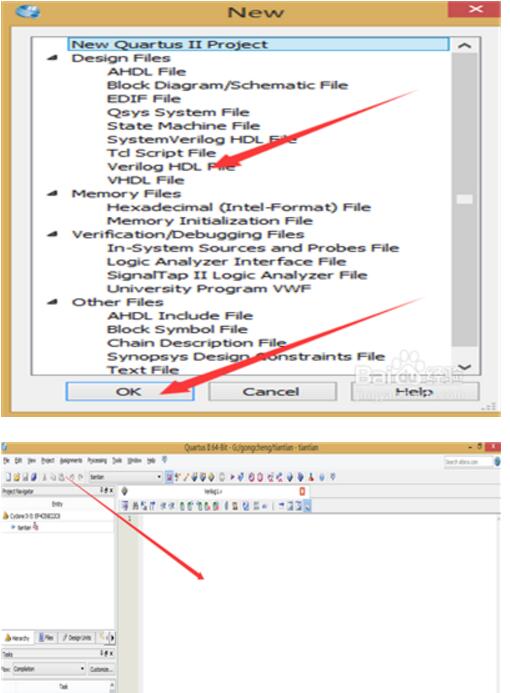

5、最后在新界面点击完成。再次点击左上角的File,在菜单中选择第一项New,之后弹出新界面选择Verilog HDL File选项之后点击下方的OK,就可以在空白处填写你要练习的程序了。

Quartus II仿真入门教程

一、建立工作库文件和编辑设计文文件

任何一项设计都是一项Project(工程),而把一个工程下的所有文件放在一个文件夹内是一个非常好的习惯,以便于我们整理,利用和提取不同工程下的文件,而此文件夹将被EDA软件默认为Work Library(工作库),所以第一步先根据自己的习惯,建立个新的文件夹。

下来进入正题:

(1)新建文件夹:我的习惯在D盘建立并保存工程,我将文件夹取名addition counter,路径为D:addition counter

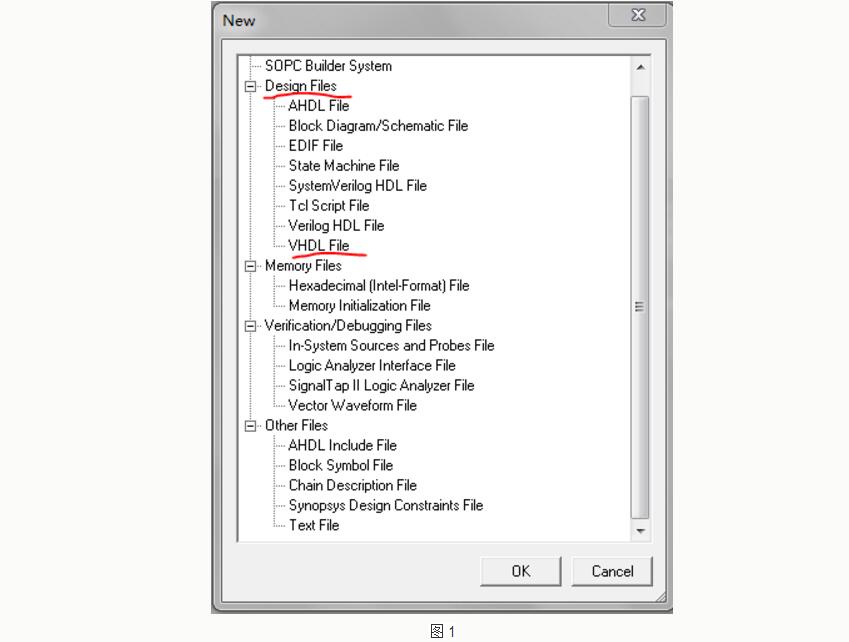

(2)输入源程序:打开Quartus II,选择菜单File--》New--》Design Files--》VHDL File--》OK(如图1所示)

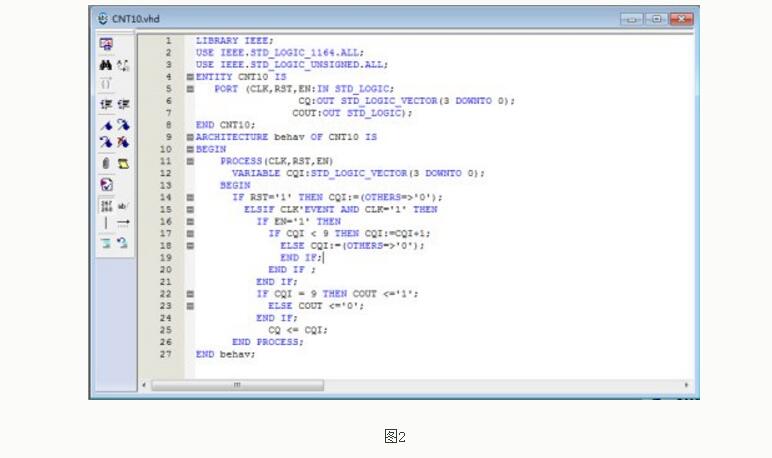

在VHDL文件编译器窗口键入程序,如图2所示,源程序附在文章的最后,可以直接复制粘贴

(3)保存文件:完成一步就保存一步是一个好习惯,这样即使出现意外情况,也不至于以前的努力付诸东流。选择File--》Save as,选择保存路径,即刚才新建的文件夹D:addition counter,文件名应与实体名保持一致,即CNT10.vhd,点击保存后会跳出“Do you want to create a new project with this file?”选择“是”,则进入如下界面

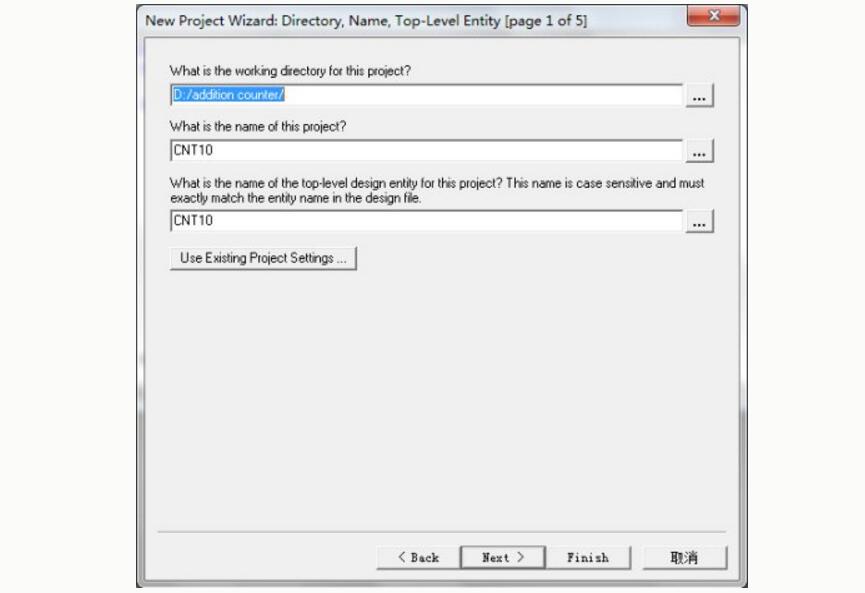

点击Next,进入“工程设置”对话框,如图所示

第一行 表示工程所在的文件夹即D:addition counter,第二行为工程名,可以与顶层文件的实体名保持一致,也可以另取别的名字,第三行为当前工程顶层文件的实体名。

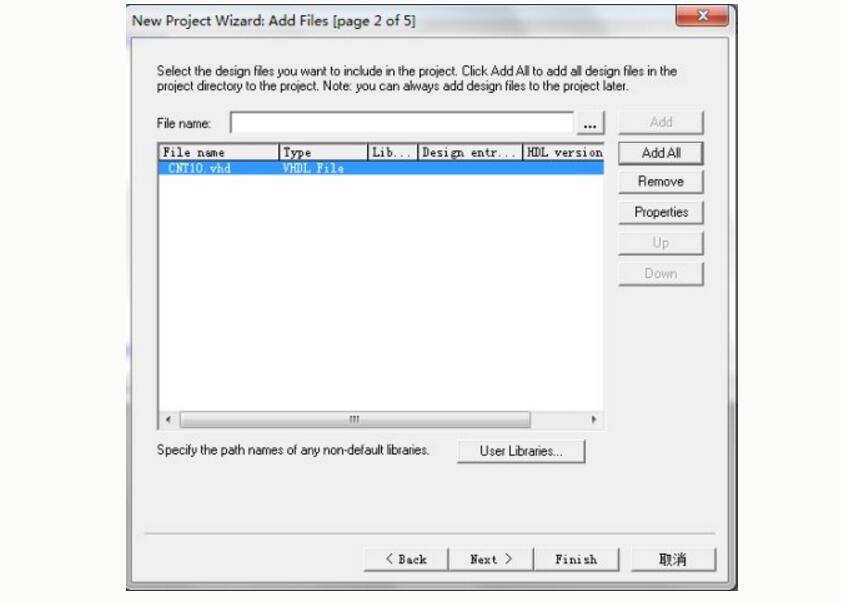

点击next,进入ADD FILE对话框,如图所示,单击Add All 按钮,将工程相关的所有VHDL文件加进工程,也可以单击“Add 。。。”选择性加入,按此步骤建立工程,工程已经自动将所有文件加进去了,可以直接点击next,当先直接建立工程时,需要自己添加

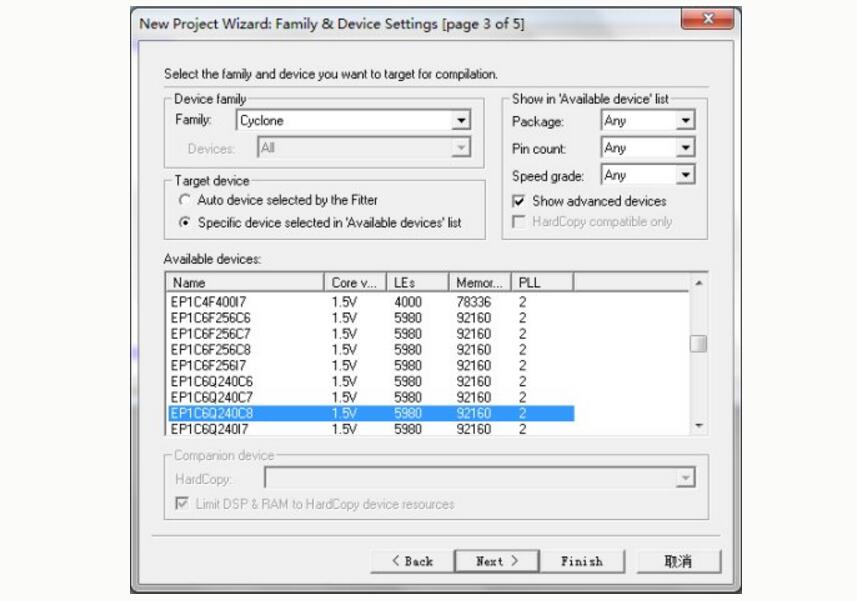

(4)选择目标芯片:我们选用的是飞思卡尔的Cyclone系列的EP1C6Q240C8,在Family栏选择芯片系列——Cyclone,然后软件会在Avalable devices栏中该系列的所有芯片,寻找EP1C6Q240C8并选中,点击Next,如图所示

(5)工具设置:进入EDA工具设置窗口,有三个选项,分别是选择输入的HDL类型和综合工具、选择仿真工具、选择时序分析工具,这是除Quartus II自含的所有设计工具以外的外加的工具,如果不作选择的,表示仅选择Quartus II自含的所有设计工具,本次不需要其他的设计工具,可以直接点击Next

(6)结束设置:进入“工程设置统计”窗口,列出了与此工程相关的设置情况,设置完成,点击Finish

二、编译前设置

1、选择目标芯片并选择配置器件的工作方式

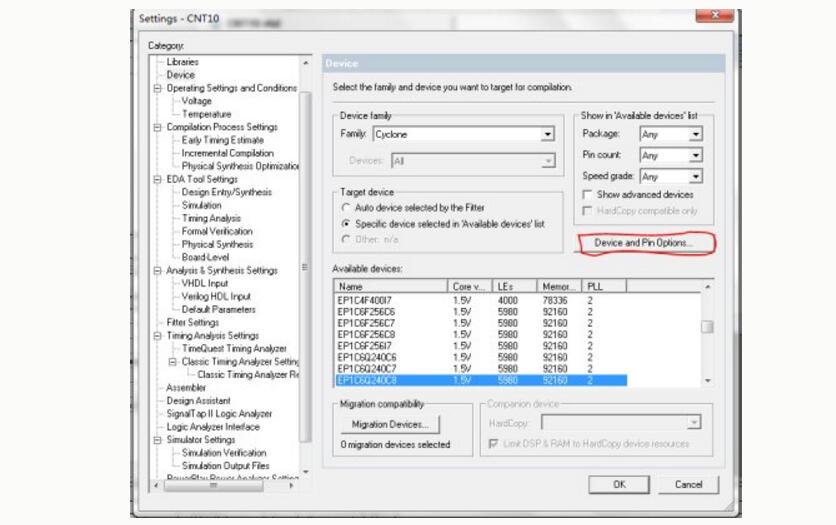

在菜单栏选择Assignments--》Device,弹出对话框,因为刚才在建立工程的时候已经选择了目标芯片,所以直接进入选择配置器件的工作方式,点击Device & Pin Options,如图所示

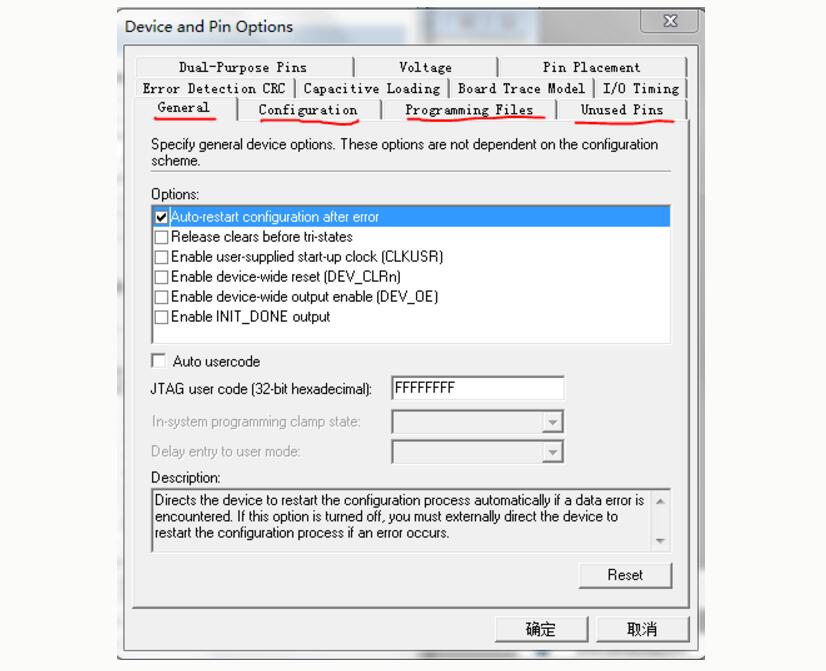

弹出Device & Pin Options窗口,分别对General、Configuration(配置器件)、Programming File、Unused Pins(不用的引脚)项进行设置,如图所示

General项中,在Options栏中选择Auto-restart configuration after error,使对FPGA的配置失败后能自动重新配置,每当选中Options栏中的任一项时,下方的Description栏中有对该选项的描述供参考。

Configuration项中将Generate compressed bitstreams处打钩,产生压缩配置文件

Programming File选项保持默认即可

Unusual Pins项把不用的引脚全部置高,即As Input tri-stated

点击确定

三、编译

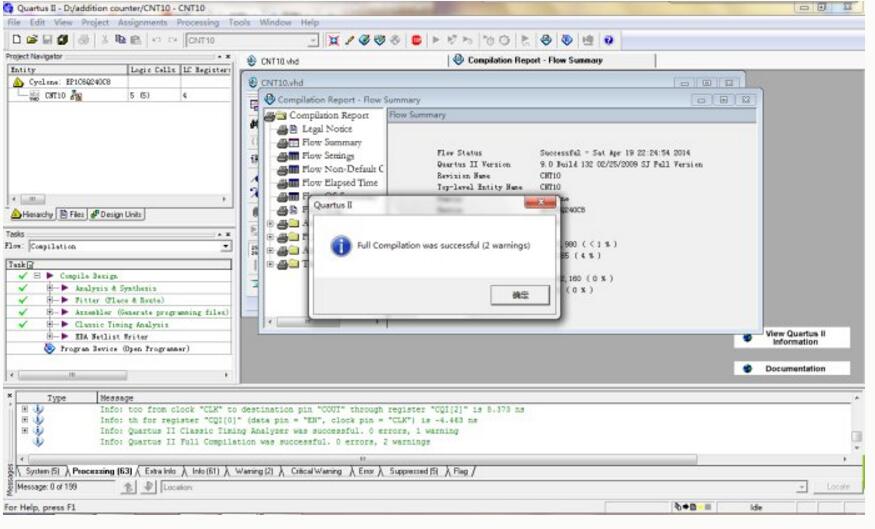

配置好后就可以进行编译了,点击

启动全程编译

编译成功后的界面如图所示

四、时序仿真

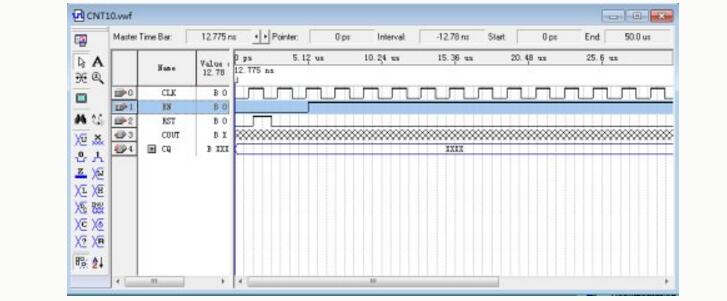

(1)打开波形编辑器:File--》New--》Verification/Debugging Files--》Vector Waveform--》OK,即出现空白的波形编辑器,如图所示

(2)设置仿真时间区域:Edit--》End Time在Time栏中输入50,单位选择“us”,点击确定并保存波形文件

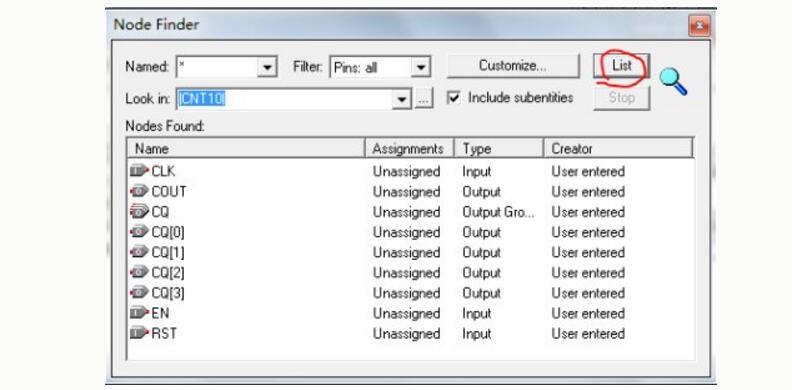

(3)将工程CNT10的端口信号名选入波形编辑器中:View--》Utility windows--》Node Finder,在Filter框中选Pins:all(通常是默认选项),然后点击List,则显示出了所有引脚,如图所示

将重要的端口名拖进波形编辑器后关闭窗口

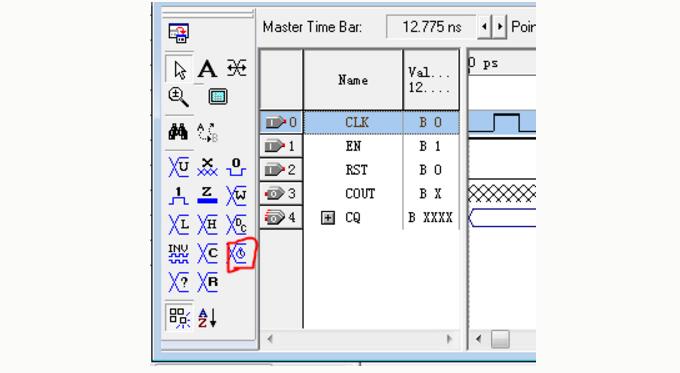

(5)编辑输入波形:

单击窗口的时钟信号名CLK使之变蓝,再单击左列的时钟设置键,如图所示

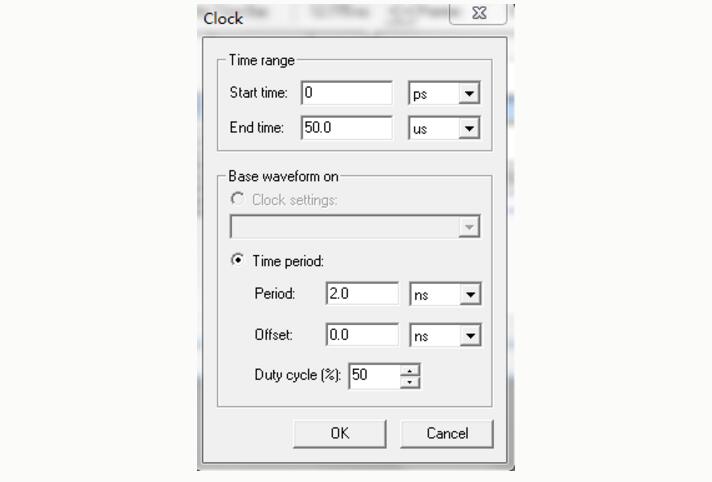

Duty Cycle(占空比)默认50,时钟周期Period为2us,点击OK,如图所示

在最初设计的时候可能默认的时间间隔比较小,没有显示出方波,而是一条直线,这时需要调整时间轴,单击左列放大镜的图标,将鼠标放在波形上,左键放大,右键缩小,点击几下右键即可看见明显的方波了。其他的输入端口的波形界面上圈出需要置高的地方,点击左列的“1”,按照此方法编辑输入波形,如图所示

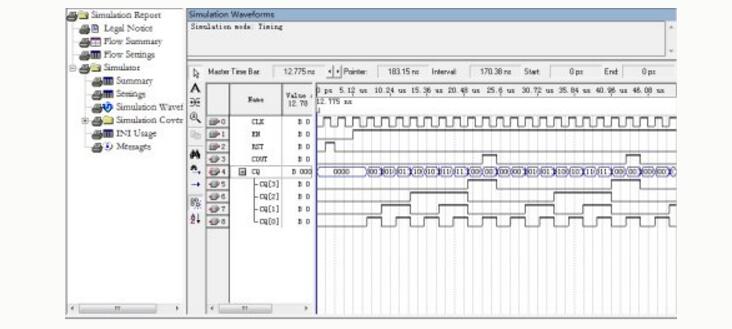

(6)启动仿真器:Processing--》Start Simulation ,直至出现Simulation was successful,仿真结束,然后会自动弹出

“Simulation Report”,点击输出信号“CQ”旁边的“+”,展开总线中的所有信号,可以更利于我们观察和分析波形,如图所示

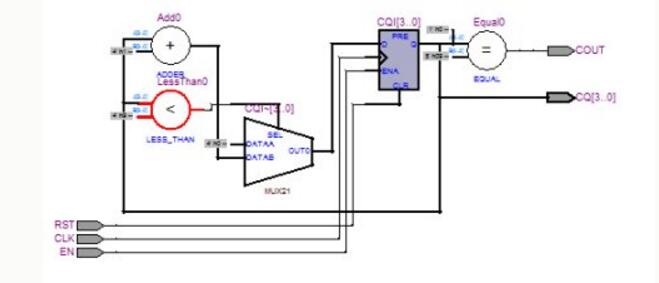

五、应用RTL电路图观察器

Tools--》Netlist Viewers--》RTL Viewer,结果如图所示

附件1:源代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT (CLK,RST,EN:IN STD_LOGIC;

CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT:OUT STD_LOGIC);

END CNT10;

ARCHITECTURE behav OF CNT10 IS

BEGIN

PROCESS(CLK,RST,EN)

VARIABLE CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST=‘1’ THEN CQI:=(OTHERS=》‘0’);

ELSIF CLK‘EVENT AND CLK=’1‘ THEN

IF EN=’1‘ THEN

IF CQI 《 9 THEN CQI:=CQI+1;

ELSE CQI:=(OTHERS=》’0‘);

END IF;

END IF ;

END IF;

IF CQI = 9 THEN COUT 《=’1‘;

ELSE COUT 《=’0‘;

END IF;

CQ 《= CQI;

END PROCESS;

END behav;

-

FPGA基础教程系列—Quartus工程建立2011-09-07 2990

-

Quartus II软件12.0的新功能详解2012-11-06 18751

-

Quartus II的FPGA设计详细手册2012-03-08 36761

-

Quartus II 软件13.1的新特性2013-11-13 10435

-

FPGA设计开发软件Quartus的使用技巧2011-06-15 1171

-

基于Quartus_II_的FPGACPLD开发2016-05-20 1006

-

FPGA-Quartus II各个器件源码2017-03-19 1408

-

Quartus-16.0.0.211-windows软件免费下载2018-04-19 2317

-

Altera推出Quartus II v13.0,支持实现世界上最快的FPGA设计2018-09-25 1628

-

FPGA verilog相关视频:quartus中的qsys的讲解2019-08-06 3897

-

Quartus官方的Verilog教程使用FPGA的典型电路设计和实现等资料说明2019-09-20 2184

-

使用Quartus II编程CPLD和FPGA设备的教程说明2020-09-17 2256

-

Altera Quartus II设计软件的简介手册免费下载2021-01-29 1586

-

综合性CPLD/FPGA软件Quartus 13.0下载2021-09-12 2253

-

quartus 12.1软件下载2023-04-18 1088

全部0条评论

快来发表一下你的评论吧 !