设计师原理图设计中常见的错误总结

EDA/IC设计

描述

十年间的差异

10年前,原理图设计非常简单,原理图的错误检查似乎也不需要太多的人力支出。 然而10多年过去了,我们的设计日趋复杂。设计中包含多个多引脚器件、以及大型电路板接插件的电路时,可能会有大量的风险隐患被带入到制造流程。

对此,我们都知道其后果 — 返工。

最近我与Altium公司,针对Valydate的原理图完整性分析检查相关的新技术,进行了一次促膝长谈。在过去的几年,设计师在原理图设计过程所犯的错误,让我们受益匪浅。这对我们、对设计师都大有裨益,因为这让我们了解到,在原理图设计过程中究竟会出现多少潜在错误,其中有多少错误能真正通过人工检查发现。

从小处着手

Valydate公司有一段有趣的历史。我们原本想要开发一款用于原理图完整性分析的EDA工具,而那时并没有足够多的投资。这该如何解决呢?于是我们从小处入手,通过提供服务来提升技术,通过客户的真实工程评估进行技术推广。

这样做是否有效?答案是肯定的。我们从客户那儿获取报告,发现设计师在原理图检查过程中一直犯的类似错误,这其中有些可能就是你所犯的。

在设计错误中寻找共同点

Valydate在2011年至2012年的两年时间里,为数百份原理图运行了验证报告。我们将调查结果分成两大类:

关键错误。这包括原理图中出现的错误,如果置之不理,很有可能影响设计。

设计缺陷。虽然没有关键错误那样严重,但很有可能会导致元件功能缺失。

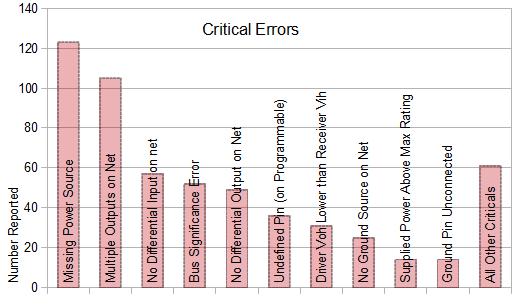

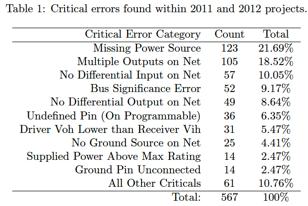

关键设计错误

我们对原理图检查中发现的关键设计错误的种类感到十分惊讶。高达21%的关键设计错误与电源缺失相关,18%与单点网络多输出相关。您在设计过程中是否也犯过这些错误?

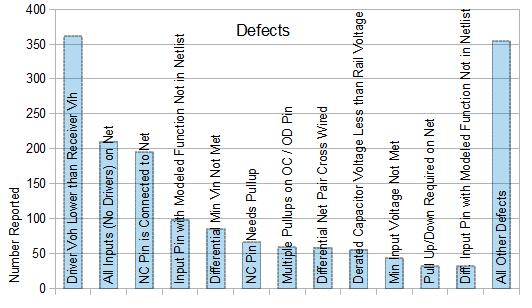

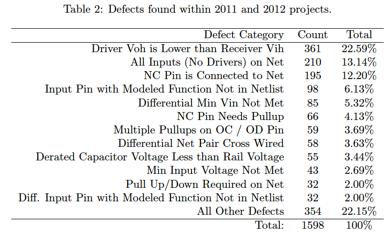

设计缺陷错误

设计缺陷本身也反映出一些有趣的现象,潜在的设计缺陷远远多于关键错误。最常见的是哪些呢?驱动端voh低于接收端vih占了22%。这些情况您是否熟悉呢?

设计错误共性

我觉得最吸引人的是,在我们2年研究的尾声阶段,找出了设计错误之间的共性。这与设计师所犯的一次性错误不同。此次研究有数百个不同的原理图,它们都有着相同的设计缺陷。

我并不认为这是设计师的错。原理图设计审核包含太多方面。每发布一次,错误都会接踵而来。总的来说,在原理图审核过程中,涉及了太多的人为因素。您怎么知道是什么原因导致了设计缺陷?

实用的解决方案

在总结了2年的研究成果后,我们发现一个常见设计错误的共同趋势——它们都涉及电源网络、可编程器件和不适当的上拉/下拉电阻。除了原理图分析工具,我们为设计师总结了8条设计时必须牢记的实用技巧,希望大家能够避免一些或所有这方面的设计错误。

电源网络解决方案

在设计原理图时,确保每个所需的电路板电压都有定义的电源网络,并保持网络名一致。如果网络名称不完全相同,可能会产生错误连接。

一定要检查每个有源器件的电源引脚,确保连接的电源有正确的最小和最大电压。

为原理图上的接地网络设置清单,确保每个接地网络都有特定的接地源。

养成如下习惯:确认每个使用元器件的原理图符号包括用于原理图设计阶段进行人工审核的标签,而且要确保并使用与器件数据手册上相同的引脚定义。

可编程器件和电阻缺失的解决方案

如果您在设计中使用了可编程器件,请确保您的电路板网表与器件相连,且引脚定义准确。

验证可编程引脚定义与电路板需要的定义并无冲突。混合引脚配置可能会导致错误,尤其当定义为输出的FPGA被定义成输入时。

设计过程中,尽早与FPGA团队沟通,针对引脚名称、方向、技术、上拉/下拉阻抗、电源电压等方面,达成一致意见。

验证设计中的所有开漏网络,确保其至少有一个上拉/下拉电阻。

时间问题

最后,这归结于您愿意投入多少时间进行原理图审核。十多年前,只要人工审核即可,然而现在的原理图太过复杂,我们无法面面俱到进行人工验证。

我们真正需要的,是一套能够运行所有审查的原理图完整性分析工具,从而让您腾出时间去处理更紧迫的事情。Valydate正在攻克这个难题,几周之后,我们很高兴与Altium Designer共同推出另一款全新扩展应用,它可以为您自动化原理图审查过程。让我们敬请期待!

Michael是一位卓越的商业领袖,这些年不断推动建立客户和雇员忠诚度,持续为公司带来不断增长的利润和市场份额,同时对全球研发团队进行指导。

供职于Valydate前,Michael曾在Nortel Networks、CoreSim和Fidus Systems等多家公司的担任管理职位,包括业务拓展、销售、运营,以及工程部门。正是在他的带领下,Fidus Systems公司得以进军硅谷。目前,Michael担任Valydate公司的CEO,该公司于2010年由他参与创建。

Michael拥有卡尔顿大学计算机系统工程学士学位,以及渥太华大学工商管理行政硕士学位。他享有众多荣誉和奖项,是OBJ 2009 Forty under Forty奖项得主。

-

浅谈原理图和PCB图的常见错误2012-08-12 0

-

原理图和PCB常见错误2013-12-25 0

-

原理图中常见的器件标识2020-03-16 0

-

电路原理图及PCB布线常见错误有哪些?2021-03-18 0

-

这些常见的错误,合格的工程师一眼就能看出来2021-04-25 0

-

PCB设计原理图常见错误2021-11-11 0

-

PROTEL原理图常见错误2010-03-15 1589

-

一文了解PCB中常见14大错误2018-07-22 5939

-

简要分析PCB中常见错误2018-11-18 3779

-

PCB作业中常见14大错误2019-03-12 4122

-

PCB原理图设计时的常见错误有哪些2019-09-11 2996

-

UI设计师的10个常见错误,你是否中招了?2020-09-03 1959

-

电路原理图及PCB布线常见错误资料下载2021-04-05 1083

-

PCB设计中常见的错误与解决方法2021-11-06 864

-

PCB设计工作中常见的错误有哪些?2023-05-23 1496

全部0条评论

快来发表一下你的评论吧 !