简谈FPGA研发设计相关规范(企业中很实用)

描述

大家好!又到了每日学习的时间了,今天我们聊一聊FPGA做开发的时候,有哪些设计规范,从文档到工程建立等,聊一聊也许你会学到很多东西,少走很多弯路哦!

在团队项目开发中,为了使开发的高效性、一致性、正确性,团队应当要有一个规范的设计流程。按照规范来完成项目的设计开发工作,归类清晰明了的工程文件夹级别;项目应拥有良好风格和完整的文档,如设计思路与调试记录及器件选型等;代码书写高效,即统一的书写规范,文件头包含的信息完整,无论自己还是团队他人阅读便一目了然。

一、文档命名:

清晰的文档命名能够让我们思路非常的清晰,所以FPGA工程文件夹的目录要求层次鲜明,归类清晰。一个工程必须要有一个严整的框架结构,用来存放相关的文档、设计,不仅方便自己查看,也提高了项目的团队工作效率。

下面我们来举例说明:

一级文件夹为工程名

二级文件夹多个:

用以存放源文件

用以存放Testbench文件

用来存放设计思路相关类的文件

用来存放IP 核的文件

等等…

二、设计文档化:

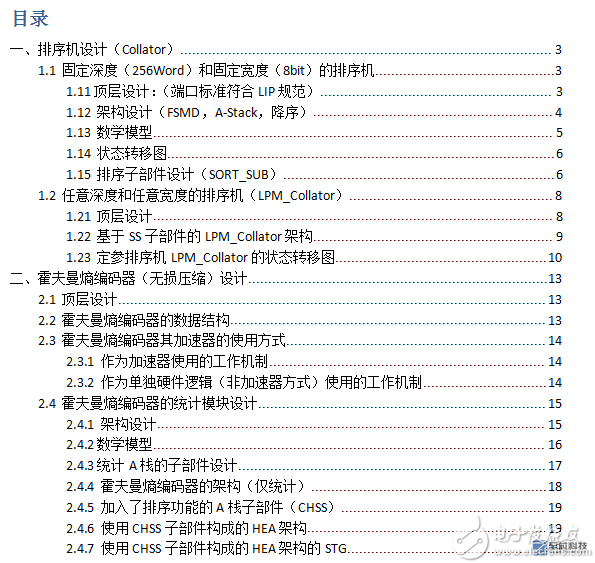

将自己对设计的思路和调试记录在文档中,有利于以后对模块功能的添加和维护,并且在项目联调时方便项目组其他人员读代码。也方便不同厂家的FPGA之间移植,以及FPGA到ASIC的移植。如下图就是设计文档化的举例说明,文档介绍清晰,功能分析明确,有利于以后对模块功能的添加和维护。

设计思路:按照项目的要求,自顶向下的分成若干模块,分别编写功能。顶层尽量只做行为描述,逻辑描述在底层编写。模块的编写要有硬件电路思维方式,每一个模块的设计都应考虑是否存在该硬件电路,尽量采用同步设计。

三、编程风格:

每个module应存在于单独的源文件中,源文件名应与其所包含的模块名相同。每个设计都应该有一个完善的文件头,包含公司名称、设计者、设计时间、文件名、所属项目、模块名称及功能、修改记录及版本信息等内容。代码中的标识符采用传统C语言的命名方法,在单词之间用下划线分开,采用有意义,能反应对象特征、作用和性质的单词命名标识符,以此来增强程序的可读性。为避免标识符过于冗长,较长的单词可以适当的缩写。

四、代码规范:

低电平有效的信号,后缀名要用“_n”,比如低电平有效的复位信号“rst_n”

模块名和信号名统一小写

变量名要小写,如wire、reg、input、output等定义的

变量命名应按照变量的功能用英文简洁表示出来“xxx_xxx_xxx”,避免过长

采用大写字母定义常量参数,参数名小于20个字母,如parameter TIME=20

时钟信号应前缀“clk”,复位信号应前缀“rst”

对于顶层模块的输出信号尽量被寄存

三态逻辑避免在子模块使用,可以在顶层模块使用

到其它模块的接口信号按:输入、(双向)、输出的顺序定义端口

一个模块至少要有一个输入、输出,避免书写空模块

时钟事件的表达式用“posedge”或“negedge”的形式

If语句嵌套不能太多

建议不要使用include语句

建议每个模块添加timescale

代码中给出必要的注释

每个文件有个一头文件

每个文件只包含一个模块

模块名和文件名保持一致

异步复位,用if(xxx==1’b1) 或 if(xxx==1’b0)

同步时序逻辑的always block中有且只有一个时钟信号,并且在同一个沿动作

采用同步设计,避免使用异步逻辑

一般不要将时钟信号作为数据信号的输入

不要在时钟路径上添加任何buffer

在顶层模块中,时钟信号必须可见

不要采用向量定义的方式定义一组时钟信号

不要在模块内部生成时钟信号,使用pll产生

尽量不使用任务

不使用事件变量

不使用系统函数

不使用disable语句

尽量不使用forever、repeat、while等循环语句

不使用不可综合的运算符

在一个always语句中有且只能有一个事件列表

移位变量必须是一个常数

时序逻辑语块中统一使用非阻塞型赋值

组合逻辑语块中使用阻塞型赋值

- 相关推荐

- 热点推荐

- FPGA

-

简谈FPGA研发设计相关规范(很实用)2024-04-16 1119

-

简谈FPGA的片内资源2024-01-08 629

-

简谈基于FPGA的千兆以太网设计2023-06-01 1217

-

FPGA设计经验谈.zip2022-12-30 525

-

FPGA和USB3.0通信-FX3硬件设计简谈2021-12-01 1344

-

简谈FPGA研发设计相关规范(企业中初入职场很实用)2021-06-30 3103

-

简谈FPGA的设计规范2019-11-14 6669

-

简谈FPGA的上电复位2018-06-18 21110

-

FPGA 研发设计相关 规范(企业中很实用)2018-02-24 4517

-

FPGA至简设计法为什么这么简单2017-12-15 4569

-

国内知名企业招聘FPGA研发工程师2017-03-07 2367

全部0条评论

快来发表一下你的评论吧 !