三分钟你就懂得如何保护射频采样ADC的输入?

RF/无线

描述

任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以是无源(使用变压器或巴伦),具体取决于系统要求。无论哪种情况,都必须谨慎选择元器件,以便实现在目标频段的最优ADC性能。

简介

射频采样ADC采用深亚微米CMOS工艺技术制造,并且半导体器件的物理特性表明较小的晶体管尺寸支持的最大电压也较低。因此,在数据手册中规定的出于可靠性原因而不应超出的绝对最大电压,将当前主流的射频采样ADC与之前的老器件相比,可以发现这个电压值是变小的。

在使用ADC对输入信号进行数字量化的接收机应用中,系统设计人员必须密切关注绝对最大输入电压。该参数直接影响ADC的使用寿命和可靠性。不可靠的ADC可能导致整个无线电系统无法使用,且更换成本也许非常巨大。

为了抵消过压带来的风险,射频采样ADC集成了可以检测高电平阈值的电路,允许接收机通过自动增益控制(AGC)环路调节增益来进行补偿。但是,如果采用流水线型ADC,则与架构相关的固有延迟可能导致输入暴露于高电平之下,从而可能损害ADC输入。本文讨论了一种简单的方法来增强AGC环路,保护ADC。

输入架构

射频采样ADC可采用多种不同的设计,最常见的一种是流水线架构,该架构采用多级级联,将模拟信号转换为数字信号。第一级最重要,可以是缓冲或未缓冲级。选择哪种设计取决于设计要求和性能目标。例如,一个带缓冲器的ADC通常在频率范围内具有更好的SFDR性能,但功耗比不带缓冲器的ADC更高。

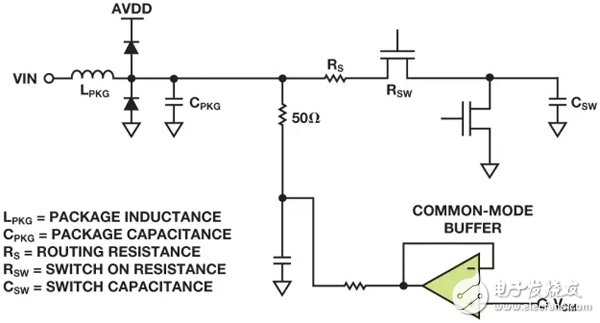

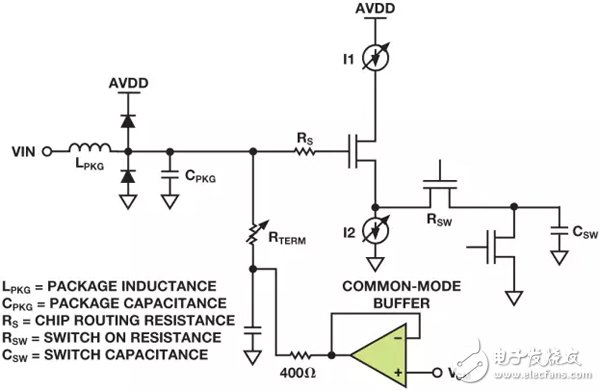

前端设计同样会根据ADC是否有缓冲级而改变。没有缓冲器的ADC需要使用额外的串联电阻来处理输入电荷反冲,它同样会改善SFDR性能。图1和图2显示了AD9625未缓冲和AD9680缓冲射频采样ADC的等效输入电路简化图。为简明起见,仅显示单端输入。

图1. 未缓冲射频采样ADC输入的等效电路

图2. 缓冲射频采样ADC输入的等效电路

无论采用何种架构,ADC输入端可持续的绝对最大电压由MOSFET能够处理的电压决定。缓冲输入更复杂,且比未缓冲输入功耗更大。ADC具有多种不同类型的缓冲器,最常见的一种是源极跟随器。

故障机制

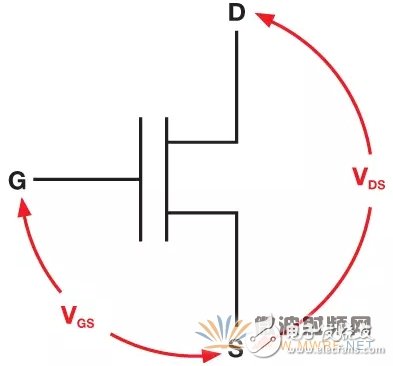

缓冲和未缓冲ADC的故障机制有所不同,但通常是在超出允许的最大栅极-源极电压( (VGS))或漏极-源极电压((VDS))时发生故障。这些电压如图3所示。

图3. MOS晶体管的关键电压

例如,假设VDS超过允许的最大电压,则发生VDS击穿故障,这通常在MOSFET处于关断状态且在漏极施加了相对于源极的过量电压时发生。如果VGS超过允许的最大电压,则它会导致VGS击穿(亦称为氧化层击穿)。这通常在MOSFET处于导通状态且在栅极施加了相对于源极的过量电压时发生。

未缓冲ADC的故障机制

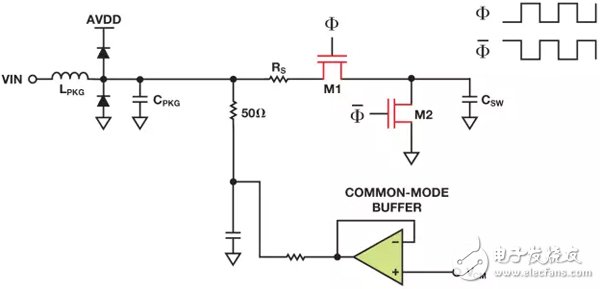

图4显示的是一个未缓冲ADC输入。采样过程由反相时钟信号Φ和Φ控制,它们是MOSFET M1的采样/保持信号以及MOSFET M2的复位信号。M1导通时,M2关断,且电容CSW跟踪信号(采样或跟踪模式)。当M1关断时,MDAC中的比较器作出判断后M2导通,电容CSW复位。这样可在采样阶段使采样电容为下一次采样做好准备。该电路通常工作状态优良。

但是,高压输入使M2暴露在超出其漏源电压的应力之下。当对输入高压进行采样(M1导通、M2关断)时,M2会暴露于较大的VDS之下,其在不足采样时钟半周期的时间内处于关断状态,但哪怕只是瞬时的暴露也会降低电路的可靠性,导致ADC随时间失效。在复位模式下(M1关断、M2导通),因M1的漏极上有输入信号,从而也会暴露于大的VDS电压。

图4. 未缓冲ADC输入的故障模式

缓冲ADC的故障机制

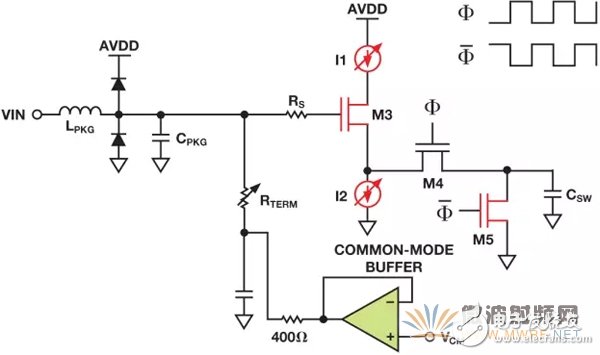

图5显示的是一个缓冲ADC输入。采样和复位信号适用相同的时钟方案。无论相位如何,当缓冲器M3栅极暴露于高压输入时,产生电流I1以及I2。电流源I1采用PMOS晶体管实现,而I2采用NMOS晶体管实现。M3栅极上的高电压导致I1和I2 MOSFET产生过大的VDS。此外,M3栅极上的高电压还可导致氧化层击穿。

图5. 缓冲ADC输入的故障模式

缓冲和未缓冲ADC的击穿机制有所不同,因此绝对最大输入电压同样有所不同,如表1所以。

表1. 缓冲与未缓冲ADC的绝对最大值规格

ADC工艺

(nm)输入结构绝对最大

输入电压(V)差分摆幅

(V p-p)

14位105 MSPS350缓冲79.2

14位125 MSPS180未缓冲2.04.5

16位250 MSPS180缓冲3.66.0

12位2.5 GSPS65未缓冲1.524

14位1.0 GSPS65缓冲3.24.6

使用TVS二极管保护ADC输入

有几种方式可以保护ADC输入不受高压影响。部分ADC(特别是射频采样ADC)具有内置电路,可以检测输入电压并在超过设定阈值时进行上报。如数据手册中所述,该快速检测输出存在一些延迟,因此依然会使ADC输入端短时间内暴漏于高压之下。

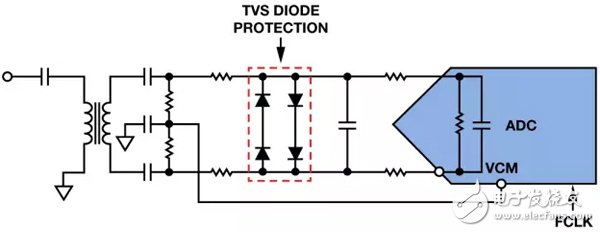

瞬态电压稳定器(TVS)二极管可以限制过量电压,但会在正常工作期间影响ADC性能。图6显示的是一个使用TVS二极管的过压保护电路。

图6. 带TVS二极管保护的ADC前端电路

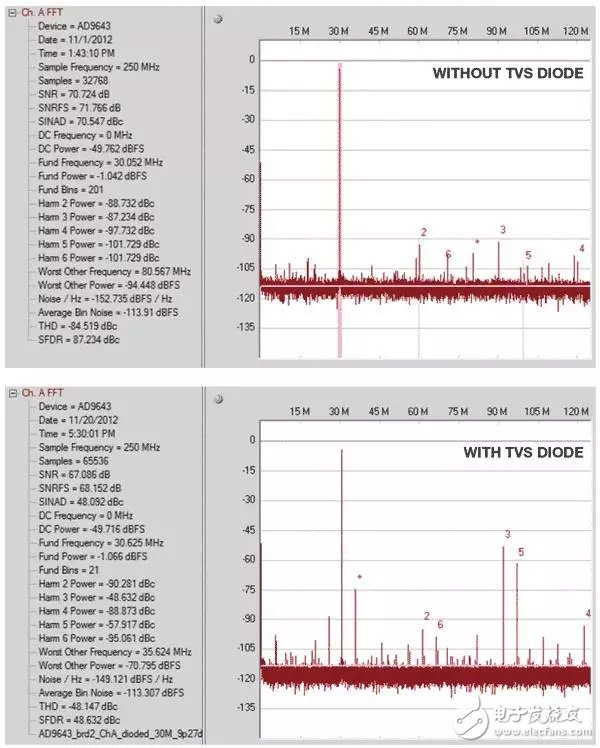

虽然TVS二极管通过箝位过量电压保护ADC输入,但它们会极大地恶化谐波性能。图7显示了具有30 MHz、–1 dBFS输入的14位、250 MSPS无缓冲ADC的前端带与不带TVS二极管时的FFT比较情况。

图7. 带与不带TVS二极管保护的ADC前端电路FFT比较

TVS二极管会极大地恶化奇次谐波性能,因为它们在不作用为箝位的时候就相当于一反向偏置二极管。该PN二极管具有结电容CJ0,该电容与ADC内部开关动作产生的非线性反冲电流互相作用,产生一个与模拟输入信号混合的电压信号。该混合信号在ADC内部被采样,产生极大的三次谐波。在过压条件下的时域曲线(图8)显示了TVS二极管的箝位削压的功能。这并不表示TVS二极管不适合用来保护ADC输入,只是必须仔细考虑二极管规格,以便达到性能要求。选择二极管类型及其参数时必须作更全面的考虑。

图8. 前端电路中的TVS二极管保护导致削波信号

使用肖特基二极管保护射频采样ADC输入

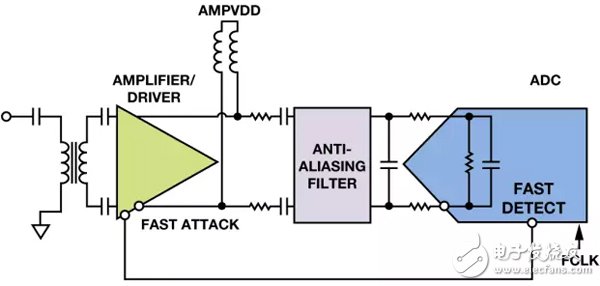

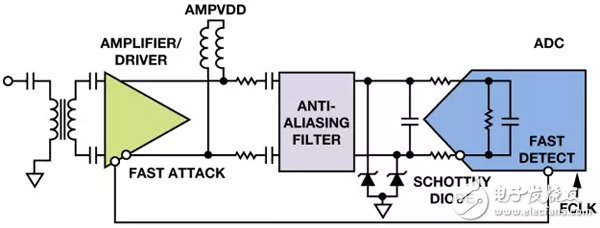

当带宽和采样速率达到GHz和GSPS级别时,射频采样ADC可以简化无线电接收机设计,因为它们不需要ADC前具有很多的混频级,但这样会让ADC输入易受过压应力影响。图9显示的是用于射频采样ADC的典型前端设计,采用放大器驱动。新一代放大器专为与这些ADC实现接口而设计,具有快速攻击响应输入管教,可通过串行外设接口(SPI)配置,将输出衰减为预定增益。快速攻击响应引脚可以配置为响应射频采样ADC的快速检测输出。ADA4961是具有快速攻击响应功能的新一代放大器实例。AD9680和AD9625是具有快速检测功能的射频采样ADC实例。

图9. 带快速攻击响应功能的放大器驱动带快速检测功能的射频采样ADC

只要输入电压处于合理的范围之内,图9中的拓扑便能工作良好。举例而言,假如该接收机的输入端收到突发高压信号,则放大器的输出将上升至放大器电源轨的电压水平(本例中为5 V)。这将产生巨大的电压摆幅,超过ADC输入端的绝对最大额定电压。快速检测功能存在一定延迟(AD9680-1000为28个时钟周期或28 ns),因此等到快速检测逻辑输出告诉放大器置位快速攻击响应时,ADC早已暴露在高压下数个时钟周期。这可能降低ADC的可靠性,因此无法承受这种风险的系统设计必须采用第二保护模式。具有极低器件和寄生电容的快速响应肖特基二极管在这种情况下十分管用。特定二极管的关键参数可参见数据手册。

反向击穿电压(VBR)——AD9680输入引脚上的最大输入电压——相对于AGND约为3.2 V,因此为该二极管选择数值为3 V的反向击穿电压。

结电容(CJ0)——二极管电容应尽可能低,确保正常工作时二极管不影响ADC的交流性能(SNR/SFDR)。

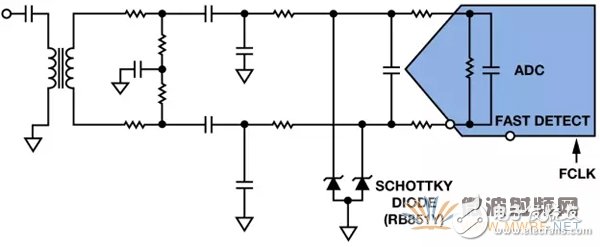

图10显示的是无源前端,肖特基二极管位于ADC之前。无源前端比较容易演示肖特基二极管在不影响交流性能情况下对ADC输入端的保护。

图10. 显示射频采样ADC和肖特基二极管的无源前端电路

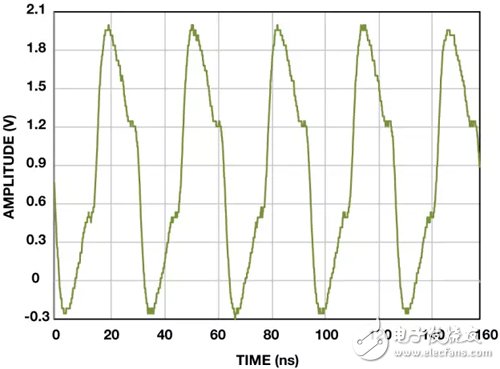

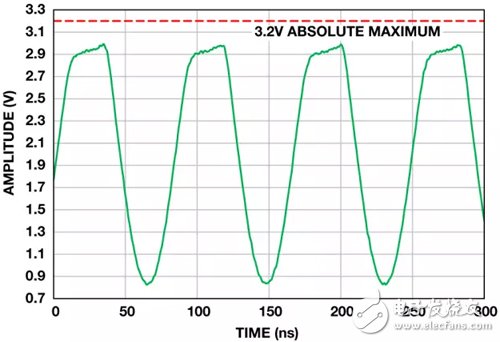

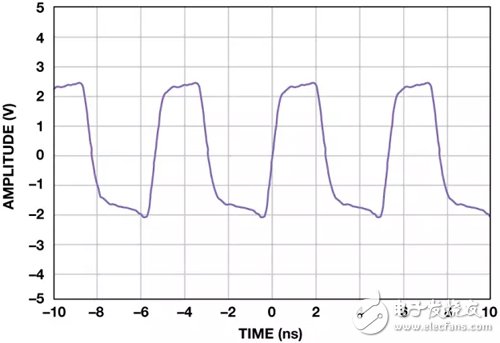

这颗射频采样ADC经过测试可输入高达2 GHz频率的信号,因此选用RF肖特基二极管(RB851Y)。表2显示RB851Y的关键参数;表明该器件适合该应用。测试结果显示二极管防止了ADC输入电压超过其3.2 V的绝对最大电压(相对于AGND)。图11显示的是一个单端输入(ADC的VIN+引脚)暴露在高压之下(185 MHz)的情况。肖特基二极管将电压箝位至3.0 V左右(相对于AGND),防止ADC输入达到3.2 V限值。图12显示的是在肖特基二极管箝位下的AD9680输入端的差分信号。

表2. 用于保护射频采样ADC输入的肖特基二极管关键参数

参数数值单位注释

反向电压(VR)3VAD9680数据手册中,绝对最大额定电压值为VIN± = 3.2 V

端点之间的电容

(CJ0, 或Ct)0.8pF正常条件下对ADC性能影响较小

图11. 肖特基二极管箝位的单端ADC输入

图12. 肖特基二极管箝位AD9680差分输入信号

下一步,我们测量正常工作性能。AD9680按照数据手册中的建议进行控制,但输入如图10所示进行修改。模拟输入频率变化范围为10 MHz至2 GHz。CJ0的超低数值应当不会对ADC的SNR和SFDR性能造成影响。

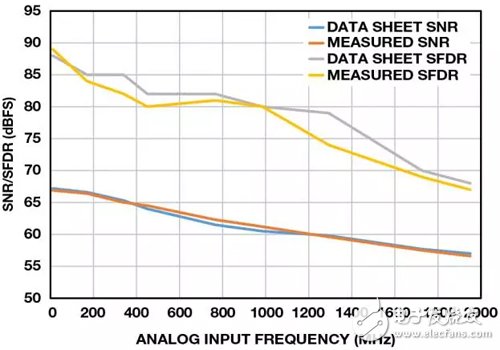

图13. AD9680带肖特基二极管保护时SNR/SFDR与模拟输入频率的关系

肖特基二极管根本不会影响SNR性能,但某些频率下SFDR与预期值有所偏差,如图13所示。这可能是由于差分信号失配或ADC反冲所导致的。评估板是从直流到2 GHz的宽频段设计,因此当它在整个频段内的整体工作良好时,某些元器件可能在特定频率下与肖特基二极管相互作用。

大部分应用不会用到整个2 GHz频段,因此可以通过修改过压保护的输入电路,将前端调谐至所需的目标信号带宽。谨慎选择肖特基二极管可以保护ADC输入,因而系统设计人员可以使用具有最新快速攻击响应功能和快速检测功能的放大器驱动前端电路,如图14所示。

图14. ADA4961驱动AD9680(显示射频采样ADC和肖特基二极管)

结论

本文讨论如何使用肖特基二极管保护射频采样ADC输入,使其免受过压应力的影响。仔细审查二极管的数据手册参数很关键。为了实现最佳的目标频段性能,需要对该电路的实施进行规划。射频采样ADC的快速检测输出可以与最新放大器的快速攻击响应功能进行配合,设置自动增益控制环路。

-

免费三分钟2009-03-02 4504

-

射频采样ADC输入保护:这不是魔法2018-11-01 3228

-

让程序运行三分钟,停一分钟,循环下去,直到设置停止循环的位置2022-06-08 11036

-

三分钟让你明白电池为什么会鼓包2009-11-12 71542

-

三分钟能做什么?三分钟能让我的iPhone6s重启N次!2017-02-25 2781

-

小米扫地机器人台湾开售 三分钟售罄2017-04-07 1421

-

如何保护射频采样ADC的输入?2017-11-22 1461

-

如何保护射频采样ADC的输入2020-09-29 857

-

三分钟概述8类常用元器件资料下载2021-03-28 1564

-

Brocade帮助Netzlink实现三分钟云服务供应2023-08-29 406

-

快乐解说MCU:三分钟,带你了解低功耗MCU2023-09-18 2071

-

三分钟实现MQTT协议网关串口连接三菱FX3UPLC上传腾讯云2023-10-23 1882

-

三分钟看懂雪崩光电二极管2023-11-23 3417

-

三分钟了解飞创直线电机运动模组特点、选型及应用-FCL系列2024-02-05 1279

-

Node-RED初学者教程-三分钟学习2024-06-27 6810

全部0条评论

快来发表一下你的评论吧 !