LCD驱动分析_LCD控制器设置及代码详解

电子说

描述

1. LCD工作的硬件需求:

要使一块LCD正常的显示文字或图像,不仅需要LCD驱动器,而且还需要相应的LCD控制器。在通常情况下,生产厂商把LCD驱动器会以COF/COG的 形式与LCD玻璃基板制作在一起,而LCD控制器则是由外部的电路来实现,现在很多的MCU内部都集成了LCD控制器,如S3C2410/2440等。通 过LCD控制器就可以产生LCD驱动器所需要的控制信号来控制STN/TFT屏了。

2. S3C2440内部LCD控制器结构图:

我们根据数据手册来描述一下这个集成在S3C2440内部的LCD控制器:

a:LCD控制器由REGBANK、LCDCDMA、TIMEGEN、VIDPRCS寄存器组成;

b:REGBANK由17个可编程的寄存器组和一块256*16的调色板内存组成,它们用来配置LCD控制器的;

c:LCDCDMA是一个专用的DMA,它能自动地把在侦内存中的视频数据传送到LCD驱动器,通过使用这个DMA通道,视频数据在不需要CPU的干预的情况下显示在LCD屏上;

d:VIDPRCS接收来自LCDCDMA的数据,将数据转换为合适的数据格式,比如说4/8位单扫,4位双扫显示模式,然后通过数据端口VD[23:0]传送视频数据到LCD驱动器;

e:TIMEGEN由可编程的逻辑组成,他生成LCD驱动器需要的控制信号,比如VSYNC、HSYNC、VCLK和LEND等等,而这些控制信号又与REGBANK寄存器组中的LCDCON1/2/3/4/5的配置密切相关,通过不同的配置,TIMEGEN就能产生这些信号的不同形态,从而支 持不同的LCD驱动器(即不同的STN/TFT屏)。

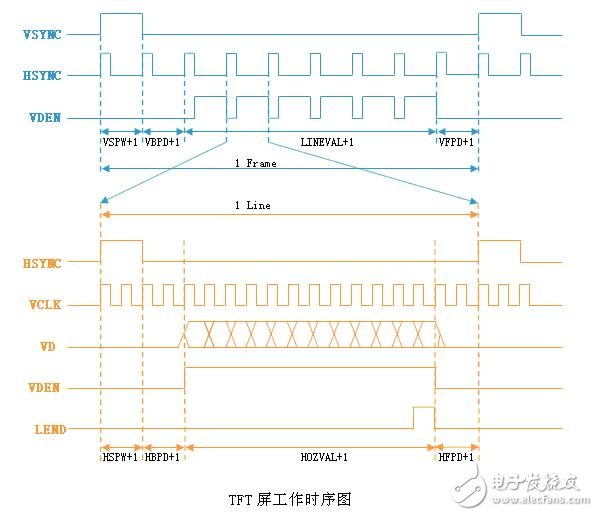

3. 常见TFT屏工作时序分析:

LCD提供的外部接口信号:

VSYNC/VFRAME/STV:垂直同步信号(TFT)/帧同步信号(STN)/SEC TFT信号;

HSYNC/VLINE/CPV:水平同步信号(TFT)/行同步脉冲信号(STN)/SEC TFT信号;

VCLK/LCD_HCLK:象素时钟信号(TFT/STN)/SEC TFT信号;

VD[23:0]:LCD像素数据输出端口(TFT/STN/SEC TFT);

VDEN/VM/TP:数据使能信号(TFT)/LCD驱动交流偏置信号(STN)/SEC TFT 信号;

LEND/STH:行结束信号(TFT)/SEC TFT信号;

LCD_LPCOE:SEC TFT OE信号;

LCD_LPCREV:SEC TFT REV信号;

LCD_LPCREVB:SEC TFT REVB信号。

所有显示器显示图像的原理都是从上到下,从左到右的。这是什么意思呢?这么说吧,一副图像可以看做是一个矩形,由很多排列整齐的点一行一行组成,这些点称之为像素。那么这幅图在LCD上的显示原理就是:

A:显示指针从矩形左上角的第一行第一个点开始,一个点一个点的在LCD上显示,在上面的时序图上用时间线表示就为VCLK,我们称之为像素时钟信号;

B:当显示指针一直显示到矩形的右边就结束这一行,那么这一行的动作在上面的时序图中就称之为1 Line;

C:接下来显示指针又回到矩形的左边从第二行开始显示,注意,显示指针在从第一行的右边回到第二行的左边是需要一定的时间的,我们称之为行切换;

D:如此类推,显示指针就这样一行一行的显示至矩形的右下角才把一副图显示完成。因此,这一行一行的显示在时间线上看,就是时序图上的HSYNC;

E:然 而,LCD的显示并不是对一副图像快速的显示一下,为了持续和稳定的在LCD上显示,就需要切换到另一幅图上(另一幅图可以和上一副图一样或者不一样,目 的只是为了将图像持续的显示在LCD上)。那么这一副一副的图像就称之为帧,在时序图上就表示为1 Frame,因此从时序图上可以看出1 Line只是1 Frame中的一行;

F:同样的,在帧与帧切换之间也是需要一定的时间的,我们称之为帧切换,那么LCD整个显示的过程在时间线上看,就可表示为时序图上的VSYNC。

上面时序图上各时钟延时参数的含义如下:(这些参数的值,LCD产生厂商会提供相应的数据手册)

VBPD(vertical back porch):表示在一帧图像开始时,垂直同步信号以后的无效的行数,对应驱动中的upper_margin;

VFBD(vertical front porch):表示在一帧图像结束后,垂直同步信号以前的无效的行数,对应驱动中的lower_margin;

VSPW(vertical sync pulse width):表示垂直同步脉冲的宽度,用行数计算,对应驱动中的vsync_len;

HBPD(horizontal back porch):表示从水平同步信号开始到一行的有效数据开始之间的VCLK的个数,对应驱动中的left_margin;

HFPD(horizontal front porth):表示一行的有效数据结束到下一个水平同步信号开始之间的VCLK的个数,对应驱动中的right_margin;

HSPW(horizontal sync pulse width):表示水平同步信号的宽度,用VCLK计算,对应驱动中的hsync_len;

对于以上这些参数的值将分别保存到REGBANK寄存器组中的LCDCON1/2/3/4/5寄存器中:(对寄存器的操作请查看S3c2440数据手册LCD部分)

LCDCON1:17 - 8位CLKVAL

6 - 5位扫描模式(对于STN屏:4位单/双扫、8位单扫)

4 - 1位色位模式(1BPP、8BPP、16BPP等)

LCDCON2:31 - 24位VBPD

23 - 14位LINEVAL

13 - 6位VFPD

5 - 0位VSPW

LCDCON3:25 - 19位HBPD

18 - 8位HOZVAL

7 - 0位HFPD

LCDCON4: 7 - 0位HSPW

LCDCON5:

4. 帧缓冲(FrameBuffer):

帧缓冲是Linux为显示设备提供的一个接口,它把一些显示设备描述成一个缓冲区,允许应用程序通过 FrameBuffer定义好的接口访问这些图形设备,从而不用去关心具体的硬件细节。对于帧缓冲设备而言,只要在显示缓冲区与显示点对应的区域写入颜色值,对应的颜色就会自动的在屏幕上显示。

下面看看2440test里面的lcd.c文件

static void PutPixel(U32 x,U32 y,U16 c)

{

if(x《SCR_XSIZE && y《SCR_YSIZE)

LCD_BUFFER[(y)][(x)] = c;

}

很容易发现TFT LCD上显示单个像素的函数实际上很简洁

看来似乎只需要LCD_BUFFER[(y)][(x)] = c这一句话

下面就来分析下,是如何通过这一句话来实现在LCD上显示单个像素的

先分析下LCD_Init()即LCD初始化函数

rLCDCON1 = (LCD_PIXCLOCK 《《 8) | (3 《《 5) | (12 《《 1);

LCDCON1 0x4d000000

#define LCD_WIDTH 240

#define LCD_HEIGHT 320

#define LCD_PIXCLOCK 4

#define LCD_RIGHT_MARGIN 36

#define LCD_LEFT_MARGIN 19

#define LCD_HSYNC_LEN 5

#define LCD_UPPER_MARGIN 1

#define LCD_LOWER_MARGIN 5

#define LCD_VSYNC_LEN 1

CLKVAL[17:8] = 4

TFT: VCLK = HCLK / [(CLKVAL+1) * 2] ( CLKVAL》=0 )

MMODE[7] = 0

PNRMODE[6:5] = 11 TFT LCD panel

BPPMODE[4:1] = 1100 16bpp for TFT

ENVID[0] = 0 Disable

rLCDCON2 = (LCD_UPPER_MARGIN 《《 24) | ((LCD_HEIGHT - 1) 《《 14) | (LCD_LOWER_MARGIN 《《 6) | (LCD_VSYNC_LEN 《《 0);

LCDCON2 0x4d000004

VBPD = 1

VBPD(vertical back porch):表示在一帧图像开始时,垂直同步信号以后的无效的行数,对应驱动中的upper_margin

LINVAL = 240 – 1

LINVAL:LCD屏的垂直大小

VFPD = 5

VFPD(vertical front porch):表示在一帧图像结束后,垂直同步信号以前的无效的行数,对应驱动中的lower_margin

VSPW = 1

VSPW(vertical sync pulse width):表示垂直同步脉冲的宽度,用行数计算,对应驱动中的vsync_len

rLCDCON3 = (LCD_RIGHT_MARGIN 《《 19) | ((LCD_WIDTH - 1) 《《 8) | (LCD_LEFT_MARGIN 《《 0);

LCDCON3 0x4d000008

HBPD = 36

HBPD(horizontal back porch):表示从水平同步信号开始到一行的有效数据开始之间的VCLK的个数,对应驱动中的left_margin

HOZVAL = 320 – 1

HOZVAL:LCD屏的水平大小

HFPD = 19

HFPD(horizontal front porth):表示一行的有效数据结束到下一个水平同步信号开始之间的VCLK的个数,对应驱动中的right_margin

rLCDCON4 = (13 《《 8) | (LCD_HSYNC_LEN 《《 0);

LCDCON4 0x4d00000c

MVAL = 13

HSPW = 5

HSPW(horizontal sync pulse width):表示水平同步信号的宽度,用VCLK计算,对应驱动中的hsync_len

# define LCD_CON5 ((1《《11) | (1 《《 9) | (1 《《 8) | (1 《《 3) | (1 《《 0))

rLCDCON5 = LCD_CON5;

LCDCON5 0x4d000010

HWSWP = 1 Swap Enable

PWREN = 1 Enable PWREN signal

INVVFRAME = 1 VFRAME/VSYNC pulse polarity Inverted 选择负极性脉冲

INVVLINE = 1 VLINE/HSYNC pulse polarity Inverted 选择负极性脉冲

FRM565 = 1 5:6:5 Format

rLCDINTMSK |= 3;

INT_FrSyn = 1 LCD frame synchronized interrupt Masked

INT_FiCnt = 1 LCD FIFO interrupt Masked

rTCONSEL &= (~7);

rTCONSEL &= ~((1《《4) | 1);

MODE_SEL = 0 Sync mode

RES_SEL = 0 320 x 240

LPC_EN = 0 LPC3600 Disable

rTPAL = 0x0;

Temporary palette register enable bit Disable

volatile static unsigned short LCD_BUFFER[SCR_YSIZE][SCR_XSIZE];

#define LCD_ADDR ((U32)LCD_BUFFER)

#define M5D(n) ((n)&0x1fffff)

rLCDSADDR1 = ((LCD_ADDR 》》 22) 《《 21) | ((M5D(LCD_ADDR 》》 1)) 《《 0);

rLCDSADDR2 = M5D((LCD_ADDR + LCD_WIDTH * LCD_HEIGHT * 2) 》》 1);

rLCDSADDR3 = LCD_WIDTH;

LCDSADDR1 0x4d000014 帧缓冲起始寄存器1

LCDBANK[29:21] = (U32)LCD_BUFFER 》》 22

These bits indicate A[30:22] of the bank location for the video buffer in the system memory. LCDBANK value cannot be changed even when moving the view port. LCD frame buffer should be within aligned 4MB region, which ensures that LCDBANK value will not be changed when moving the view port. So, care should be taken to use the malloc() Function

系统内存地址A[30:22]处的Bank位置为图像缓冲。LCDBANK的值在视图移动的值在视图移动时不能改变,LCD帧缓冲应该在4MB区域对齐,保证LCDBANK的值在移动视图时不会改变。

LCDBASEU[20:0] = ((U32)LCD_BUFFER 》》 1)&0x1fffff

For dual-scan LCD : These bits indicate A[21:1] of the start address of the upper address counter, which is for the upper frame memory of dual scan LCD or the frame memory of single scan LCD.

For single-scan LCD : These bits indicate A[21:1] of the start address of the LCD frame buffer.

双扫描:表明高地址计数器的起始地址A[21:1],用于LCD双扫描的上部帧内存或者单扫描的帧内存

单扫描:表明LCD帧缓冲的起始地址A[21:1]

LCDSADDR2 0x4d000018帧缓冲起始寄存器2

LCDBASEL[20:0] = ((LCD_ADDR + LCD_WIDTH * LCD_HEIGHT * 2) 》》 1)& 0x1fffff

= (LCD_ADDR 》》 1 + LCD_WIDTH * LCD_HEIGHT)& 0x1fffff

For dual-scan LCD: These bits indicate A[21:1] of the start address of the lower address counter, which is used for the lower frame memory of dual scan LCD.

For single scan LCD: These bits indicate A[21:1] of the end address of the LCD frame buffer.

LCDBASEL = ((the frame end address) 》》1) + 1

= LCDBASEU + (PAGEWIDTH+OFFSIZE) x (LINEVAL+1)

双扫描:表明低地址计数器的起始地址A[21:1],用于LCD双扫描的下部帧内存或者单扫描的帧内存

单扫描:表明LCD帧缓冲的结束地址A[21:1]

LCDSADDR3 0x4d00001c帧缓冲起始寄存器3

OFFSIZE = 0

PAGEWIDTH = 320 虚拟屏页宽(半字数量) 定义了帧中的视图域宽度

程序分析至此,大概已经清楚是如何通过LCD_BUFFER[(y)][(x)] = c来实现在LCD上显示单个像素了。

就是在设置好各个LCD寄存器之后,通过将LCD_BUFFER地址与LCDBANK以及LCDBASEU、LCDBASEL对应之后,通过改变LCD_BUFFER里不同单元存储的值(即像素的颜色),即可在LCD相应位置上做出显示。

那么在应用不同LCD的时候,只需对LCDCONx以及LCDSADDRx做出相应的配置,在创建一个数组,做出上述的地址映射即可。

关于VCLK计算,由于配置的是TFT,可用到公式VCLK = HCLK / [(CLKVAL+1) * 2] ( CLKVAL》=0 )

设置的FLK为400MHz,HCLK为100MHz,CLKVAL = 4,因此VLCK = 10MHz

-

如何使用示波器解决LCD控制器调试难题2016-12-09 3003

-

EP7212上的LCD控制器是如何驱动彩色LCD的?2021-06-03 1682

-

LCD控制器的设置2022-01-21 851

-

S3C2410驱动TFT LCD的设计应用2008-09-10 1477

-

ARM芯片S3C2410驱动TFT LCD的研究2009-11-12 939

-

通用的TFT-LCD显示控制器的设计与实现2012-08-29 2618

-

基于FPGA的LCD控制器设计2015-10-29 789

-

LCD基础及S3C2410_LCD控制器2016-01-13 1138

-

基于FPGA设计LCD显示控制器相关知识详解2017-12-01 1695

-

基于ARM处理器的LCD控制与触摸屏接口设计(详解)2017-12-02 2143

-

MAX32650上的LCD控制器介绍如何配置LCD定时参数2018-10-09 4431

-

了解LCD驱动(FrameBuffer)的实例开发2019-04-02 1551

-

LCD控制器/驱动器ST7565S芯片手册2021-06-09 1699

-

瑞萨MCU内置LCD控制器/驱动器漫谈2023-09-28 2120

-

什么是LCD控制器?爱普生LCD控制器的作用和功能、概述和产品列表2024-10-09 2210

全部0条评论

快来发表一下你的评论吧 !