ad7606应用电路图大全(五款ad7606应用电路)

IC应用电路图

描述

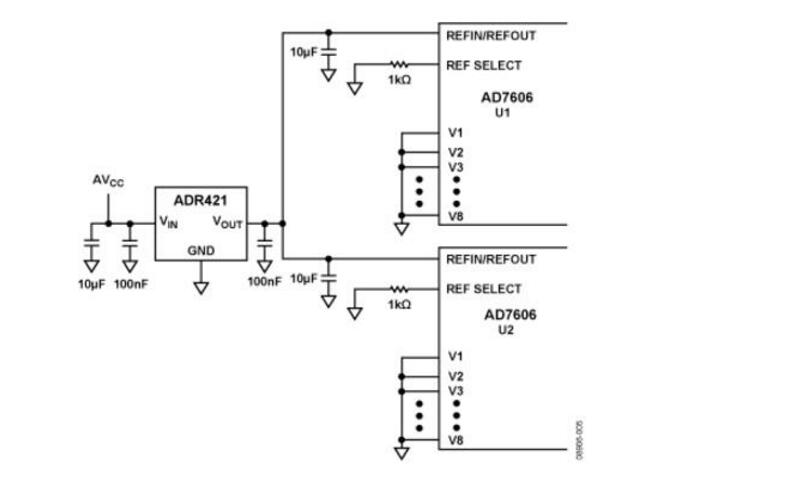

ad7606应用电路一:

在高通道数系统中,良好的通道间和器件间性能匹配可以大大简化校准程序。AD7606器件、模拟输入通道和去耦电容的对称布局有助于多个器件之间的性能匹配。使用公共系统基准电压将能进一步增强系统的匹配性能。图5显示所有输入接地时,用于测量板上16个通道之间性能匹配的电路配置。还有最多7个码的分布直方图,各通道直方图的中心为码0,如图6所示。

基于16位8通道DAS AD7606的可扩展多通道同步采样数据采集系统的布局考虑

图5. 用于测试16通道系统通道间匹配的电路示意图,该系统采用两个AD7606和外部基准电压源ADR421,所有输入接地。

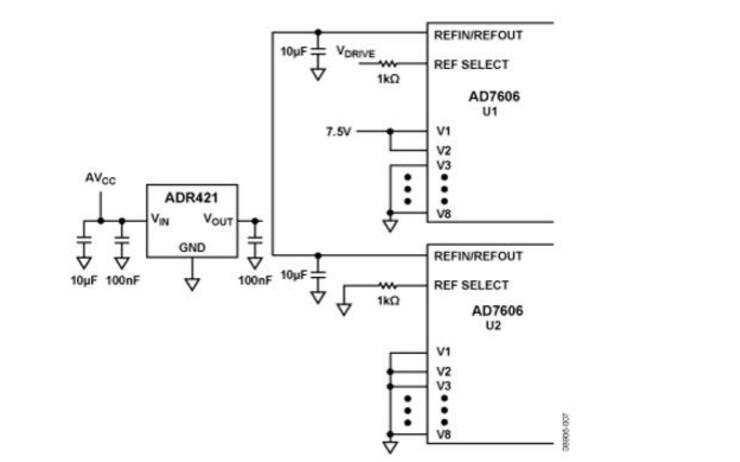

ad7606应用电路二:

AD7606采用5V单电源供电,可以处理±10V和±5V真双极性输入信号,同时所有通道均能以高达200 kSPS的吞吐速率采样。输入箝位保护电路可以耐受最高达±16.5V的电压。它采用单电源工作方式,具有片内滤波和高输入阻抗,因此无需驱动运算放大器和外部双极性电源。AD7606-6抗混叠滤波器的3 dB截止频率为22 kHz;当采样速率为200 ksps时,它具有40 dB抗混叠抑制特性。灵活的数字滤波器采用引脚驱动,可以改善信噪比(SNR),并降低3 dB带宽。如图7所示。

图7. 用于测试一个AD7606通道间匹配的电路示意图,使用U1内部基准电压源

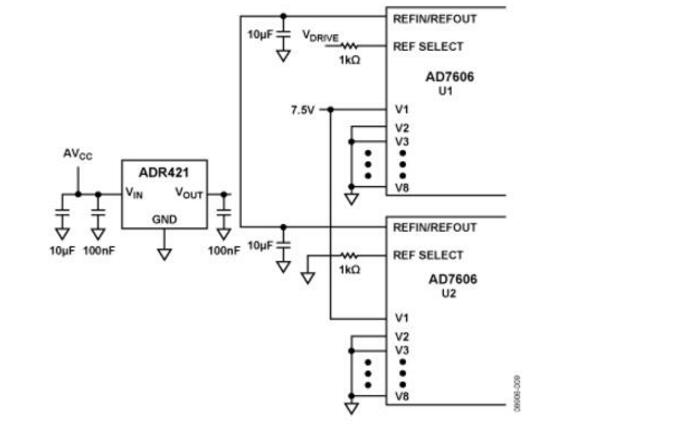

ad7606应用电路三:

7.5 V信号施加于U1的V1和U2的V1,板上的所有16个通道以200 kSPS速率工作,如图9的配置电路示意图所示。

图9. 用于测试两个AD7606之间器件间匹配的电路示意图,U1内部基准电压源用作系统基准电压源

ad7606应用电路四:

AD7606-共需要9个去稠曳容就可以保証其穏定地迸行工作,包括4个屯源引脚 AVcc( 100nf)、REFCAPA( REFCAPB )弓脚和REFIN/REFOUT引脚( 10pF板性曳容)、丙个REGCAP引脚( 1pF )以及還輯屯源引脚Vdrive ( 100nf)。

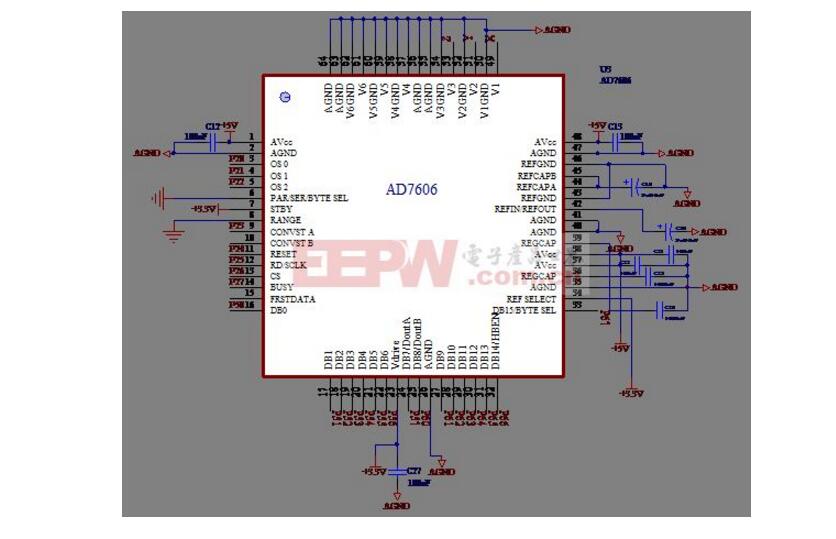

ad7606应用电路五:

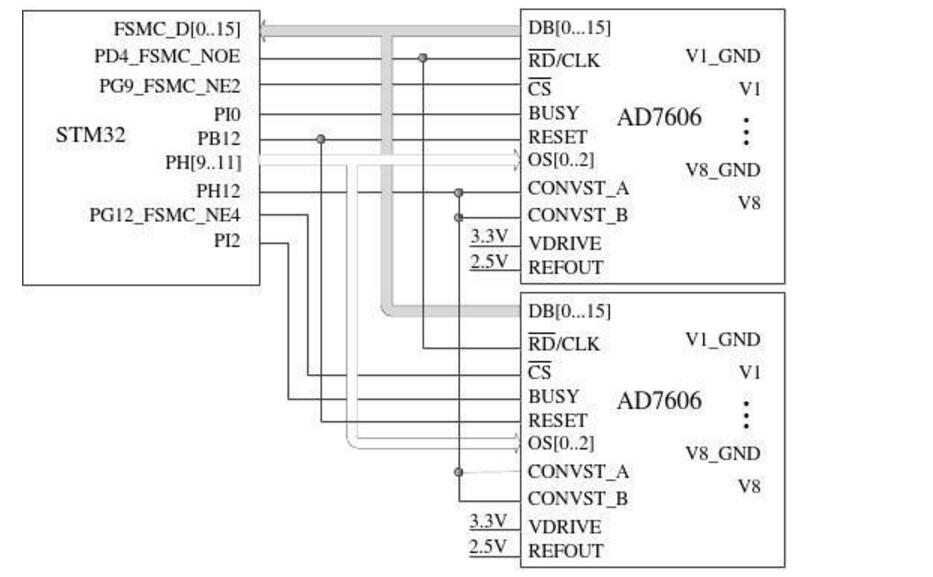

数据采集模块由两片AD7606组成,AD7606与STM32之间的电路连接示意图如图

(1)AD7606提供了三种接口选项:并行接口、高速串行接口和并行字节接口。其中并行接口具有最高的数据传输速度,并且与STM32的FSMC(FlexibleStaticMemoryController,可变静态存储控制器)兼容。因此两片AD7606与STM32通过并行接口方式连接。AD7606的数据线DB0~DB15分别连接对应的FSMC数据线,片选信号分别接到FSMC接口片选信号PG9_FSMC_NE2和PG12_FSMC_NE4上。

(2)AD7606的BUSY引脚电平为高时表示AD正在进行转换,变低表示转换完成。将BUSY引脚接到STM32的外部中断引脚并配置为下降沿触发,这样可以在AF转换完成后及时读取数据。

(3)OS[0..2]为过采样配置引脚,通过控制STM32相关GPIO的电平可以是AD7606工作在不同的过采样状态。

(4)CONVST_A,CONVST_B为转换触发信号,上升沿触发。对于每一个AD7606来说,CONVST_A控制模拟通道1~4,CONVST_B控制模拟通道5~8。由于需要对所有通道同步采样,因此将CONVST_A,CONVST_B引脚同时连接在一个触发信号引脚上以实现同步采样。

(5)REFOUT引脚为外部基准电压输入引脚。AD7606可以配置为使用内部基准电压或外部基准电压。当两片AD7606同时工作时,使用外部基准电压可以保证所有输入通道转换精度的一致性。外部基准电压源选择ADR421,ADR421为2.5V基准电源,具有出色的噪声性能、稳定性和精度【参考】,可以满足AD对基准电压源的精度要求。

- 相关推荐

- 热点推荐

- AD7606

-

AD7606/AD7606 - 6/AD7606 - 4数据采集系统详解2026-03-31 416

-

AD7606/AD7606 - 6/AD7606 - 4:高性能同步采样模数数据采集系统解析2026-03-30 420

-

基于STM32的AD7606的数据采集例程2022-12-07 1965

-

2片AD7606总成的采样电路原理图2022-09-26 1301

-

AD7606应用笔记2021-12-05 1660

-

AD7606 IBIS型号2021-03-24 820

-

AD7606系列软件型号2021-03-22 897

-

AD7606参考代码2021-03-18 1618

-

AD7606 Family Software Model2021-01-29 866

-

ad7606与stm32连接电路介绍2018-05-21 21065

-

ad7606中文资料汇总(ad7606引脚图及功能_内部结构及应用电路)2018-05-16 95291

-

AD7606中文电路描述2016-05-05 1374

-

AD7606中文资料pdf2015-12-11 4186

全部0条评论

快来发表一下你的评论吧 !