铜对芯片制造中的重要作用

描述

文章来源:半导体与物理

原文作者:jjfly686

本文介绍了铜对芯片制造中的重要作用和加工工艺。

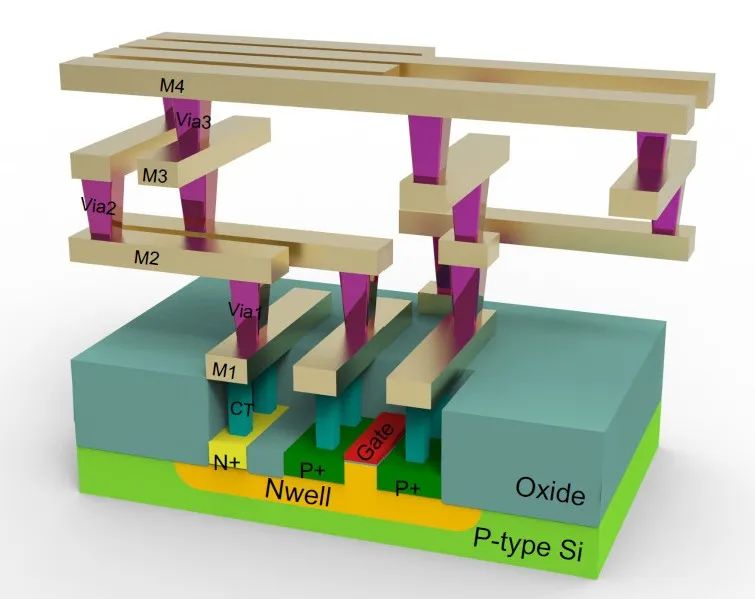

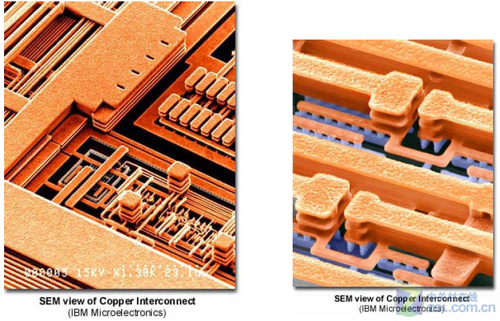

在指甲盖大小的芯片上,数百亿晶体管需要通过比头发丝细千倍的金属线连接。当制程进入130纳米节点时,传统铝互连已无法满足需求——而铜(Cu) 的引入,如同一场纳米级的“金属革命”,让芯片性能与能效实现质的飞跃。

一、为什么是铜?——铝互连的三大困局

1997年IBM首次将铜引入芯片制造前,铝(Al)统治互连领域30年,但纳米时代暴露其致命缺陷:

| 特性 | 铝(Al) | 铜(Cu) | 优势提升 |

|---|---|---|---|

| 电阻率 | 2.65 μΩ·cm | 1.68 μΩ·cm | 降低37% |

| 抗电迁移能力 | 失效电流密度<1 MA/cm² | >5 MA/cm² | 提升5倍 |

| 热膨胀系数 | 23 ppm/℃ | 17 ppm/℃ | 更匹配硅衬底 |

铝的溃败:130 nm节点中,铝线电阻占RC延迟的70%,芯片频率卡在1 GHz;电流密度>10⁶ A/cm²时,铝原子被电子“吹走”,导线断裂。

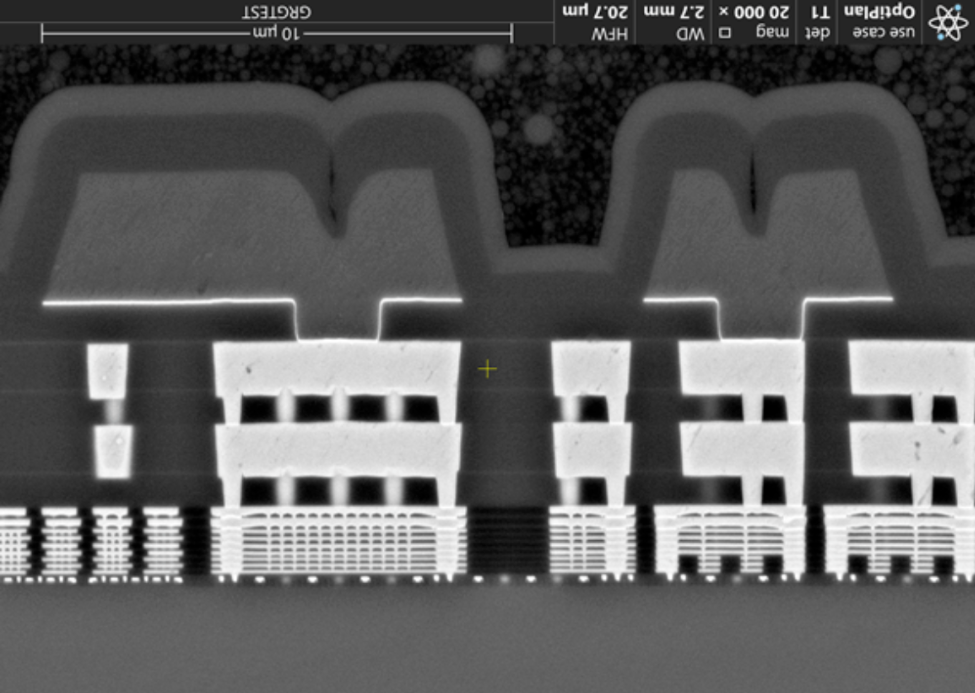

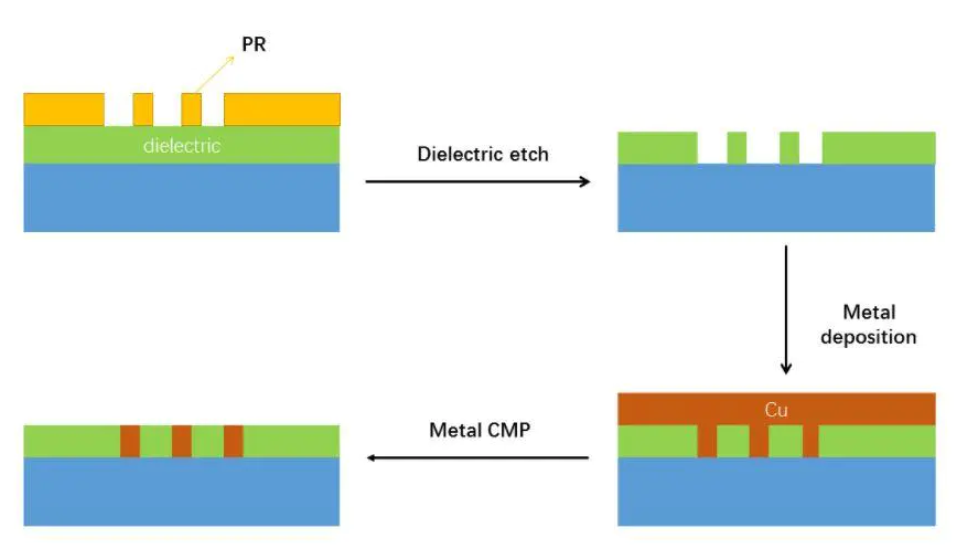

二、铜互连的制造奥秘:双大马士革工艺

铜无法直接刻蚀,工程师发明了双大马士革工艺(Dual Damascene):

工艺流程(以5 nm节点为例):

1. 介质层刻槽:

在Low-k材料上光刻,刻蚀出导线沟槽和通孔);

2. 原子级防护:

沉积2 nm 钽(Ta)阻挡层(防铜扩散);沉积1 nm 钌(Ru)种子层(增强附着力);

3. 超填充电镀:

铜电镀液(CuSO₄ + 添加剂)中通电,实现自底向上填充;

4. 化学机械抛光:

两步抛光:先磨平铜层,再精抛阻挡层,表面起伏<0.3 nm。

三、铜在芯片中的核心作用

1. 全局互连的“电流大动脉”

高层厚铜线(M8-M10层):厚度1-3 μm,传输时钟/电源信号(电流>10 mA);1100℃退火后晶粒>1 μm。

2. 局部互连的“纳米导线”

低层铜线(M1-M3层):线宽10-20 nm,连接相邻晶体管;钴包裹铜技术抑制电迁移。

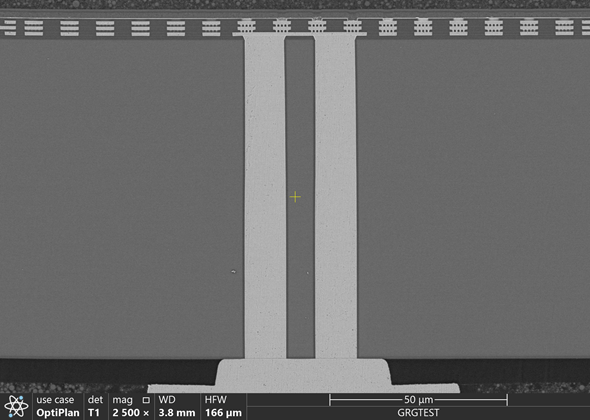

3. 三维堆叠的“垂直电梯”

硅通孔(TSV):直径5 μm深100 μm的铜柱连接上下芯片;热膨胀匹配设计,避免应力开裂。

-

氧化层制备在芯片制造中的重要作用2025-05-27 1196

-

阻性负载的重要作用2025-01-07 5939

-

【案例5】DFM在产品生产制造过程中的重要作用2021-07-09 4925

-

浅谈展会宣传推广的重要作用2021-08-26 1330

-

日志系统在应用中的重要作用2010-01-29 9495

-

通信电源在通信机房中的重要作用2010-11-16 2500

-

边缘计算在企业中占有重要作用2021-02-22 2039

-

电容在开关电源中的重要作用2021-09-29 1585

-

浅析风速传感器在气象监测中的重要作用2021-11-03 1048

-

PCB制造中铜厚度的重要性2023-08-09 1356

-

智能制造中工时分析的重要作用及制造业实现智能制造转型的关键2023-08-15 1520

-

大气环境监测仪在环境保护中的重要作用2024-05-13 1059

-

DCAC电源模块在工业科技中的重要作用2024-07-10 1301

-

激光焊锡中温度控制系统的重要作用2024-12-03 1046

-

氮化钛在芯片制造中的重要作用2025-03-18 2161

全部0条评论

快来发表一下你的评论吧 !