火爆开发中|开源FPGA硬件板卡,硬件第一期发布

描述

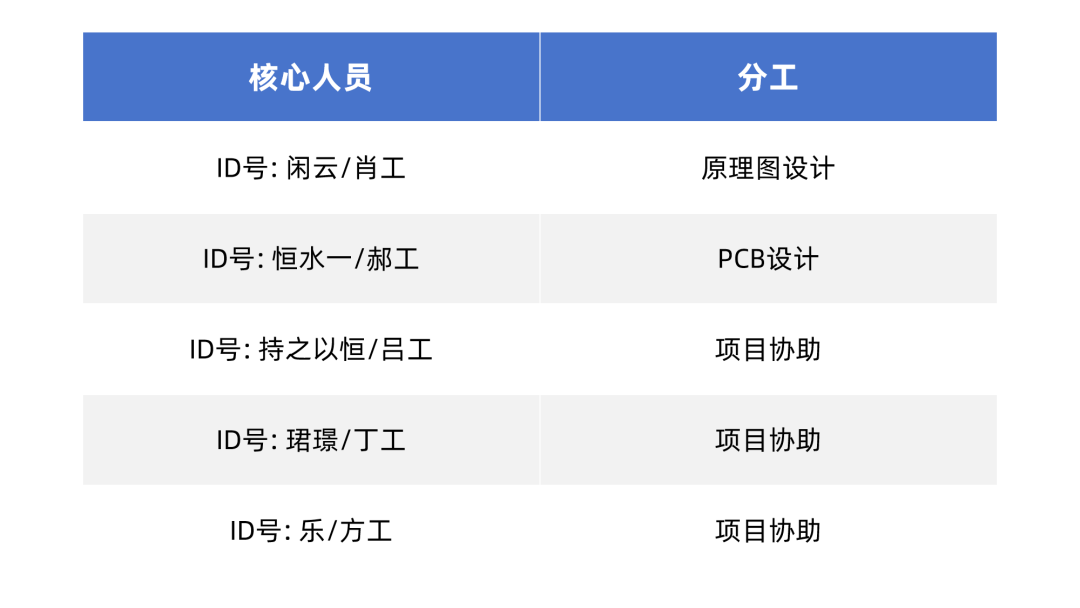

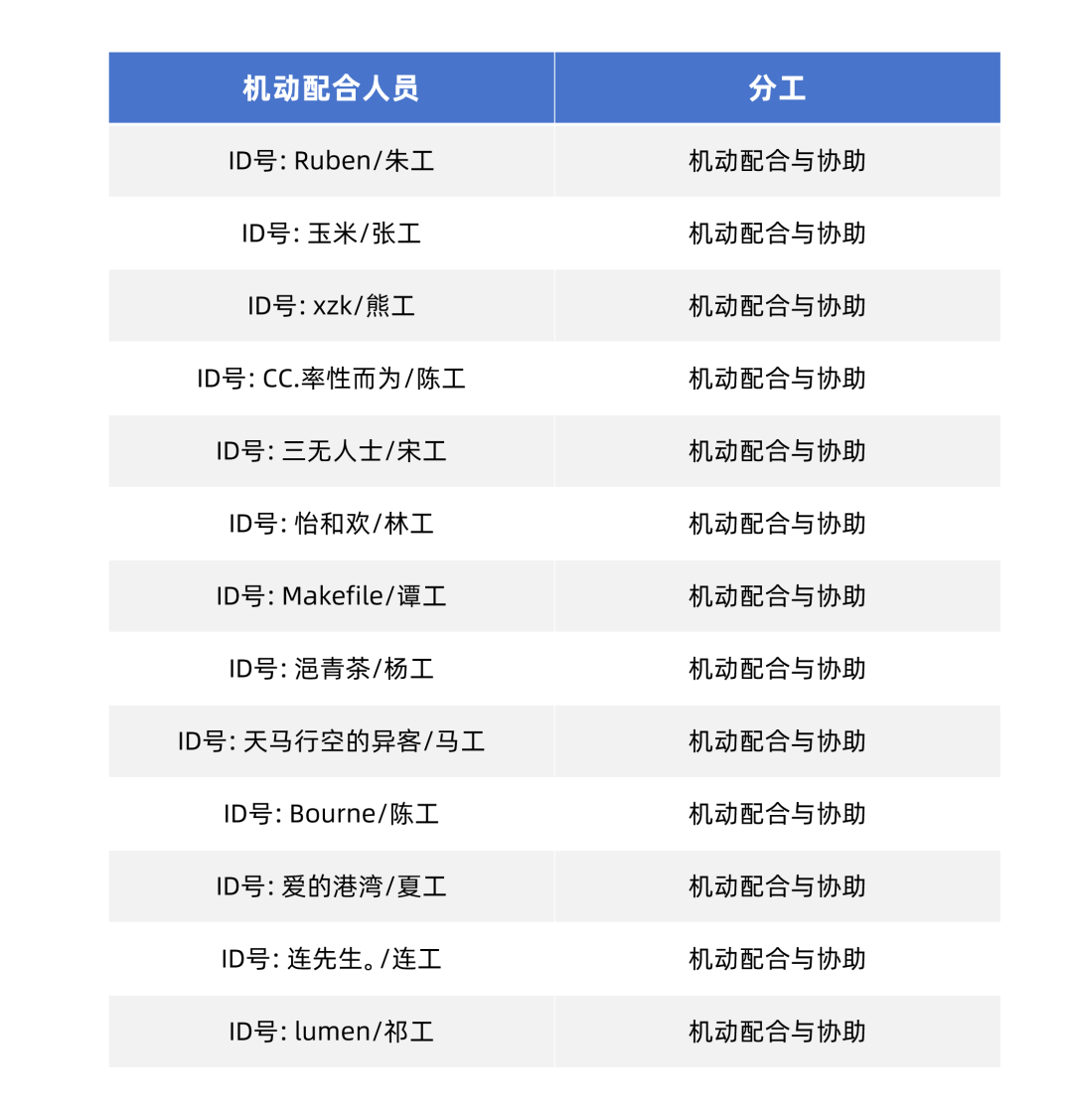

开源FPGA项目自发布以来,得到了众多开发者的关注,涉及工业、通信、车载等多个行业的100+位工程师报名参与设计,并分为:硬件组、FPGA组、linux组。其中硬件组率先开始启动项目,经过和所有报名硬件组的工程师沟通,最终确定由ID号:闲云(肖工)担任原理图主导设计工程师,负责主板硬件设计;ID号:恒水一(郝工)担任Layout主导设计工程师,负责主板Layout设计,其余人员机动配合参与设计,详细分工见下文。

01

最终硬件方案

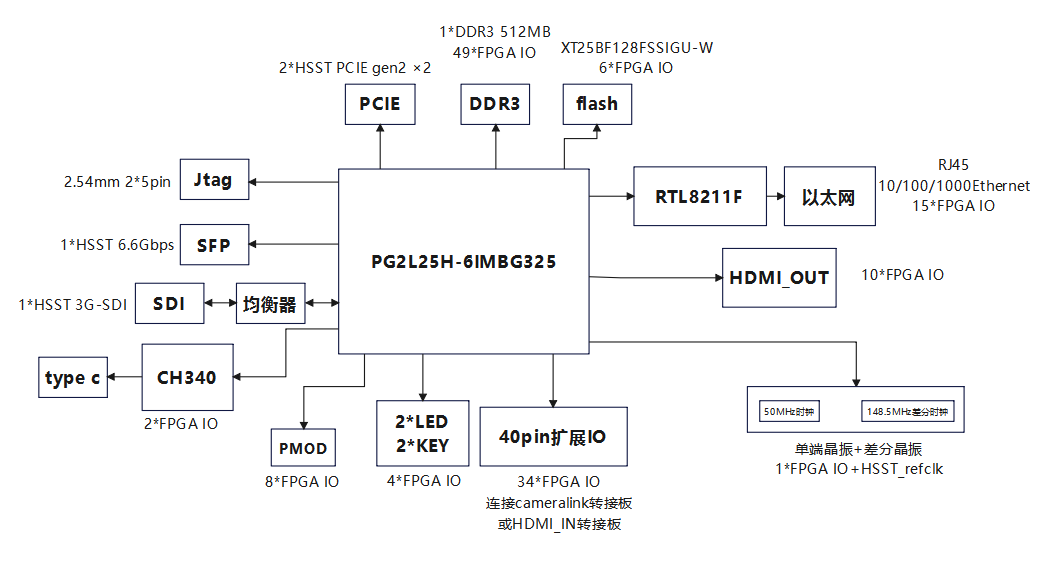

7月6日,相关硬件人员进行了会议讨论,最终确定硬件方案确定如下:

1. 电源:外部电源输入采用电源适配器输入,使用电源芯片为FPGA各电源管脚提供对应的电源,并为外设器件供电,电源方案采用矽力杰SQ20953和SQ28704;

2. 晶振:单端晶振及HSST差分晶振;

3. DDR3:1颗4Gbit(512MB)的DDR3芯片,DDR3型号采用芯存XCCC256M16EP-EINAY;

4. Flash:采用XT25BF128FSSIGU-W用于存储位流文件;

5. HDMI_OUT:FPGA差分管脚连接HDMI输出接口;

6. UART:采用CH340实现USB转uart;

7. SFP光口:1个SFP光纤接口,最高速率支持6.6Gbps

8. PCIE接口:PCIE gen2 x2;

9. 以太网:实现10/100/1000M Ethernet;

10. SDI接口:预留1路SDI接口,SDI均衡器采用LMH0344和LMH0302;

11. JTAG:预留jtag调试接口,标准2.54mm 2*5pin;

12. LED/按键:预留用户按键及用户LED(数量根据可用管脚数量调整);

13. PMOD:预留1路PMOD接口(根据可用管脚数量调整);

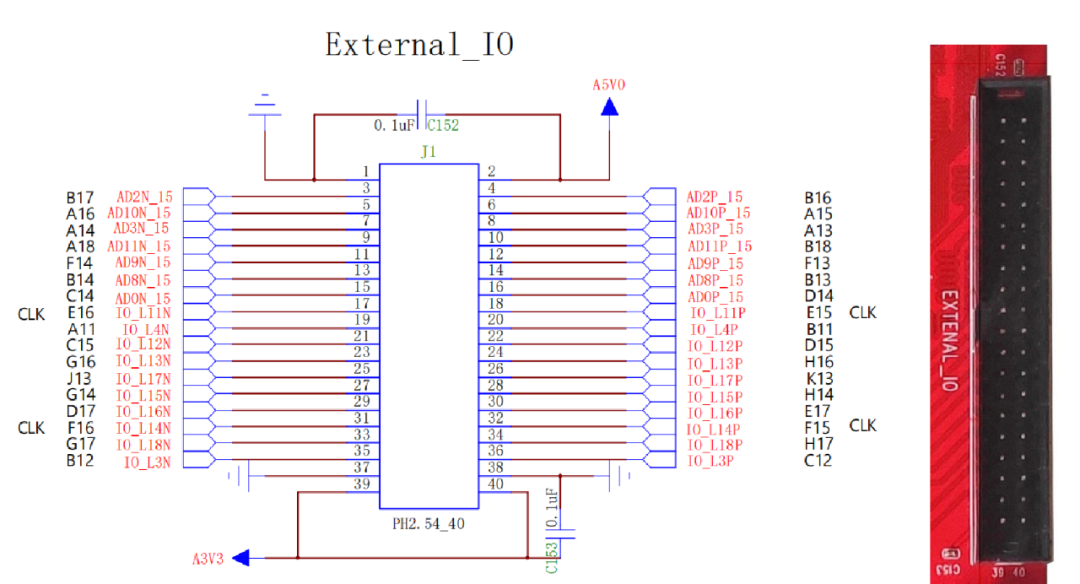

14. 40pin扩展IO接口:扩展1路标准PMOD接口,并设计camera link(base)及HDMI_IN转接板,2.54mm 40pin扩展IO接口线序定义参考如下:

* 注:40pin扩展IO选用FPGA差分IO,且在对应管脚序号支持两对差分始终输入至FPGA的全局时钟管脚,使板卡接口适配更多扩展模块。

PCIe接口形态邀您投票啦!

在开源FPGA开发板的设计中,PCIe 接口形态的选择至关重要,直接影响着开发板的性能、适用场景和使用体验。目前,常见的 PCIe 接口形态主要有金手指和卡槽两种,为了让开发板能更好地满足大家的需求,我们特此发起投票,邀请大家就 “开源开发板 PCIe 接口用金手指好还是卡槽好” 发表自己的看法(欢迎大家积极投票并在评论区留言哦)。

金手指接口,直接集成在 PCB 板上,具有出色的导电性能和抗氧化能力,能保证数据高速稳定传输。板卡结构设计需符合PCIE卡的尺寸要求,若安装不当易导致接口损坏,且作为从设备使用时较为常见,功能升级和维护相对不便。

卡槽接口,通用性和灵活性强,能适配多种板卡,方便进行功能扩展和升级,机械强度高,固定效果好,在一些振动较大的环境中表现更优。但它体积较大,会占用较多空间,同时在板卡的布局上更具有灵活性。

请大家根据自己的使用需求、开发场景以及对两种接口的了解,投出宝贵的一票吧!期待大家的积极参与,让我们能更精准地把握大家的需求,设计出更贴合实际应用的开源开发板!

02

硬件设计核心人员

* 再次感谢大家积极报名参与,感谢大家对本次活动的关注和支持!

项目发起人

05

配套指导教材

由项目发起人Mill(米尔)和紫光同创原厂技术专家共同编写的教材《国产FPGA权威开发指南》作为参考。该书不仅从宏观市场角度分析整个FPGA市场及发展,并从硬件架构原理及软件使用方法多个层面阐述FPGA开发的各个方面,并以紫光同创FPGA的器件特性作为分析案列,深入浅出讲解FPGA技术及原理,并在第八章收录了各个领域FPGA应用方案及具体问题解决方法。全书理论实践相结合,具有极高的理论指导及实战意义,可用于高校理论教学的工具书,亦可用于企业FPGA开发指导。

-

全网征集令:开源开发板命名火热征集中......2025-11-04 1324

-

【开源FPGA硬件】硬件黑客集结:开源FPGA开发板测评活动全网火热招募中......2025-10-29 3503

-

火爆开发中 | 开源FPGA硬件板卡,硬件第一期发布2025-07-09 6044

-

拥抱开源!一起来做FPGA开发板啦!2025-06-06 37696

-

开源芯片社区9月双周报-第一期2023-10-11 2785

-

开发者说 | 地平线程序员奶爸带你玩转机器人开发平台 —— 第一期 手势控制2022-07-19 4057

-

硬件免费教程(第一期)积分运算电路公式推导方法2021-04-01 4027

-

请问你们第一期视频都是怎么学的?2019-09-24 2712

-

请问第一期视频需要掌握什么程度?2019-07-23 1813

-

动手玩转Arduino(第一期)2016-07-08 521

-

FRDM-KL25Z开发第一期(平台介绍、环境搭建、第一个工程)2015-01-30 16394

-

第一期设计坊颁奖啦!获奖的来冒个泡2013-11-12 4212

-

【Verilog基础和编程规范视频公开课】【资料】第一期阿东公开课2013-10-10 49962

-

电子报2011年第一期2011-03-14 4639

全部0条评论

快来发表一下你的评论吧 !