一个高集成度的掉电检测电路应用

电子说

描述

本文导读

相信大家都会遇到这样的情况,当你正在敲一份文档或一段代码时,啪的一下停电啦,我擦……,我的代码……,我的图纸……,我刚写好的文章……。但是在嵌入式系统中也会遇到类似的情况,通常会导致嵌入式系统数据,程序丢失,不能工作,甚至损坏存储系统。而对于核心板的嵌入式系统来说,异常掉电情况下数据不丢失,稳定性是根本。本文基于CAT706介绍一种能够检测到异常掉电,并利用电容中存储的少量电量保存数据、防止存储器损坏、丢失数据的方法。一、概述

首先引用一篇微信文章“老板说:你去跳槽,我去跳楼!一场由SD卡引发的灾难”

去年上半年,我们公司承接了某大型广告公司的电梯广告显示屏的项目,该产品使用了飞思卡尔的IMX6系列芯片作为主控CPU,具备媒体人机触摸互动、媒体投放、远程升级、录像监控等功能。其中很重要的一项功能就是监控和保存功能,因客户的报价较低,我们理所当然的选择了SD卡作为录像数据的保存介质。

没想到,灾难半年后就降临了,半年前发货的10K机器,每个月都有10%的损坏率,损坏的机器90%都是SD卡损坏了!客户不但要求我们赔偿SD卡的损失,延长质保期,而且威胁一个月内不解决将终止合作,客户是老板的唯一大客户,丢失这个客户我们离解散就不远。老板甚至放下狠话:一个月内不解决,你们跳槽,我跳楼。

经过仔细检查确定SD卡损坏的原因是设备上下电导致的。

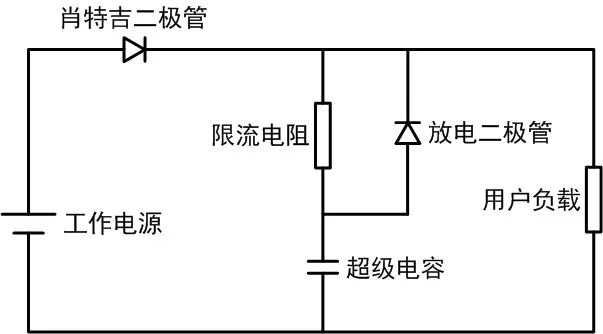

于是我们采用了如下的方案。其中方案的核心是掉电检测电路和超级电容继续供电电路。掉电检测电路是用运放搭出来的一个比较复杂的比较电路,由于复杂这里就不上图了。图1是超级电容的充放电电路,增加该电路可以使掉电后继续维持2秒钟的时间,使CPU完成掉电后的保护处理工作。

图1 超级电容充放电电路

上述案例结局办法是用运放搭建掉电检测电路比较复杂,容易出现问题,这里推荐大家一个高集成度的掉电检测电路。

二、功能简介:

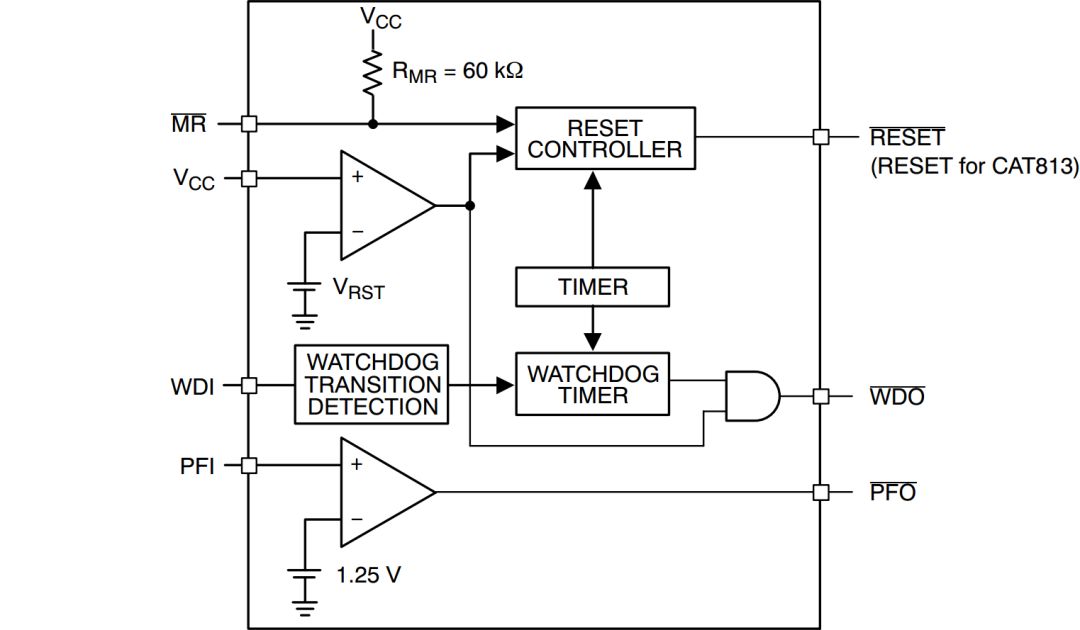

如图2所示是CAT706芯片内部框图。CAT706内部集成了多种功能,功能强大,使用简便,此次只重点讲解其内部的掉电检测功能。

图2 内部功能框图

由于内部框图很简单,可以很容易的分析出有以下四种情况能导致单片机复位或中断:

-

VCC供电不符合要求时可导致RESET复位输出;

-

MR引脚可以手动使RESET复位输出;

-

看门狗WDI没及时喂狗可导致WDO复位输出;

-

电源掉电检测输入PFI可导致PFO中断输出。

针对以上四个功能对嵌入式系统作用如下:

-

可保证VCC供电在稳定时单片机工作,不稳定时复位输出保证系统稳定运行;

-

可人为手动控制单片机复位运行;

-

看门狗实时监测系统,防止系统跑崩溃;

-

及时监测供电系统是否掉电从而让系统迅速处理数据。

本篇文章主要就是针对其第四点检测意外掉电的保护处理方案。

三、典型应用

PFI相当于是一个电压比较器的正输入端,如果PFI电压高于1.25V那么PFO就会输出高电平,如果PFI电压低于1.25V哪呢PFO就会输出低电平。如此便可以通过PFI作为输入将前端的高电压分压后接入,从而可以提前检测到前端的掉电情况。

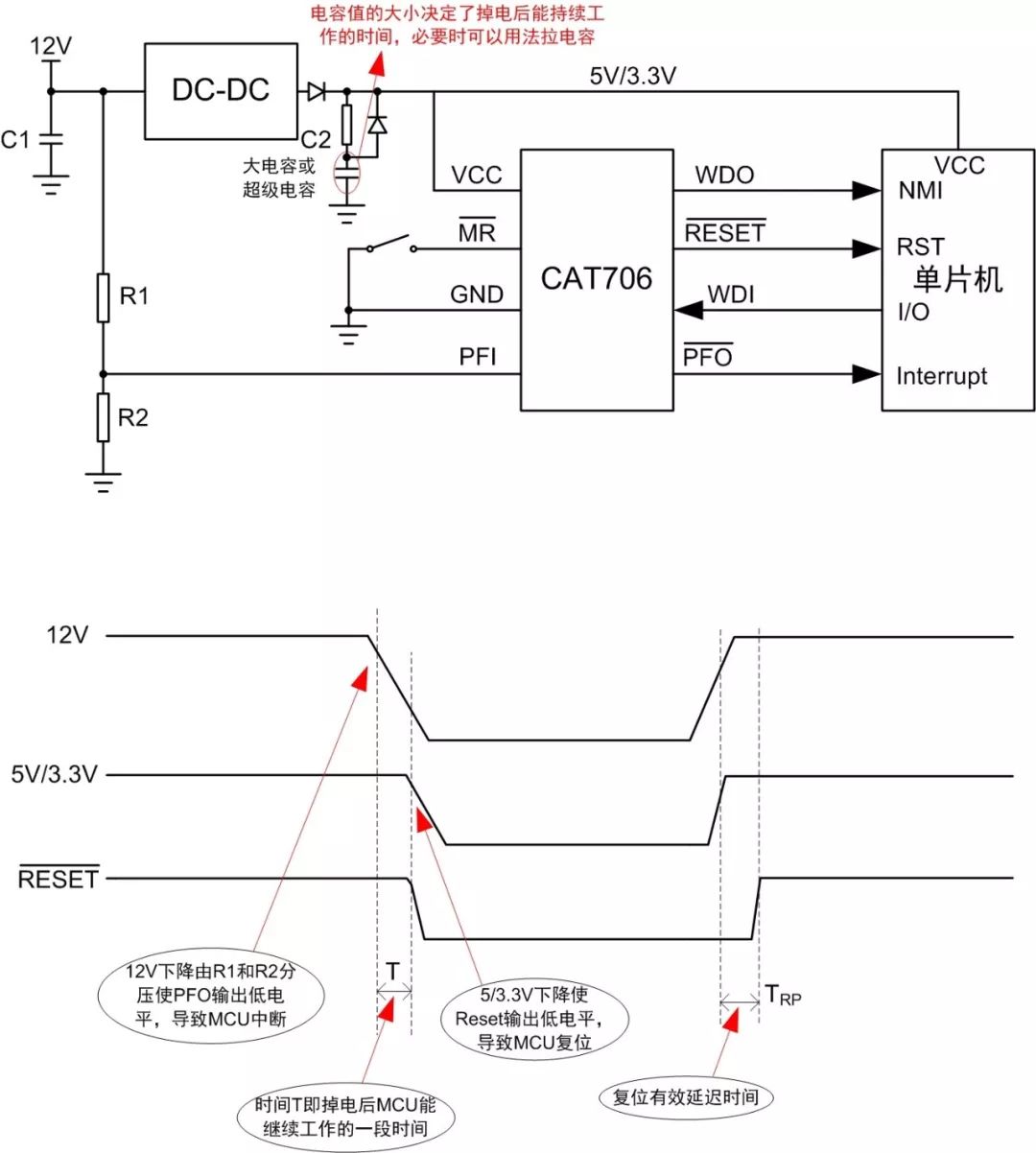

如图3所示是CAT706典型应用电路及时序图。原理图相对比较简单容易理解,并且画出了在掉电和上电后各部分的理论波形图。

一般情况下系统的供电都是由前端市电隔离降压到相对偏高的直流电压(如12V),再降压到系统所需要工作的电压(如5V/3.3V)。如图3所示是针对于检测前端的12V直流电压的掉电检测电路。

图3 典型应用电路及时序图

12V上电时输出的5V会对大电容充电,图中串联了一个电阻用来限流,当掉电时电容的电量会通过旁边的肖特吉二极管直接放电给后端负载使用。

由于12V掉电到5V/3.3V掉电完成之间有一段时差,所以可以提前检测12V的掉电情况使单片机进入Interrupt对掉电采取一系列应对措施,并且在5V/3.3V掉电完成前完成操作,如图中的时间T,并且此段时间T与图中红色圈的电容值大小有关,电容值越大时间T就越长(必要时可以考虑使用法拉电容);且检测掉电的信号越靠近总电源的前端就越好。

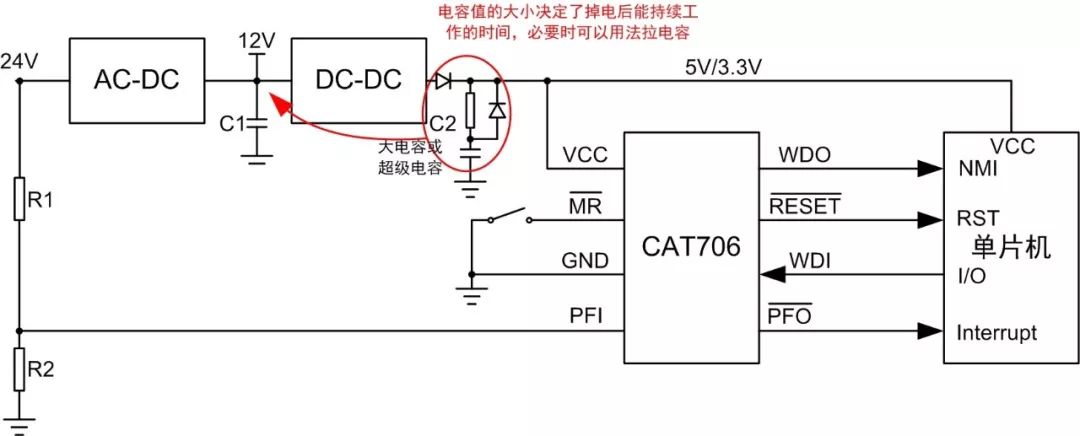

为了增大掉电后的维持时间T,不仅可以增大储能电容值来达到目的,也可以将掉电检测信号往前端挪动,例如将掉电检测移至最前端的220V市电或前端高压,市电掉电时到12V掉电中间也有一段时间,这样就可以间接增加掉电后的维持时间T。

如图4所示是检测前端电压的掉电检测电路。提前处理掉电信号以此来增加掉电后的电压维持时间。

图4 前端掉电检测电路

以图3所示的法拉电容放置位置可知随着掉电后的电压维持,电容上的电压会逐渐下降可能会影响到后端系统的工作。为此可以将大电容的充放电电路移至前端的高电压部分,也可以将降压电路分为两节或三节降压连接,如此只需将大电容的放置位置相对往前端挪一节即可保证在掉电维持的那段时间内主系统的工作电压维持稳定。如图4所示对大电容的摆放位置改动。

四、实测分析

针对上一节关于CAT706原理的推算和实际效果波形的推算我们做了如下的硬件电路搭建,硬件电路针对图3搭建。如图5所示硬件使用洞洞板搭建,用来测试实际的输入供电电压波形,输出电压波形以及PFO和RST引脚的波形。

图5 实物图

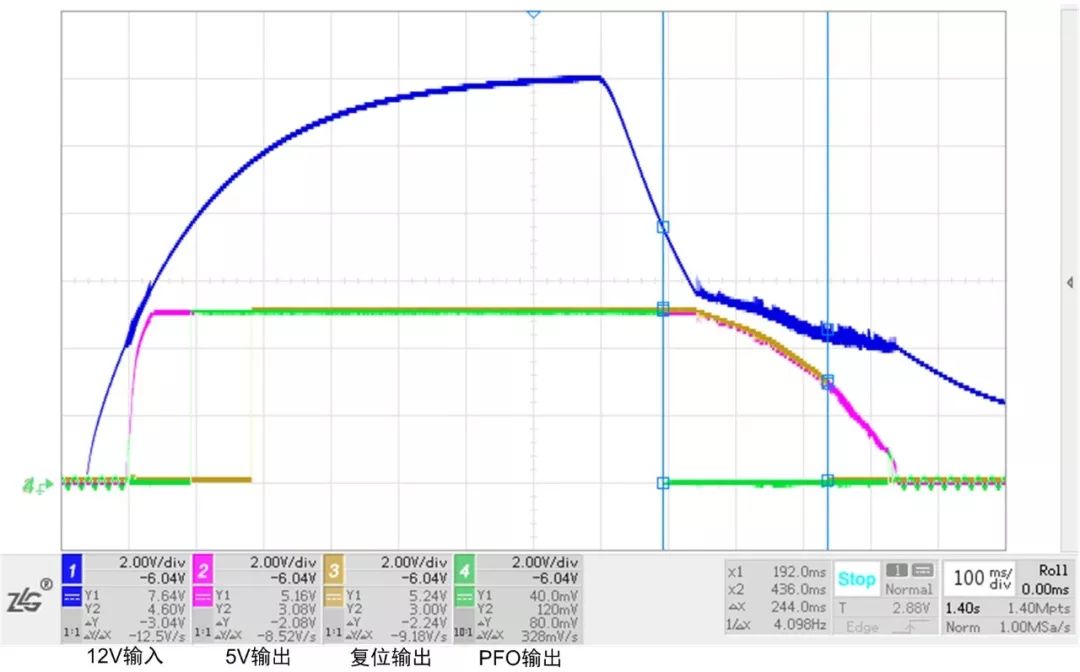

如图6所示波形1是输入的12V电压波形、波形2是输出的5V电压波形、波形3是复位引脚的电压波形、波形4是PFO引脚的电压波形。图中测试时输出以10mA的负载对其恒流放电。

图6 测试波形图

当输入12V上升时,DCDC电源会紧接着开始输出5V,同时随之12V的上升其分压值若大于PFI的输入阈值时PFO会跟着立即输出高电平,复位引脚在检测到5V电压正常一段时间后也会时复位系统,系统启动工作。

当输入12V意外断电下降时其在PFI引脚上的分压值低于阈值时PFO会立即输出低电平,此PFO的低电平会中断系统主控告知系统意外断电应立即对存储数据进行处理,防止数据丢失。图中的测试波形是以10mA的恒流负载模拟测试效果,从图中可以看出从检测到意外断电到系统复位停止工作中间有244ms的处理时间。这个时间和DCDC输出端的电容有很大的关系,电容值越大其数据处理的时间越长,图中是以2200μF的电容值大小、负载10mA恒流情况下测得是时间。实际处理时检测到掉电主控应立即断掉液晶屏等不需要的耗电外设只保持主控部分的供电即可。

-

基于i.MX6ULL的掉电检测设计与软件测试2023-11-09 1517

-

单片机掉电检测与数据掉电保存方案2023-09-18 5572

-

一种机载电源掉电检测电路设计2023-05-25 998

-

常用的电源掉电检测电路介绍2023-02-27 3925

-

XB8886AR系列产品是锂的高集成度解决方案。2022-03-08 1026

-

赛芯锂电保护XB7608AJ反向连接保护高集成度解决方案2021-04-15 1138

-

高集成度RF IC是什么?2019-09-30 3627

-

5V电压掉电检测2019-01-07 8661

-

单片机掉电检测与保存2018-01-14 10824

-

集成度是什么意思_集成度的概念2017-11-10 19998

-

一种实用的掉电检测和保护电路2017-01-22 1654

-

高集成度蓝牙4.0模块2016-06-06 2850

-

关于开关电源的掉电检测电路修改的求助2015-08-10 6107

-

电源掉电检测器电路图2009-04-09 2235

全部0条评论

快来发表一下你的评论吧 !