IMEC上周宣布了一项新的技术,制造了全球最小的SRAM芯片

制造/封装

描述

地球上除了IBM、英特尔、台积电、三星具有强大的半导体工艺研发技术实力之外,比利时微电子中心IMEC也是全球知名的半导体研发中心,国内的14nm FinFET工艺就是跟他们合作的。

在新一代半导体工艺上,除了三星提及5nm及之后3nm工艺之外,其他家都没有具体的5nm、3nm工艺细节披露,IMEC上周则宣布了一项新的技术,制造了全球最小的SRAM芯片,面积缩小了24%,可适用于未来的5nm工艺。

由于结构更简单等原因,每一代新工艺中研发人员往往会使用SRAM芯片做试点,谁造出的SRAM芯片核心面积更小就意味着工艺越先进,此前的记录是三星在今年2月份的国际会议上宣布的6T 256Mb SRAM芯片,面积只有0.026mm2。

不过IMEC上周联合Unisantis公司开发的新一代6T 256Mb SRAM芯片打破了这个记录,核心面积只有0.0184到0.0205mm2,相比三星的SRAM微缩了24%。

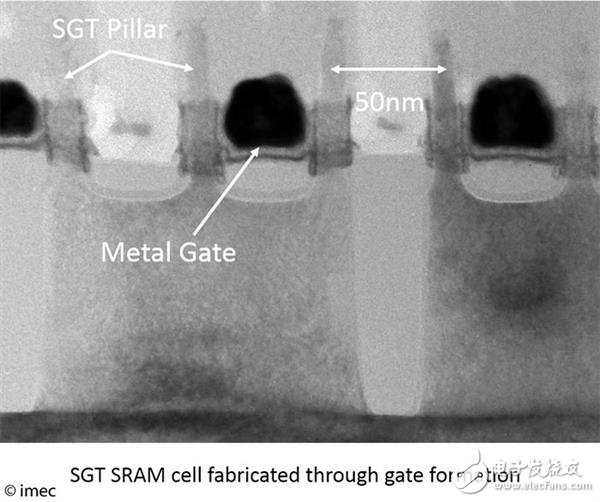

面积能大幅缩小的原因就在于使用了新的晶体管结构,Unisantis与IMEC使用的是前者开发的垂直型环绕栅极(Surrounding Gate Transistor,简称SGT)结构,最小栅极距只有50nm。

研究表明,与水平型GAA晶体管相比,垂直型SGT单元GAA晶体管面积能够缩小20-30%,同时在工作电压、漏电流及稳定性上表现更佳。

目前IMEC正在跟Unisantis公司一起定制新工艺的关键工艺流程及步骤,通过一种新颖的工艺协同优化DTCO技术,研发人员就能使用50nm间距制造出0.0205mm2的SRAM单元,该工艺能够适用于未来的5nm工艺节点。

此外,该工艺还能使用EUV光刻工艺,减少工艺步骤,从而使得设计成本与传统FinFET工艺相当

-

下一代高速芯片晶体管解制造问题解决了!2025-06-20 800

-

可用于各种广泛的数字消费产品的全球最小嵌入式NAND闪存产品2018-09-13 2581

-

关于如何提高SRAM存储器的新方法2020-05-11 2748

-

DARPA为推进制造毫米级到厘米级微型机器人所需的技术制定了一项新计划2018-08-23 1145

-

Arm芯片设计公司发布了一项芯片技术2020-02-12 3180

-

泛林集团发布了一项等离子刻蚀技术及系统解决方案2020-03-10 2988

-

Twitter宣布,它已经实现了一项新的安全功能2020-07-24 2155

-

TCL宣布了一项名为NXTPAPER的新显示技术2020-09-09 4638

-

ASML宣布了一项合作成果:在印刷24nm节距线方面取得突破2021-02-03 2201

-

IBM推出一项微芯片工艺技术中的新改进2021-03-26 2044

-

Molex莫仕发布了一项针对工业4.0制造业的全球调研结果2021-08-02 2246

-

Molex莫仕发布一项针对工业4.0制造业的全球调研结果2022-03-28 1926

-

NVIDIA和谷歌云宣布开展一项新的合作,加速AI开发2024-04-11 1479

-

IMEC组建汽车Chiplet联盟2024-10-15 1272

-

Imec牵头启动汽车芯粒计划2024-10-22 1406

全部0条评论

快来发表一下你的评论吧 !