FPGA学习系列:二选一数据选择器的设计

描述

前两篇给大家介绍了软件的安装、破解以及工程的建立等基本的软件操作,这一篇就通过简单的二选一的数据选择器的设计来实际操作一下,要记住,多动手才是王道。

设计背景:

数据选择器在数字电路的设计中非常重要,在FPGA内部的逻辑实现中都是通过数据选择器实现的,数据选择器的应用使我们的代码和设计更加人性化,多元化。

设计原理:

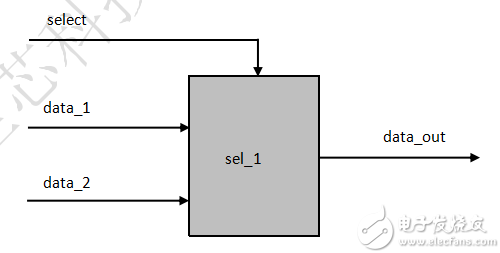

本次的设计主要是一个简单的二选一数据选择器,我们的设计主要有4个端口,数据输入data_1,data_2,数据选择位select,输出data_out

设计架构图:

设计代码:

模块

0 module sel_1(data_1, data_2, select, data_out);

1

2 input data_1, data_2; //数据输入

3 input select; //选择位

4

5 output reg data_out; //数据的输出

6

7 always @ (*)

8 begin

9 if(select) //如果选择位为高,输出data_1

10 data_out = data_1;

11 else //如果选择位为低,输出data_2

12 data_out = data_2;

13 end

14

15 endmodule

测试模块

0 `timescale 1ns / 1ps

1

2 module sel_1_tb;

3

4 reg data_1, data_2; //定义模块的输入输出

5 reg select;

6

7 wire data_out;

8

9 initial begin

10 data_1 = 0;

11 data_2 = 0;

12 select = 0;

13

14 #200 data_1 = 1; data_2 = 0; //延迟200ns给输入赋值

15 #100 select = 1; //延迟200ns后给选择位赋值

16 #100 select = 0; //延迟200ns后给选择位赋值

17

18 #200 data_1 = 0; data_2 = 1;

19 #100 select = 0;

20 #100 select = 1;

21

22 #300 $stop;

23 end

24

25 sel_1 sel_1_dut( //模块的例化,和端口的连接

26 .data_1(data_1),

27 .data_2(data_2),

28 .select(select),

29 .data_out(data_out)

30 );

31

32 endmodule

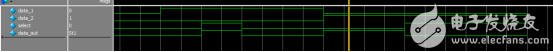

仿真图:

在仿真中我们可以真实的看到,当数据data_1为1,data_2位0的时候,当选择位select为0的时候,输出data_out的值为0也就是data_2的值,当select为1的时候,data_out的值位1,也就是data_1的值,后面的仿真也一样我们可以清楚的看到。

以上就是二选一数据选择器的设计,大家可以自己动手在quartus II 13.1 去操作一下,体验一下。

-

基于FPGA的多路选择器设计(附代码)2023-03-01 2101

-

4选1多路选择器是什么?2022-02-09 1023

-

EDA四选一多路选择器的设计2021-04-12 6785

-

【梦翼师兄今日分享】 二选一数据选择器的设计2019-12-13 4943

-

二选一数据选择器的系统设计框架图分析2019-11-20 13898

-

请问有单个二选一数据选择器的芯片吗?2019-06-20 9098

-

74LS153利用双四选一数据选择器实现全加器的电路图资料免费下载2018-11-26 89603

-

FPGA学习系列:33. 设计一个简单的二选一数据选择器2018-09-21 11859

-

设计一个1位的二选一多路选择器及其VHDL描述2018-04-27 33043

-

找一种八选一数据选择器贴片式芯片2017-12-01 6850

-

FPGA_100天之旅_第三天,二选一数据选择器2017-08-04 4704

-

至芯科技之altera 系列FPGA教程 第九篇 二选一多路选择器的设计2016-08-11 3472

-

数据选择器2014-05-30 3906

全部0条评论

快来发表一下你的评论吧 !