PCIe物理层实现了一对收发差分对,可以实现全双工的通信方式

电子说

描述

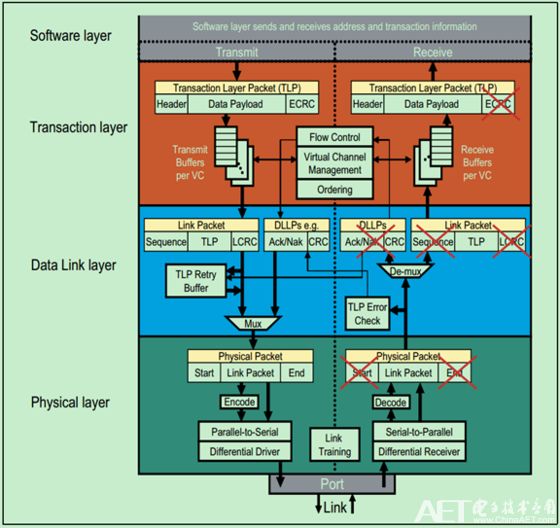

首先,回顾一下,之前看了很多遍的PCIe的Layer结构图:

PCIe中的物理层主要完成编解码(8b/10b for Gen1&Gen2,128b/130b for Gen3 and later)、扰码与解扰码、串并转换、差分发送与接收、链路训练等功能。其中链路训练主要通过物理层包Ordered Sets来实现。

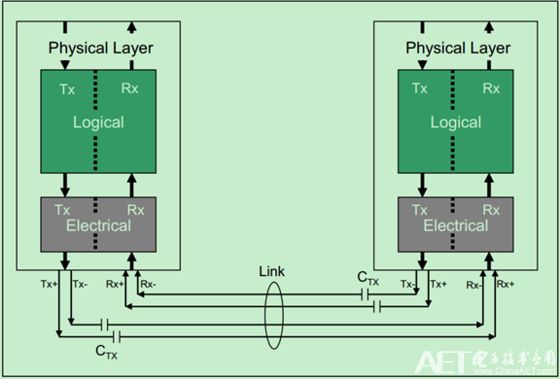

PCIe Spec将物理层分为两个部分——逻辑子层和电气子层,如下图所示:

如上图所示,PCIe物理层实现了一对收发差分对,因此可以实现全双工的通信方式。需要注意的是,PCIe Spec只是规定了物理层需要实现的功能、性能与参数等,置于如何实现这些却并没有明确的说明。也就是说,厂商可以根据自己的需要和实际情况,来设计PCIe的物理层。下面将以Mindshare书中的例子来简要的介绍PCIe的物理层逻辑部分,可能会与其他的厂商的设备的物理层实现方式有所差异,但是设计的目标和最终的功能是基本一致的。

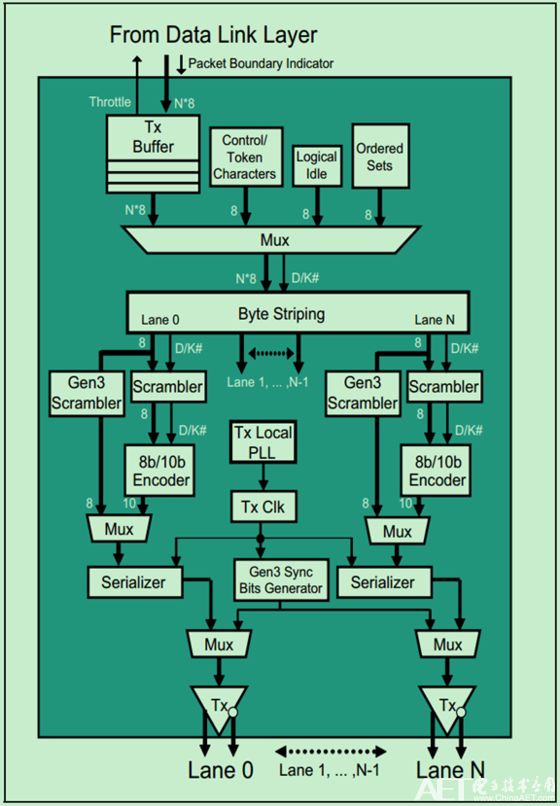

物理层逻辑子层的发送端部分的结构图如下图所示:

在进行8b/10b编码之前,Mux会对来自数据链路层的数据中插入一些内容,如用于标记包边界或者Ordered Sets的控制字符和数据字符。为了区分这些字符,Mux为其对应上一个D/K#位(Data or Kontrol)。

注:图中还包含了Gen3的一些实现,不过这里只介绍Gen1 & Gen2,并不会介绍Gen3。如果大家感兴趣的,可以去阅读Mindshare的书籍或者参考PCIe Gen3的Spec。

Byte Striping将来自Mux的并行数据按照一定的规则(后面会详细地说)分配到各个Lane上去。随后进行扰码(Scrambler)、8b/10b编码、串行化(Serializer),然后是差分发送对。

其中扰码器(Scrambler)是基于伪随机码(Pesudo-Random)的异或逻辑(XOR),由于是伪随机码,所以只要发送端和接收端采用相同的算法和种子,接收端便可以轻松地恢复出数据。但是,如果发送端和接收端由于某些原因导致其节拍不一致了,此时便会产生错误,因此Gen1和Gen2的扰码器(Scrambler)会周期性地被复位。

注:关于8b/10b的原理和作用,在我之前的博文中有所介绍。所以接下来的文章中不会重复介绍这些内容,但是会简要地介绍PCIe中的8b/10b的实现细节和要点。

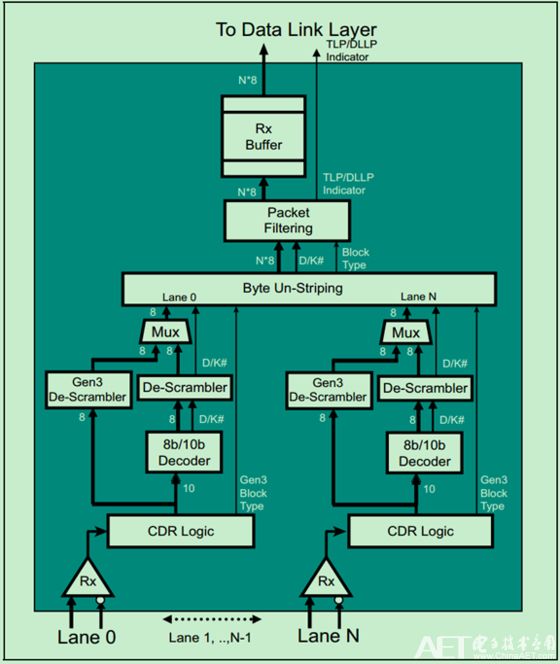

物理层逻辑子层的接收端部分的结构图如下图所示:

由于PCIe采用的是一种Embeded Clock(借助8b/10b)机制,因此接收端在接收到数据流时,首先要从中恢复出时钟信号,这正是通过CDR逻辑来实现的。如上图所示,接收端的逻辑基本上都是与发送端相对应的相反的操作。这里就不在详细地介绍了。

-

HAL库的串口收发函数,HAL的串口DMA方式下不能实现独立的全双工通信吗?2024-05-14 712

-

高速全双工通信:数据世界的“双向快车道”2026-03-17 657

-

PCIe一般介绍2019-06-03 2893

-

全双工无线系统的实现2019-07-11 2062

-

通信基础知识:单工,半双工,全双工2019-09-30 3736

-

如何对PCIe 3.0接收机物理层进行测试?2021-05-11 3414

-

串口通信的物理层与协议层的相关资料推荐2022-02-17 969

-

用于RS485全双工的LPUART,以半双工方式连接时出现回声怎么解决?2023-04-06 819

-

WiMAX物理层技术特征及其OFDM和OFDMA技术的应用2017-12-13 3481

-

PCIe物理层的基本概念2018-05-02 11561

-

PCIe物理层接口定义了物理层中的,媒介层和物理编码子层之间的统一接口2018-09-07 9942

-

SWIPT MIMO全双工系统中的物理层通信优化综述2021-06-02 889

-

ZLG致远电子新一代车载以太网全双工物理层转换器发布2023-06-27 1569

-

SATA主机协议的物理层的实现过程2024-10-22 2127

-

RapidIO标准的串行物理层实现2025-12-09 734

全部0条评论

快来发表一下你的评论吧 !