MCU工程师须知的FPGA硬件属性

电子说

描述

MCU工程师须知的FPGA硬件属性

简单的FPGA构造

在集成电路领域人们经常会听到构造(fabric)这个术语,它指的是FPGA器件的底层基础结构。(作为一个兴趣点,单词“构造”来自中世纪英语fabryke,意思是“建造的某些东西”)。下面让我们从FPGA中的内核可编程构造开始吧……

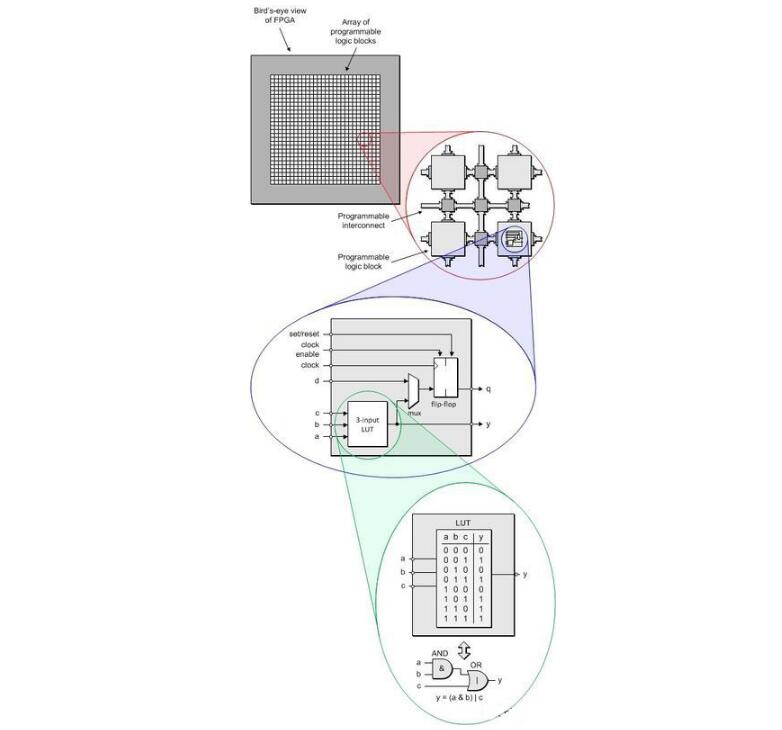

如果我们仔细观察FPGA封装的内部,我们将看到硅片(技术术语裸片)。可编程构造表现为可编程逻辑块阵列,如下图所示。如果我们用放大镜“放大查看”,我们可以看到这种构造由沉浸于可编程互连“海洋”中的许多逻辑“岛”(可编程逻辑块)组成。

图1:简单的FPGA构造

基本FPGA可编程构造的一般性表示。是啊,我确实是用自己的双手亲自创作的这幅图片,我因此感到非常自豪呢,非常感谢你加以关注。如果我们进一步放大,我们可以看到,每个可编程模块都包含有许多数字功能。在这个例子中,我们可以见到一个三输入的查找表(LUT)、一个复用器和一个触发器,但重要的是我们要认识到,这些功能的数量和类型对不同系列的FPGA来说是会变化的。

触发器可以被配置(编程)为寄存器或锁存器;复用器可以被配置为选择一个到逻辑块的输入或LUT的输出;LUT可以被配置为代表任何所要求的逻辑功能。

更详细地了解LUT:

上面所示的简单例子包含一个三输入的查找表(LUT)。在实际应用中,即使最简单的FPGA都会使用四输入LUT,而一些更大更复杂的器件甚至会宣称使用六、七或八输入的LUT,但为了简单起见,我们还是讨论三输入版本。

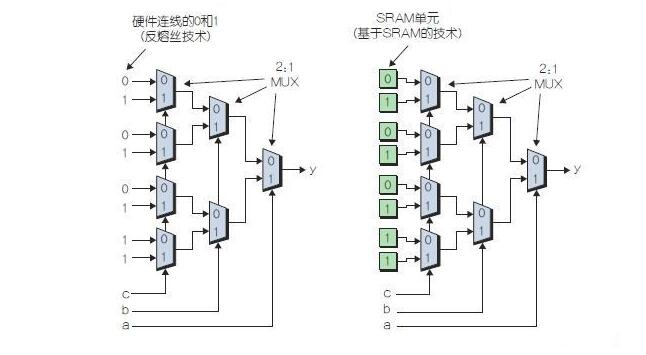

我们会在以后的文章中讨论各种类型的FPGA实现技术。现在我们只需要知道,FPGA内部的可编程单元可以用反熔丝、闪存单元或SRAM内存单元来实现。先让我们看一个用反熔丝技术创建的FPGA吧。这是一种一次性可编程(OTP)技术,这意味着一旦你编程了这个FPGA,它将永远保持这个状态而不再改变。

形象化介绍这种技术的最简单方法是用下图所示级联的2:1复用器(MUX)。对基于反熔丝技术的FPGA来说,编程器件相当于通过“硬件连线”将第一组复用器的输入连接到实现目标逻辑功能所需的正确0或1值。下图中所示的值反映的实际结果是,我们使用这个LUT实现了前面那张图隐含的公式y=(a & b)|c。在实际应用中,复用器可以用场效应管的分支“树”来实现,但我们在这里真的不用担心最底层的实现细节。

图2:输入值经“硬件连接的”反熔丝型LUT(左),输入从SRAM单元馈入的SRAM型LUT(右)

另外一种非常常见的FPGA实现技术是使用SRAM配置单元。同样,我们会在以后的文章中讨论更多的细节。这里我们所要知道的仅是当电路板第一次上电时,基于SRAM的FPGA会加载配置信息(我们可以把这个过程想像为器件的编程)。作为这种配置的一部分,用作LUT复用器输入的SRAM单元会被加载进上图所示的目标0或1值。

我没有显示0和1被加载进SRAM单元的那种机制,因为我不想让问题变得复杂。出于这次讨论的目的,我们真的无需担心这种“魔术”是如何发生的。我在这里唯一要提的事(给你考虑的空间)是—使用一种被称为部分再配置的技术—FPGA的一部分可以发起对另一部分进行再配置(当然反过来也行)。对于具有微控制器和/或软件背景的读者来说,我们可以将这种技术想象为相当于自我修改代码的硬件。这意味着这种技术是非常非常强大的,但也会带来很难隔离和调试的问题。

通用的输入和输出

FPGA器件还包含有通用的输入/输出(GPIO)引脚和焊盘(图1中没有显示)。通过配置单元,FPGA器件内的互连部分可以被编程为这样:将器件的主输入连接到一个或多个可编程逻辑块的输入。任何逻辑块的输出也可以用来驱动任何其它逻辑块的输入和/或FPGA器件的主输出。另外,GPIO引脚可以被配置为支持种类广泛的I/O标准,包括电压、终端阻抗、摆率等。

世界上第一块FPGA与本文中讨论的架构非常类似。这块FPGA就是赛灵思公司在1985年推出的XC2064(是用2um工艺节点制造的),它包含有8×8=64的逻辑块阵列,每个逻辑块包含一个四输入LUT和其它一些简单功能。从那以后,FPGA发展势不可挡,正像我们看到的那样……

复杂的FPGA架构

正如我们在前面说的那样,赛灵思公司在1985年推出的第一块FPGA—XC2064包含8×8=64的逻辑块阵列,每个逻辑块包含一个四输入查找表及其它一些简单功能。由于它们的容量非常有限,因此早期的FPGA只用来执行一些相对简单的任务,比如集中一些胶合逻辑,或实现基本的状态机。然而随着时间的推移,事情开始改变……

随着时间的推移和工艺节点的进步,FPGA的容量和性能不断得到提高,功耗却不断的下降。直到大约2006年以前广泛使用的一直是四输入查找表。事实上,在写这篇文章之时,较小的FPGA系列器件仍在使用四输入的查找表,但一些高端器件可能使用六、七或八输入的查找表。这些大家伙可能被用作一个大的查找表,或分裂成许多更小的功能,比如两个四输入的查找表或一个三输入一个五输入的查找表。在实际的高端器件中,这种可编程构造可以描述相当于百万级(有时甚至千万级)的原始逻辑门。

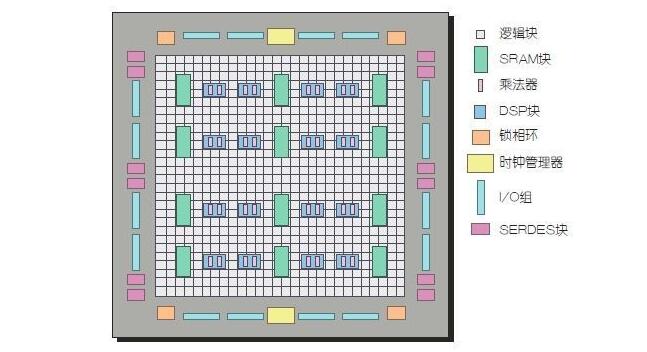

如果某个逻辑功能(比方说计数器)是用FPGA的可编程构造实现的,那么这个功能可以被说成“软功能”。相比之下,如果某个功能是直接用芯片实现的,则被说成“硬功能”。(随着这些功能变得越来越大越来越复杂,我们一般称它们为内核)。软内核的优势在于,你可以让它们做你想让它们做的任何事。硬内核的优势是它们占用较少的硅片面积,具有较高的性能,并且功耗较低。最优的解决方案是混合使用软内核(用可编程构造实现)和硬内核(直接用硅片实现)。这样,除了基于查找表的可编程构造外,今天的FPGA可以利用以下介绍的各种硬内核进行性能增强:

图3:更复杂的FPGA架构

举例来说,该器件可能包含数千个加法器、乘法器和数字信号处理(DSP)功能;数兆位的片上内存,大量的高速串行互连(SERDES)收发器模块,以及众多的其它功能。

带嵌入式处理器的FPGA

这是真正让人兴奋的事情……你可以用FPGA中的普通可编程构造做的事情之一是,使用其中的一部分实现一个或多个软处理器内核。当然,你可以实现不同规模的处理器。举例来说,你可以创建一个或多个8位的处理器,加上一个或多个16位或32位的软处理器—所有处理器都在同一器件中。

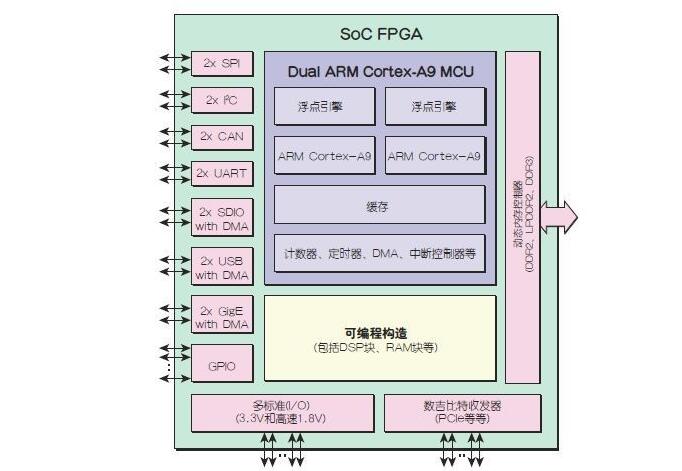

如果FPGA供应商希望提供一个占用较少硅片面积、消耗较低功率但性能更高的处理器,解决方案是将它实现为硬内核。一个非常令人兴奋的开发成果是Altera和赛灵思等公司最近推出的SoC FPGA。考虑下面所示这个例子:

图4:一种新的SoC FPGA

这个漂亮的小东西整合了一个完全以硬内核方式实现的双路ARM Cortex-A9微控制器子系统(运行时钟高达1GHz,包含浮点引擎,片上缓存,计数器,定时器等),以及种类广泛的硬内核接口功能(SPI,I2C,CAN等),还有一个硬内核的动态内存控制器,所有这些组件都利用大量传统的可编程构造和大量的通用输入输出(GPIO)引脚进行了性能增强。(即将在16nm节点推出的一款SoC FPGA据称包含四内核的64位ARM Cortex-A53处理器,双内核32位ARM Cortex-R5实时处理器,以及一个ARM Mali-400MP图形处理器。这些可不是你祖母时候的FPGA哦!)

传统的嵌入式系统架构师可能将其中一个器件放置在电路板上,并将它用作传统的高性能双内核ARM Cortex-A9微控制器。当电路板上电时,硬微控制器内核立即启动,并在任何可编程构造完成配置之前就可用了。这样可以节省时间和精力,并让软件开发人员和硬件设计师同时开始开发。

一种情形是软件开发人员捕获他们的代码,在SoC FPGA的Cortex-A9处理器上运行这些代码,然后通过分析识别任何可能严重影响性能并成为瓶颈的功能。这些功能随后可能就转交给硬件设计工程师用可编程构造来实现,它们(这些功能,不是设计工程师)将使用较低的时钟频率提供明显更高的性能,而且功耗更低。

前面我们说过,硬内核实现的功能(图4所示的ARM Cortex-A9就是一种硬内核)与等效的软内核相比具有更高的性能和更低的功耗。但现在我们又说如果在硬内核处理器上运行的软件功能是个瓶颈,我们可以用可编程构造来实现,这样它就能……你理解的没错,提供更高的性能和更低的功耗。

FPGA开发流程

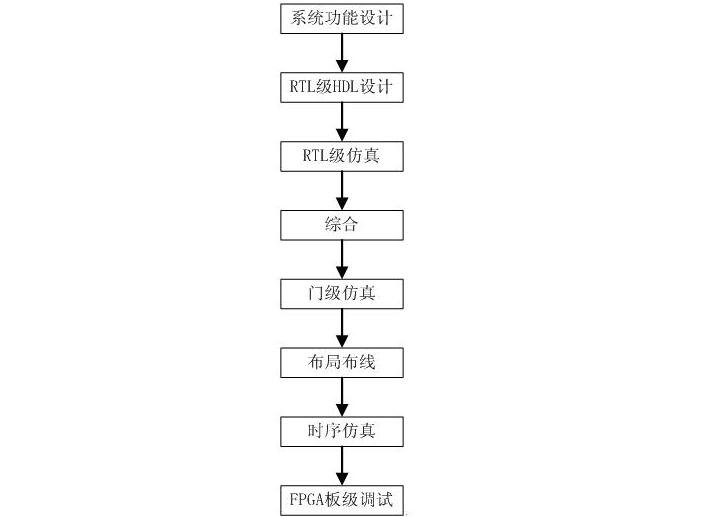

原理图和HDL(Hardwaredescriptionlanguage,硬件描述语言)是两种最常用的数字硬件电路描述方法,其中HDL设计法具有更好的可移植性、通用性和模块划分与重用性的特点,在目前的工程设计中被广泛使用,下面对FPGA设计熟悉电路时的开发流程是基于HDL的。

图6FPGA的开发流程

1)系统功能设计

在系统设计之前,首先要进行的是方案论证、系统设计和FPGA芯片选择等准备工作。系统工程师根据任务要求,如系统的指标和复杂度,对工作速度和芯片本身的各种资源、成本等方面进行权衡,选择合理的设计方案和合适的器件类型。一般都采用自顶向下的设计方法,把系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接使用EDA元件库为止。

2)RTL级HDL设计

RTL级(RegisterTransferLevel,寄存器传输级)指不关注寄存器和组合逻辑的细节(如使用了多少个逻辑门、逻辑门的连接拓扑结构等),通过描述数据在寄存器之间的流动和如何处理、控制这些数据流动的模型的HDL设计方法。RTL级比门级更抽象,同时也更简单和高效。RTL级的最大特点是可以直接用综合工具将其综合成为门级网表,其中RTL级设计直接决定着系统的功能和效率。

3)RTL级仿真

也称为功能(行为)仿真,或是综合前仿真,是在编译之前对用户所设计的电路进行逻辑功能验证,此时的仿真没有延迟信息,仅对初步的功能进行检测。仿真前,要先利用波形编辑器和HDL等建立波形文件和测试向量(即将所关心的输入信号组合成序列),仿真结果将会生成报告文件和输出信号波形,从中便可以观察各个节点信号的变化。如果发现错误,则返回设计修改逻辑设计。常用的工具有ModelTech公司的ModelSim、Sysnopsys公司的VCS和Cadence公司的NC-Verilog以及NC-VHDL等软件。虽然功能仿真不是FPGA开发过程中的必需步骤,但却是系统设计中最关键的一步。

为了提高功能仿真的效率,需要建立测试平台testbench,其测试激励一般使用行为级HDL语言描述,其中RTL级模块是可综合的,它是行为级模块的一个子集合。

4)综合

所谓综合就是将较高级抽象层次的描述转化成较低层次的描述。综合优化根据目标与要求优化所生成的逻辑连接,使层次设计平面化,供FPGA布局布线软件进行实现。就目前的层次来看,综合优化(Synthesis)是指将设计输入编译成由与门、或门、非门、RAM、触发器等基本逻辑单元组成的逻辑连接网表,而并非真实的门级电路。真实具体的门级电路需要利用FPGA制造商的布局布线功能,根据综合后生成的标准门级结构网表来产生。为了能转换成标准的门级结构网表,HDL程序的编写必须符合特定综合器所要求的风格。由于门级结构、RTL级的HDL程序的综合是很成熟的技术,所有的综合器都可以支持到这一级别的综合。常用的综合工具有Synplicity公司的Synplify/SynplifyPro软件以及各个FPGA厂家自己推出的综合开发工具。

5)门级仿真

也称为综合后仿真,综合后仿真检查综合结果是否和原设计一致。在仿真时,把综合生成的标准延时文件反标注到综合仿真模型中去,可估计门延时带来的影响。但这一步骤不能估计线延时,因此和布线后的实际情况还有一定的差距,并不十分准确。目前的综合工具较为成熟,对于一般的设计可以省略这一步,但如果在布局布线后发现电路结构和设计意图不符,则需要回溯到综合后仿真来确认问题之所在。在功能仿真中介绍的软件工具一般都支持综合后仿真。

6)布局布线

实现是将综合生成的逻辑网表配置到具体的FPGA芯片上,将工程的逻辑和时序与器件的可用资源匹配。布局布线是其中最重要的过程,布局将逻辑网表中的硬件原语和底层单元合理地配置到芯片内部的固有硬件结构上,并且往往需要在速度最优和面积最优之间作出选择。布线根据布局的拓扑结构,利用芯片内部的各种连线资源,合理正确地连接各个元件。也可以简单地将布局布线理解为对FPGA内部查找表和寄存器资源的合理配置,布局可以被理解挑选可实现设计网表的最优的资源组合,而布线就是将这些查找表和寄存器资源以最优方式连接起来。

目前,FPGA的结构非常复杂,特别是在有时序约束条件时,需要利用时序驱动的引擎进行布局布线。布线结束后,软件工具会自动生成报告,提供有关设计中各部分资源的使用情况。由于只有FPGA芯片生产商对芯片结构最为了解,所以布局布线必须选择芯片开发商提供的工具。

7)时序仿真

是指将布局布线的延时信息反标注到设计网表中来检测有无时序违规(即不满足时序约束条件或器件固有的时序规则,如建立时间、保持时间等)现象。时序仿真包含的延迟信息最全,也最精确,能较好地反映芯片的实际工作情况。由于不同芯片的内部延时不一样,不同的布局布线方案也给延时带来不同的影响。因此在布局布线后,通过对系统和各个模块进行时序仿真,分析其时序关系,估计系统性能,以及检查和消除竞争冒险是非常有必要的。

8)FPGA板级调试

通过编程器将布局布线后的配置文件下载至FPGA中,对其硬件进行编程。配置文件一般为.pof或.sof文件格式,下载的方式包括AS(主动)、PS(被动)、JTAG(边界扫描)等方式。

逻辑分析仪(LogicAnalyzer,LA)是FPGA设计的主要调试工具,但需要引出大量的测试管脚,且LA价格昂贵。目前,主流的FPGA芯片生产商都提供了内嵌的在线逻辑分析仪(如XilinxISE中的ChipScope、AlteraQuartusII中的SignalTapII以及SignalProb)来解决上述矛盾,它们只需要占用芯片少量的逻辑资源,具有很高的实用价值。

FPGA总体设计的硬件考虑

FPGA在项目开始阶段需要考虑的设计主要有3大方面:一个是硬件做板相关的FPGA升级电路的设计以及外围IO设计;一个是与软件配合相关的软硬件接口设计;一个是FPGA内部的逻辑功能规划。本文先针对硬件设计相关进行阐述:

升级电路的设计:FPGA的好处就是产品发布后还能进行功能升级以及功能修改,但在客户那里应该没有人会愿意打开机箱进行升级,这时就要设计可靠的升级通路。

1)板上有配置器件:如果上电后FPGA需要快速配置,这时一般会采用SPIFLASH的配置方式,这时我们就要设计一个电路如何更新SPIFLASH,如果板上有CPU,可以直接写SPIFLASH,这种一般即使写错了,校验后重新写就好了。如果板上没有CPU,那FPGA内部或者配套的CPLD就要预留写FLASH的通路。这个通路实际上就是设计一个用户接口到SPI接口的桥接器,xilinx7系列以后的器件官方都提供了参考设计,而且支持SPIFlash中存入2个映像,其中一个是升级失败后起机的golden映像(否则升级文件写错,板就变成砖头了),虽然xilinx提供参考设计,但那只是针对SPIFLASH的操作,用户还要设计预留通道与这个控制器对接,比如以太、SPI之类。这时配合的软件就要考虑丢包、错包这些影响,要保证文件都正确写入FLASH。Altera公司应该也是提供类似东西,原理上总是相通的。但quartus能写入的一般都是自己的FLASH,否则就需要外接一个CPLD做配置电路,注意这个CPLD必须Altera自己的,否则不能用他的配置IP。

2)板上如果没有配置器件,那CPU直接通过被动配置方式进行配置,就是控制programe、status、DIN那几根线,CPU照时序做就好,缺点是CPU必须起来后才能进行配置。

3)目前还有一种配置就是通过PCIE接口,这个设计在电路上有一定要求,FPGA只需要挂接一个很小的SPIFLASH保存PCIE硬核的设置就好,起机后再把其他的功能映像从CPU端载入,这种一般再新的器件会支持,需要查看手册详细说明,不同器件再PCIE的复位以及其他引脚设计上还有要求。

这种配置一般用在PCIE的加速卡中,因为上电后系统会对PCIE设备进行扫描,一种好的做法就是通过SPIFLASH快速载入PCIE相关的映像,让枚举软件看到FPGA,CPU完全起机后,再把需要的功能配置进去。

硬件相关的第2个设计是外围IO的设计,包括VCCIO的电源连接、IO位置的分配、serdes的连接等。

虽然FPGA号称IO可以支持多种标准电平,但也不是可以随心所欲,特别是用到DDR3这些接口时。一种就是使劲看DS,但个人觉得太慢。好的做法是,建立一个demo工程,例化那些可能用到的外围IOIP,比如DDR,PCIE,以太接口等,把这些examle放在一个代码中不被优化掉,编译通过的话,一般IO分配就没问题了,有问题再看文档修改。编译通过后从工程导出IO配置的CSV文件,xilinx的会比较详细说明每个引脚的连接方式,包括端接等。Altera在工程目录下有个.pin文件,似乎也有类似说明。有了这个文件基本上可以保证做板不会范大错了。

-

硬件工程师面试必会:10个核心考点#硬件设计 #硬件工程师 #电路设计 #电路设计安泰小课堂 2025-09-23

-

硬件工程师看了只会找个角落默默哭泣#硬件工程师 #MDD #MDD辰达半导体 #产品经理 #软件工程师MDD辰达半导体 2025-06-09

-

硬件工程师VS软件工程师|硬件工程师看到这都泪目了!#硬件设计 #硬件工程师 #电子工程师 #软件工程师安泰小课堂 2024-09-25

-

求FPGA开发工程师、硬件开发工程师各一名2019-10-22 2683

-

如何给MCU工程师详解FPGA硬件属性?2019-09-18 2586

-

MCU工程师需要了解的FPGA硬件属性2019-07-03 783

-

给MCU工程师详解FPGA硬件属性2017-02-08 699

-

诚聘硬件研发工程师(FPGA)2016-11-14 3038

-

招聘:软件工程师(数字信号处理方向-FPGA)、硬件工程师2015-04-25 3731

-

诚招FPGA、硬件、模拟电路工程师2013-08-09 2403

-

电子工程师必须知道的几个技术问题2012-08-20 4063

-

电子工程师须知2012-05-10 3290

全部0条评论

快来发表一下你的评论吧 !