一窥ARM的AI处理器

电子说

描述

最近,ARM进一步公开了ML Procesor的一些信息。EETimes的文章“Arm Gives Glimpse of AI Core”[1] 和 AnandTech的文章“ARM Details “Project Trillium” Machine Learning Processor Architecture”分别从不同角度进行了介绍,值得我们仔细分析。

ARM公开它的ML Processor是在今年春节前夕,当时公布的信息不多,我也简单做了点分析(AI芯片开年)。

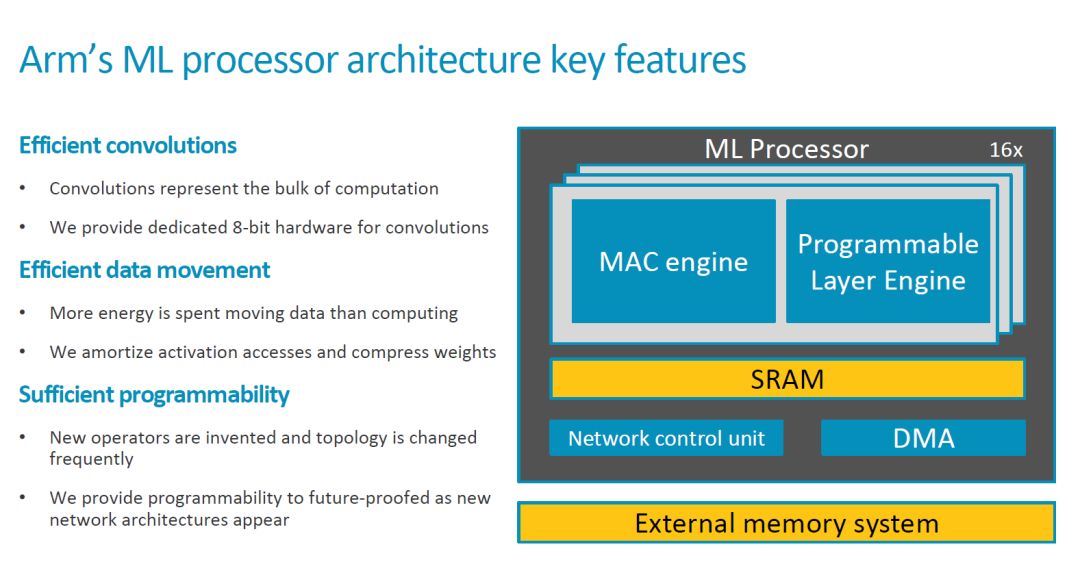

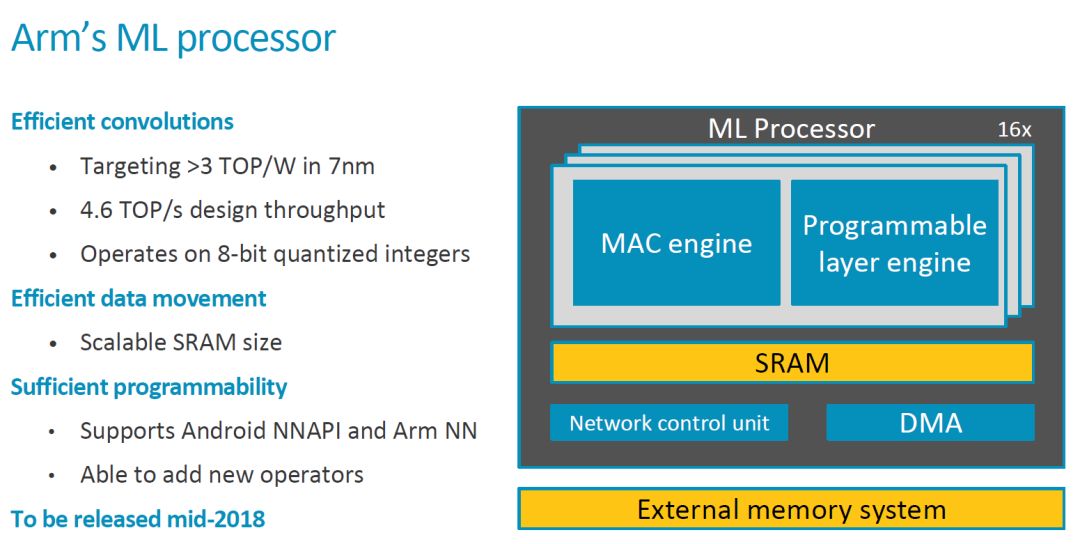

这次ARM公开了更多信息,我们一起来看看。首先是关键的Feature和一些重要信息,2018年中会Release。

•••

顶层架构

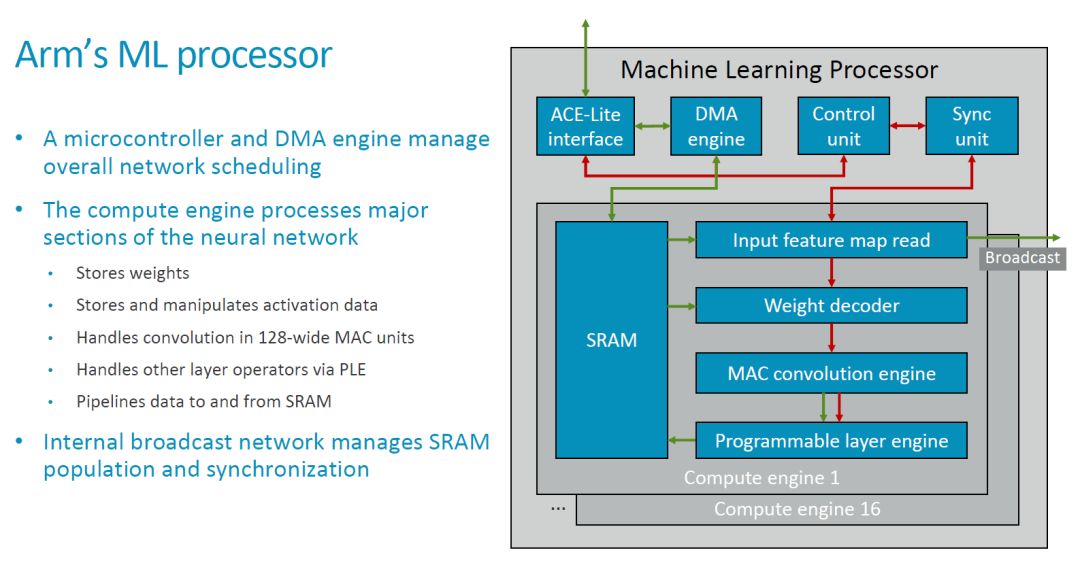

与最初公布的基本框图相比,我们这次看到了更细化的模块框图和连接关系,如下图所示。

MLP的顶层对外来看是个比较典型的硬件加速器,它有本地的SRAM,通过一个ACE-Lite接口和外部交互数据和主要的控制信息(指令)。另外应该还有一些控制信号,估计在这里略去了(可以参考Nvidia的NVDLA)。

在上图中绿色箭头应该表示的是数据流,红色表示控制流。MLP中的CE共享一套DMA,Control Unit和Sync Unit,它的基本处理流程大概是这样的:1. 配置Control Unit和DMA Engine;2. DMA Engine从外部(如DDR)读入数据存在本地的SRAM中;3. Input Feature Map Read模块和Weight Read模块分别读入待运算的feature map和weight,处理(比如Weight的解压缩),并发送到MAC Convolution Engine(后面简称为MCE);4. MCE执行卷积等操作,并把结果传输给Programmable Layer Engine(后面简称为PLE);5. PLE执行其它处理,并将结果写回本地SRAM;6. DMA Engine把结果传输到外部存储空间(如DDR)。

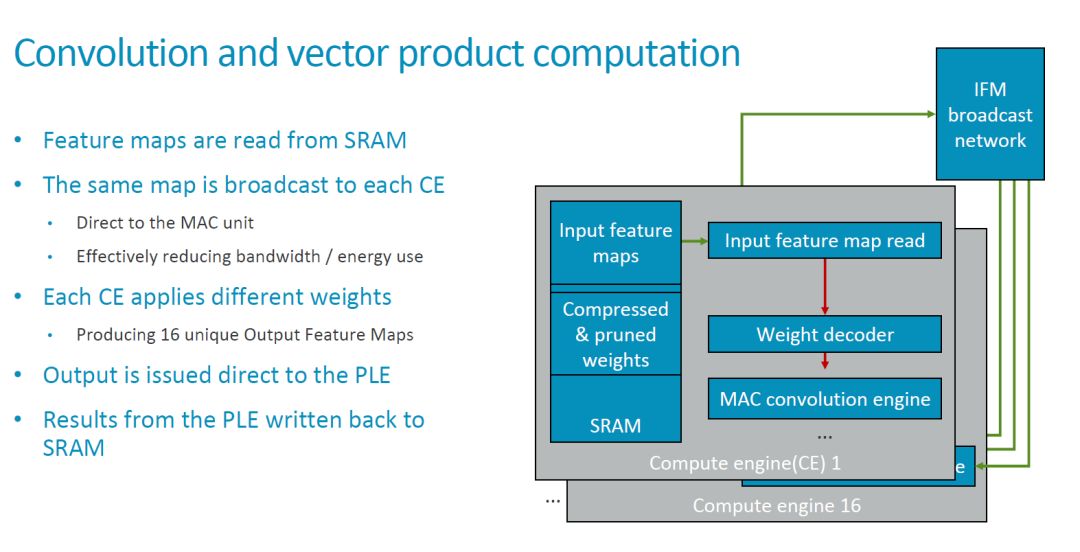

在顶层标出的Broadcast接口,实现在多个Compute Engine(后面简称为CE)之间广播feature map数据的功能。因此,基本的卷积运算模式是,相同的feature map广播到多个CE,不同的CE使用不同的weight来和这些feature map进行运算。

从目前的配置来看,MLP包括16个compute engine,每个有128个MAC,即一共有16x128=2048个MAC,每个cycle可以执行4096个操作。如果要实现ARM所说的4.6TOPS的总的处理能力,则需要时钟周期达到1.12GHz左右。由于这个指标是针对7nm工艺,实现问题不大。

•••

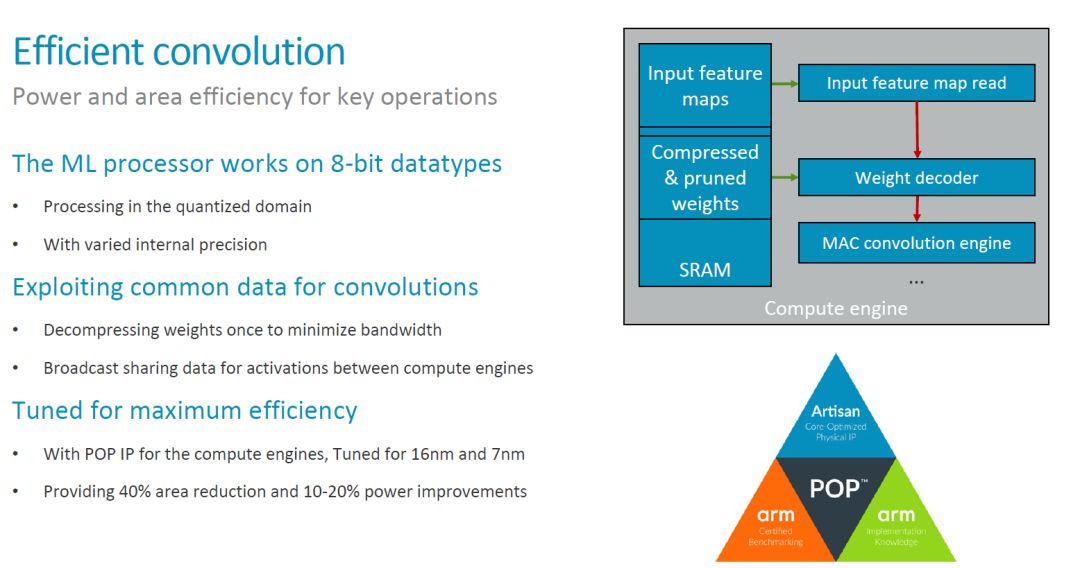

MCE实现高效卷积

在MLP的架构中,MCE和PLE是最重要的功能模块。MCE提供主要的运算能力(处理90%的运算),应该也是MLP中面积和功耗最大的部分。因此,MCE设计优化的一个主要目标就是实现高效的卷积操作。具体来讲,MLP的设计主要考虑了以下一些方法,这些方法大部分我们之前也都讨论过。

一个比较有趣的点是上面提到的“varied internal precision”。目前还不太清楚其具体的含义。不过对应用来说看到的应该是固定的8bit数据类型。至于对低精度Inference的支持,[1]中提供的信息是,“The team is tracking research on data types down to 1-bit precision, including a novel 8-bit proposal from Microsoft. So far, the alternatives lack support in tools to make them commercially viable, said Laudick.” 因此在第一版的MLP中,应该也不会看到低精度或者Bit-serial MAC了(参考AI芯片开年中对ISSCC2018出现的Bit-serial Processing的介绍)。

此外,数据的压缩和对工艺的优化也是提高整体效率的主要手段。特别是工艺的优化,结合ARM的工艺库,应该有比较好的效果,这也是ARM有优势的地方。

•••

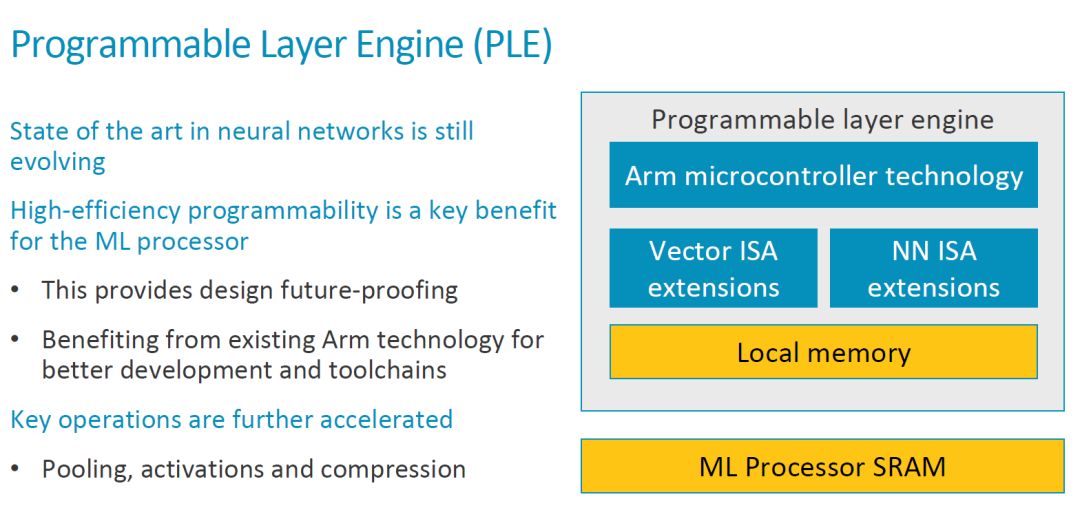

PLE实现高效的可编程性

如下图所示,PLE的结构基本是在一个ARM MCU基础上扩展了Vector处理和NN处理的指令。在讨论可编程性的时候,其出发点主要是NN算法和架构目前还在不断演进。

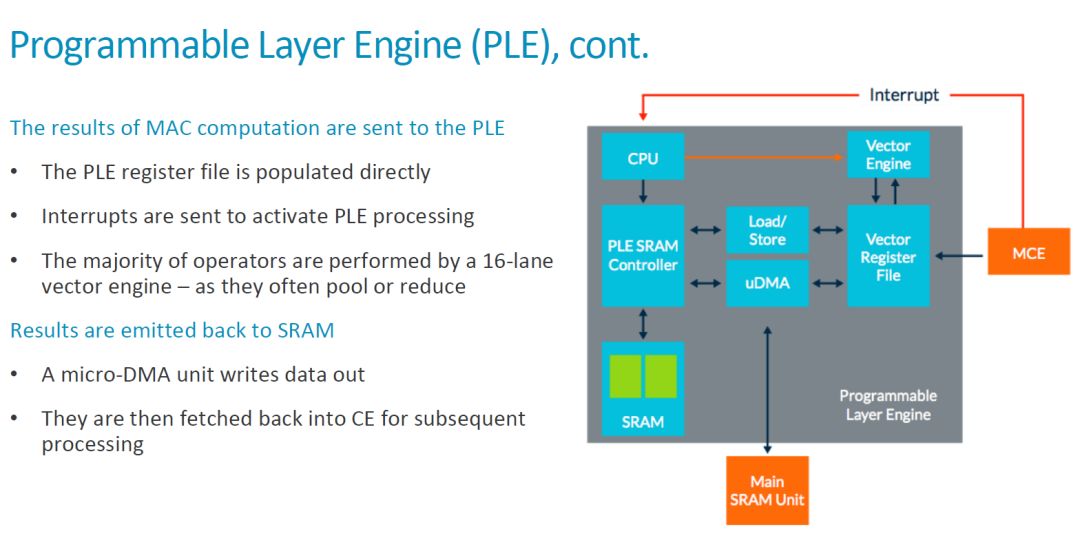

我们前面已经分析了整个MLP的基本工作流程,MCE在完成了运算之后把结果传输给PLE。从这里可以看出,MCE应该是把结果发送到Vector Register File(VRF),然后产生中断通知CPU。之后,CPU启动Vector Engine对数据进行处理。具体如下图所示。

对于做专用处理器的同学来说,这种scalar CPU+vector engine的架构并不陌生。这里,本地SRAM,VRF和PLE之外的Maing SRAM Unit(CE中的SRAM)之间有Load/Store单元和uDMA实现数据的传输,数据流也是比较灵活的。综合来看,在MLP中,每个CE中都有一个PLE和MCE配合,即每个MCE(128个MAC)就对应一个可编程架构。因此,ARM MLP的可编程性和灵活性是要远高于Google TPU1和Nvidia的NVDLA的。当然,灵活性也意味着更多额外的开销,如[1]中指出的,“The programmable layer engine (PLE) on each slice of the core offers “just enough programmability to perform [neural-net] manipulations””。High-efficient Programmability是MLP的一个主要卖点之一,而ARM的“just enough”是否真是最合适的选择,还有待进一步观察。

•••

其它信息

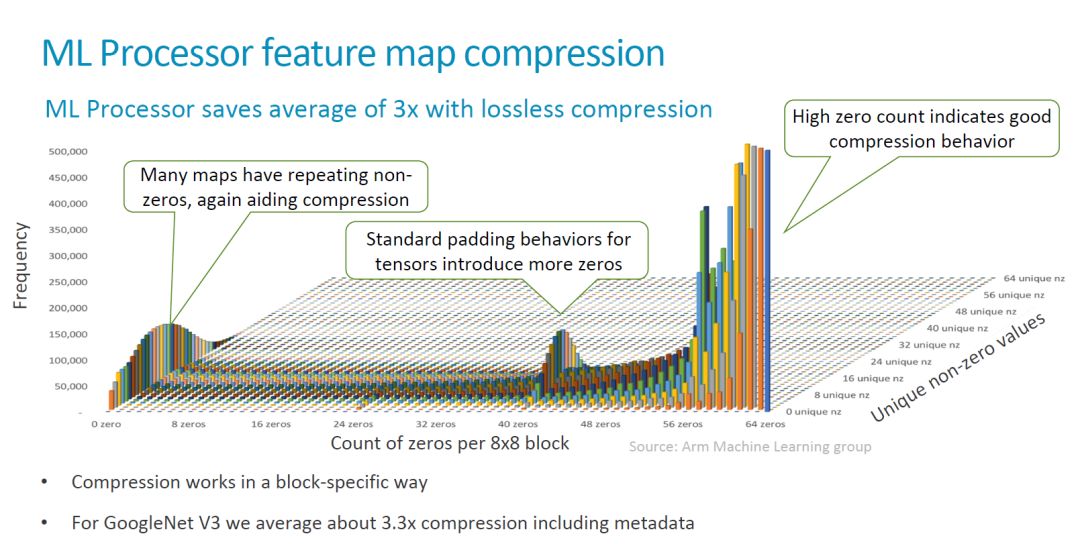

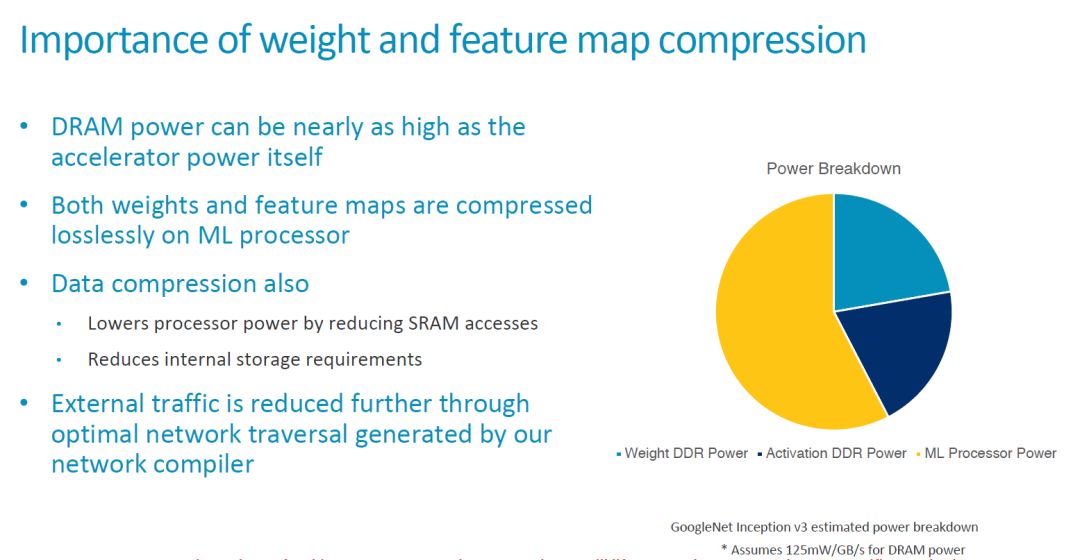

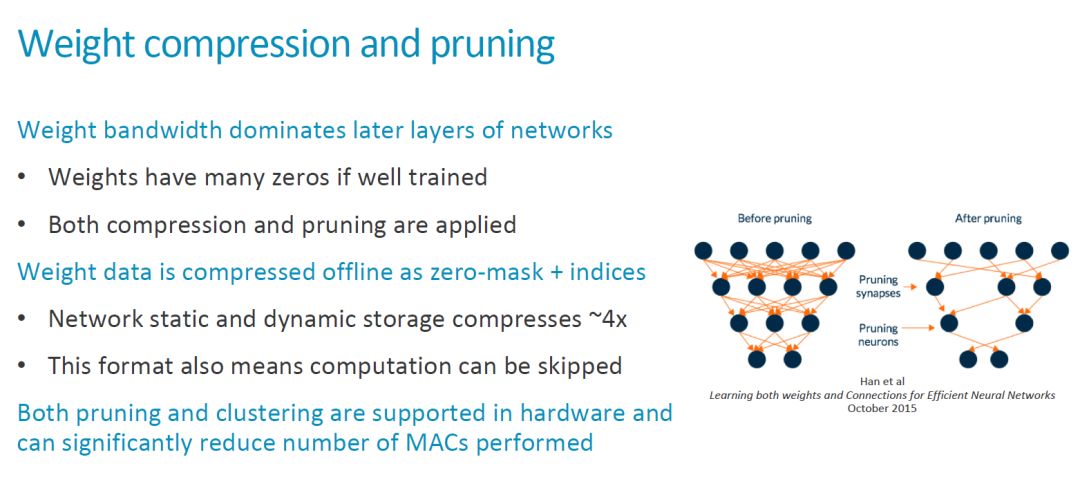

在这次发布中信息中,ARM还强调了他们在数据压缩方面的考虑,包括对lossless compression的硬件支持。这部分内容我在之前的文章中也有比较多的讨论,就不再赘述了,贴几张比较有意思的图,大家看看。

作为一个IP核,可配置性(configurability)是一个重要的特征。目前还不知道MLP有哪些硬件参数可以支持灵活配置。Compute Engine的数量,MAC数量,SRAM大小,这些比较大的参数应该有可能是支持配置的。其它更细致的内容还要看最终发布的情况。另外,这些参数的配置和相关的软件工具有非常密切的关系,更多的可配置参数也意味着软件工具需要相应的支持,难度更大。[2]对此的说法:“In terms of scalability the MLP is meant to come with configurable compute engine setups from 1 CE up to 16 CEs and a scalable SRAM buffer up to 1MB. The current active designs however are the 16CE and 1MB configurations and smaller scaled down variants will happen later on in the product lifecycle.”

•••

竞争态势

除了比较中规中矩的性能指标外,ARM还没有公布MLP具体的面积,功耗等参数,以及具体发布的日期(目前的说法是“production release of the RTL is on track for mid-year”)。

在这个已经比较“拥挤”的市场,ARM显然是动作比较慢的。[1]一开始就提到了,“Analysts generally praised the architecture as a flexible but late response to a market that is already crowded with dozens of rivals.”并列举了一些竞争对手的例子。

其实,从ARM在处理器IP市场和整个生态链的关键地位来看,晚一点关系也不大。如[1]所说,一方面,ARM正在和一些智能手机厂商进行深度的合作,“In a sign of Arm’s hunger to unseat its rivals in AI, the company has “gone further than we normally would, letting [potential smartphone customers] look under the hood””。

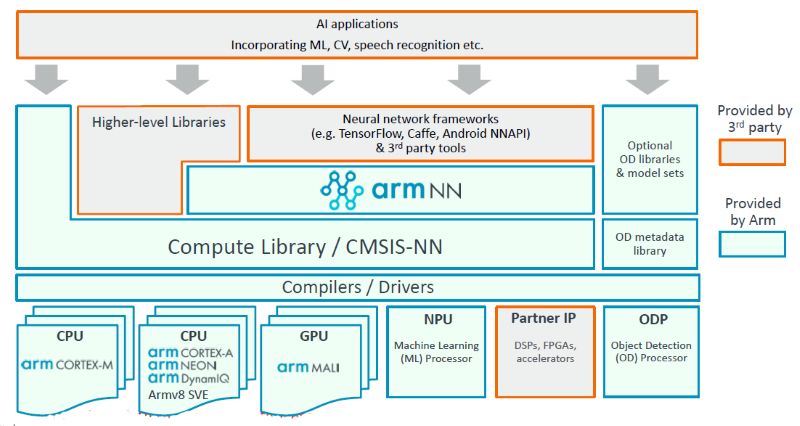

ARM的另一个重要优势是,ARM在推出MLP之前在软件工具上还是有一些准备的,包括armnn和开源的计算库等等,如下图。

这些工具的广泛使用都可以帮助ARM积累经验,优化硬件和软件工具。正如[1]中引用来自ARM的说法,“Winning the hearts and minds of software developers is increasingly key in getting design wins for hardware sockets...This is kind of the start of software 2.0. For a processor company, that is cool. But it will be a slow shift, there’s a lot of things to be worked out, and the software and hardware will move in steps.”

我们也看到,目前大量的嵌入AI应用还是运行在ARM的各种硬件上的,很多公司在相关算法和实现的优化上投入了很大的力量,也取得了很好的效果。当然这样带来另一个有趣的问题,那就是未来引入MLP之后,ML任务到底放到哪里跑?不同特点的处理器怎么配合?文章中正好也提到这个问题,“Arm will release more data on the core’s performance when it is launched, probably in mid-June. But don’t expect detailed guidance onwhen to run what AI jobs on its CPU, GPU, or new machine-learning cores, a complex issue that the company, so far, is leaving to its SoC and OEM customers.” 看来这个“难题”短期之内还是丢给用户了。

另外一个值得关注细节是,[1]中提到,“Theoretically, the design scales from 20 GOPS to 150 TOPS, but the demand for inference in the Internet of Things will pull it first to the low end. Arm is still debating whether it wants to design a core for the very different workloads of the data center that includes training. “We are looking at [a data center core], but it’s a jump from here,” and its still early days for thoughts on a design specific for self-driving cars, said Laudick.”从这里可以看出,至少MLP在处理能力上还是具有比较强的伸缩性的,应该可以覆盖从Edge到Cloud的大部分的inference应用。如果是最高的150TOPS,MAC的规模应该和Google第一代Inference专用的TPU类似,不过相比Google的脉动阵列架构,MLP有更复杂的控制通道,灵活性还是要高不少。不知道未来,这会不会帮助ARM打开data center的inference市场。

参考:

1."Arm Gives Glimpse of AI Core", https://www.eetimes.com/document.asp?doc_id=1333307

2."ARM Details “Project Trullium” Machine Learning Processor Architecture", https://www.anandtech.com/show/12791/arm-details-project-trillium-mlp-architecture.

-

arm处理器有哪些中断源?arm处理器对异常中断的响应过程2023-10-19 2289

-

什么是ARM处理器?2021-11-24 2462

-

什么是ARM处理器 ARM处理器有哪些系列2019-09-24 6742

-

解答arm是什么/arm处理器采用什么技术2018-10-26 8617

-

arm的协处理器有几个?ARM协处理器详解2018-04-24 9605

-

ARM处理器简介及RISC设计要点2018-04-01 9845

-

arm是什么处理器,arm处理器汇总2017-11-10 3618

-

初识ARM系列处理器2017-10-18 2075

-

基于ARM和CPLD的无线内窥系统设计2017-01-24 597

-

ARM处理器及ARM处理器工作模式2011-01-27 2676

-

ARM,ARM处理器是什么意思2010-03-26 5576

-

ARM处理器的工作模式2010-03-01 701

-

ARM微处理器的编程模型2008-09-09 612

全部0条评论

快来发表一下你的评论吧 !