基于FPGA的模糊PID控制器的设计实现

电子说

描述

FPGA技术的快速发展与VHDL(VeryhighspeedintegratedcircuitHardwareDescriptionLanguage)硬件描述语言的支持,使得智能控制策略(模糊逻辑、神经网络、遗传算法等)的VHDL描述和FPGA固核实现研究也随之活跃。在模糊逻辑控制方面,Torralba等人完成了4输入、12个隶属度、64条规则的模糊逻辑控制器的FPGA实现,Cirstea等人基于FPGA设计模糊控制器。本文主要详解基于FPGA的模糊PID控制器的设计实现,首先介绍了FPGA工作原理、基本特点以及FPGA的优势,其次阐述了使用Altera的FPGA设计实现的数字模糊PID控制器,具体的跟随小编一起来了解一下。

FPGA工作原理

FPGA采用了逻辑单元阵列LCA这样一个概念,内部包括可配置逻辑模块CLB、输出输入模块IOB和内部连线三个部分。FPGA利用小型查找表(16&TImes;1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了即可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能, 加电时,FPGA芯片将EPROM中数据读入片内编程RAM中,配置完成后,FPGA进入工作状态。掉电后,FPGA恢复成白片,内部逻辑关系消失,因此,FPGA能够反复使用。FPGA的编程无须专用的FPGA编程器,只须用通用的EPROM、PROM编程器即可。当需要修改FPGA功能时,只需换一片EPROM即可。这样,同一片FPGA,不同的编程数据,可以产生不同的电路功能。FPGA是由存放在片内RAM中的程序来设置其工作状态的,因此,工作时需要对片内的RAM进行编程。用户可以根据不同的配置模式,采用不同的编程方式。

FPGA的基本特点

1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。

2)FPGA可做其它全定制或半定制ASIC电路的中试样片。

3)FPGA内部有丰富的触发器和I/O引脚。

4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。

5) FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

FPGA的优势

优势一:

更大的并行度。这个主要是通过并发和流水两种技术实现。

A:并发是指重复分配计算资源,使得多个模块之间可以同时独立进行计算。这一点与现在的多核和SIMD技术相似。但相对与SIMD技术,FPGA的并发可以在不同逻辑功能之间进行,而不局限于同时执行相同的功能。举个简单例子说就是使用SIMD 可以同时执行多个加法,而FPGA可以同时执行多个加法和乘法和任何你能设计出来的逻辑。

B:流水是通过将任务分段,段与段之间同时执行。其实这一点和CPU相似,只是CPU是指令间的流水而FPGA是任务间流水或者可以说是线程间流水。

优势二:

可定制。FPGA 内部通过Lookup Table实现逻辑,可以简单理解为是硬件电路。可定制指的是在资源允许范围内,用户可实现自己的逻辑电路。通常情况下任务在硬件电路上跑是比在软件上快的,比如要比较一个64位数高32位和低32位的大小,在CPU下需要2条区数指令,两条位与指令,一条移位指令一条比较指令和一条写回指令,而在FPGA下只要一个比较器就行了。

优势三:

可重构。可重构指的是FPGA内部的逻辑可根据需求改变,减少开发成本。同时,使用FPGA复用资源比使用多个固定的ASIC模块为服务器省下更多的空间

基于FPGA的模糊PID控制器的设计实现

一、控制器原理

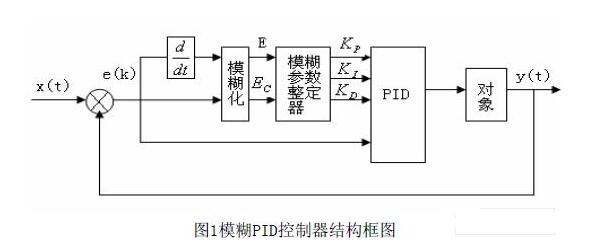

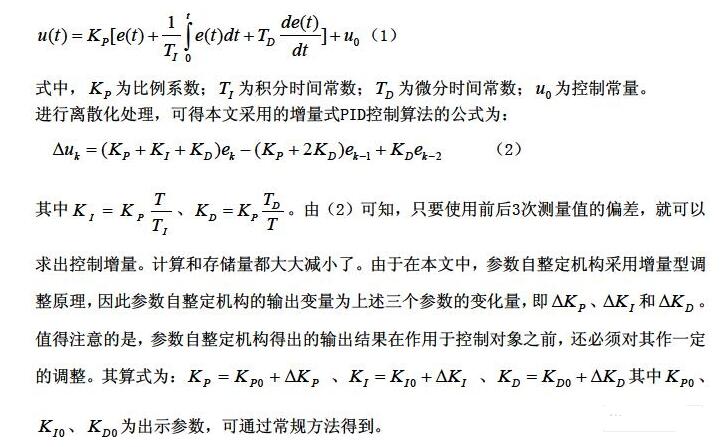

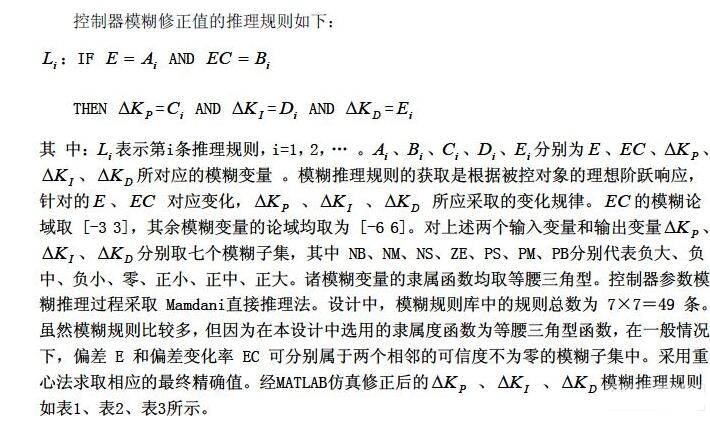

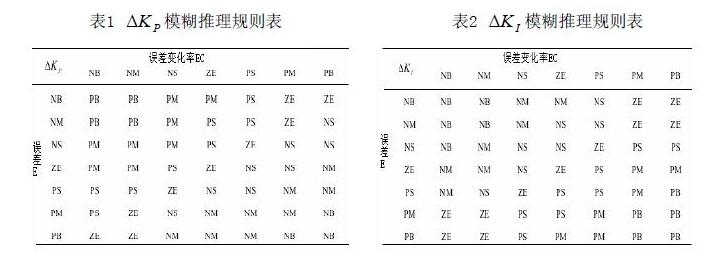

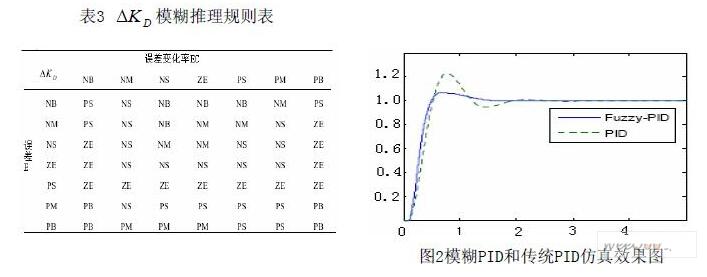

模糊自整定PID控制器结构:是模糊控制器与传统PID控制器的结合,利用模糊推理判断的思想,根据不同的偏差、偏差变化率对PID的参数KP、KI、KD进行在线自整定,传统PID控制器在获得新的KP、KI、KD后,对控制对象输出控制量。由此模糊PID控制器的结构框图如图1所示。

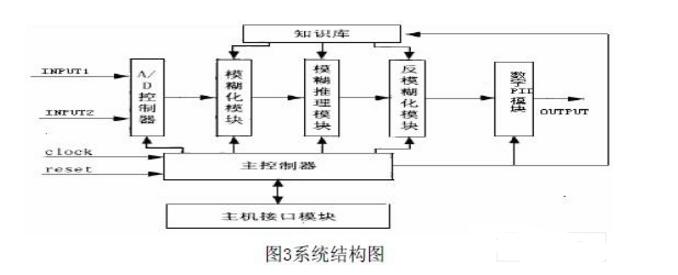

二、控制器的VHDL分层设计

模糊PID控制器主要由A/D控制器、模糊化模块、模糊推理模块、反模糊化模块、规则存储器、数字PID运算等部分组成,其结构如图3所示。现就模糊化模块、模糊推理模块、反模糊化模块等主要模块的建立来描述VHDL的设计过程。

1、模糊化模块

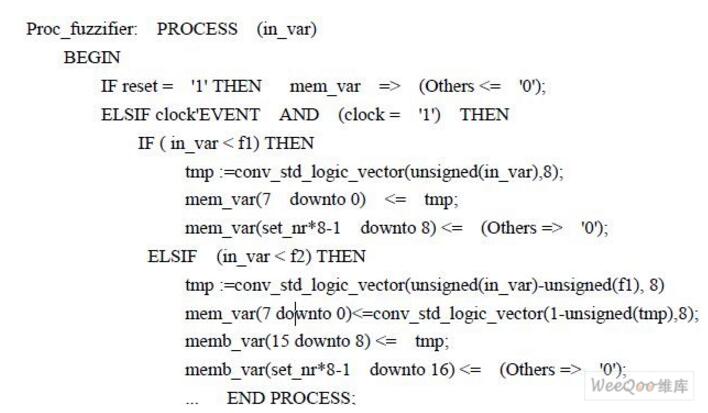

模糊化模块的功能主要包括两部分:把输入的精确量进行尺度变换,变换到相应的论域范围;将己变换到论域范围的输入量进行模糊化处理,主要是计算各个输入量的隶属度。由于变量的隶属度函数均取用等腰三角形,则底边宽度和底边中点就可以确定隶属函数的所有信息。分别用一个字节表示每个语言变量的底边宽度(实际宽度的一半),用三个位(bit)表示底边中点位置,将这部分信息存在两个表中。根据两个表中的信息,可以计算出输入变量的隶属度。为实现隶属度的计算,需要用到一个加法器,一个减法器和一个除法器。计算的结果肯定是小数(由隶属度的性质可知)。为了实现方便,将分子的计算结果左移8位。这样,分子的计算结果是16位,分母是8位,计算结果是8位。对其部分输入进行模糊化的VHDL描述如下:

2、模糊推理模块

模糊推理模块是模糊控制器的核心,它将输入的模糊量经过推理,变为输出的模糊量。模糊推理采用Mamdani推理,也称为Max一Min推理,即最大一最小推理,因为其中主要包括最大化模块和最小化模块。对于两输入系统,最多输出四个语言值和四个隶属度。这样,对于一个两输入系统,最多激活四条模糊规则。上述过程就是规则匹配的过程。规则匹配需要最小化运算,即Min运算。规则合并就是将后件相同的模糊规则进行合并,规则合并需要最大化运算,即Max运算。由模糊化模块计算所得的四个隶属函数值在控制信号作用下经过多路选择器输入到比较器;另外两个控制信号经过译码后选中隶属函数寄存器中的一个,同时选择输出最小值到比较器;比较器的输出结果再输入到隶属函数寄存器中。这样,经过4个循环,就完成了一个最小化运算。由于VHDL描述简单,在这里省略。

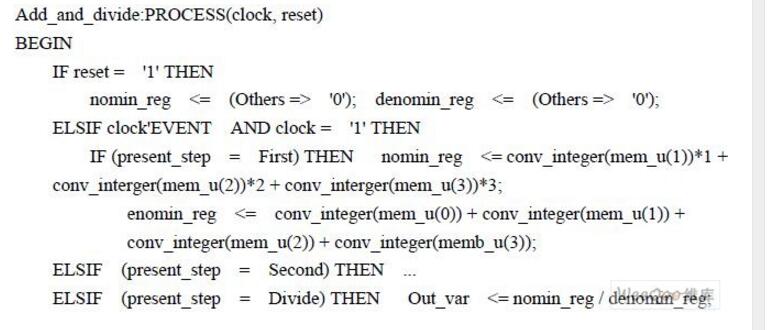

3、反模糊化模块

反模糊化通常采用重心法,由于隶属度函数采用8为二进制表示,而所涉及的规则数最多为4条,所以分子运算需要四个8位x2位的乘法器,3个10位加法器,分母需要3个8位加法器。此外,还需要一个12位/10位的除法器。除法器的设计方法与模糊化模块中的设计方法相同。而乘法器的设计也与除法器的设计方法相似。相应的VHDL描述如下:

4、数字PID运算模块

数字PID运算主要是加、减、乘的运算,运用原码算法设计数字电路无疑增加电路的复杂度。而采用补码运算进行设计就简单多了。加减法运算都可以用相同的加法电路来实现。设计乘法电路的方法很多,考虑到节省FPGA器件资源问题,采用BOOTH算法。主要涉及累加器溢出处理和小数运算处理等问题。

三、试验结果

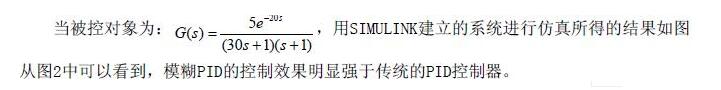

借助MATLAB的模糊控制工具箱提供的FIS编辑器建立mamdani型的模糊控制器,并结合Simulink工具箱建立FuzzyPID控制系统仿真模型。仿真得到的系统阶跃响应如图2。通过图可以看出Fuzzy-PID控制调节时间短,超调量小,曲线平滑,具有较强的抗干扰和鲁棒性。

各模块程序经过编译优化之后,由QuartusⅡ软件综合并生成网表文件,最后下载到Altera公司的Cyclone系列的EP1C6Q240C8芯片上。经实际测试显示,该模糊PID控制器控制效果明显优于普通的PID控制器。

四、结论

本文使用Altera的FPGA设计实现了一个数字模糊PID控制器。其中PID部分采用增量式算法,模糊控制部分采用离线计算、在线查表的方式实现,在不增加硬件资源耗费的前提下大大改善了普通PID控制器的控制效果。同时,FPGA作为单一控制器实现模糊自整定PID控制,编程规范、时序验证方便、系统修改灵活,且基本无须改动硬件,是实现单片或小系统智能控制策略的一种新的有效途径。

-

怎样去编写PID控制器和模糊控制器代码呢2021-11-19 3066

-

请问如何去设计模糊PID自整定控制器?2021-04-21 2935

-

快速浮_定点PID控制器FPGA的研究与实现2016-05-11 628

-

直流调速系统的模糊PID控制器设计实现2016-04-06 985

-

基于模糊PID控制的导弹舵机伺服控制器2016-04-05 1196

-

模糊自适应PID控制器设计2016-01-18 730

-

基于FPGA的模糊PID控制算法的研究及实现2013-03-18 9596

-

基于FPGA的温度模糊控制器的实现2013-03-15 1254

-

一种简化PID模糊控制器的研究与设计2013-02-21 832

-

基于FPGA的温度模糊自适应PID控制器的设计2010-01-22 1716

-

基于遗传算法和模糊PID的励磁控制器2010-01-18 521

-

一种新型的模糊PID控制器介绍2009-04-10 499

-

简化的模糊PID控制器研究2009-03-16 675

-

参数自适应模糊PID控制器的设计2009-02-27 2638

全部0条评论

快来发表一下你的评论吧 !