全新的Vivado项目功能 可配置的报告

电子说

描述

对设计的合并可能会很棘手。通常当你需要解决一个问题时,变化会影响设计的其他部分,从而不可避免地会出现其他问题。在2017.3我们推出了一项新功能可以帮助您解决这个问题。该功能被称作可配置报告。

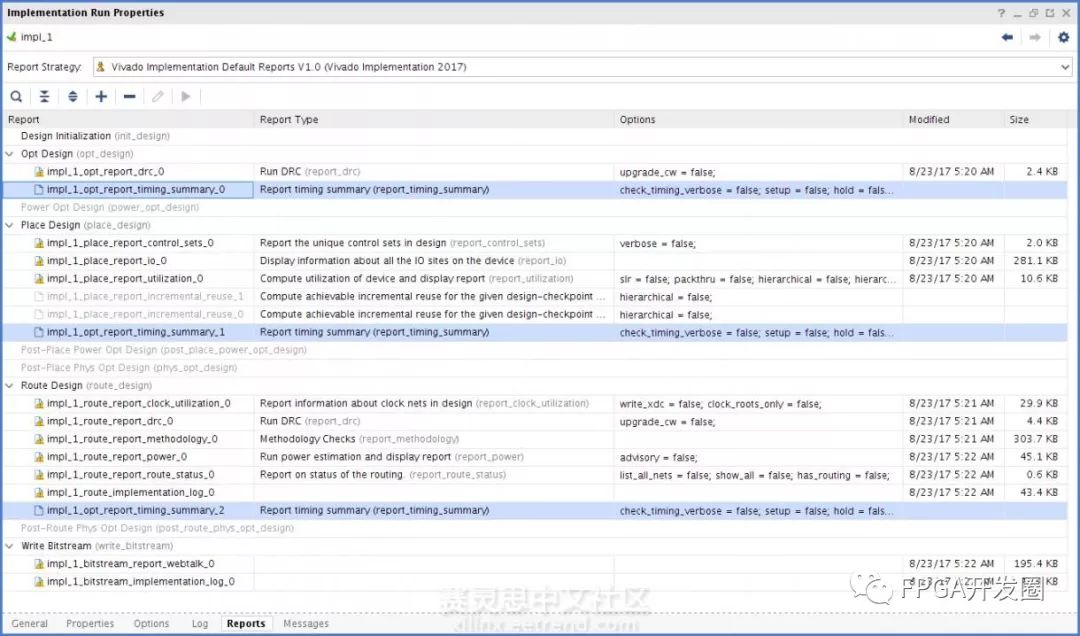

可配置的报告是一项全新的Vivado项目功能,可让您在流程的任何步骤运行任何报告。例如,假设您在实现后出现一个关键路径,而且您不确定如何解决它。为了理解这条关键路径如何在流程间“演变”,可配置的报告使得您可以在完成逻辑优化,布局设计,布线设计以及这之间的任何步骤报告那条确切路径的时序情况。图1显示了被添加到每个实现流程步骤的报告时序总结。了解每个步骤的时序可以帮助您理解问题是综合问题,利用率问题,时钟分配问题还是布线拥塞问题。

图 1. 在运行实现属性选项卡中配置时序统计报告在三个流程运行完成之后再生成

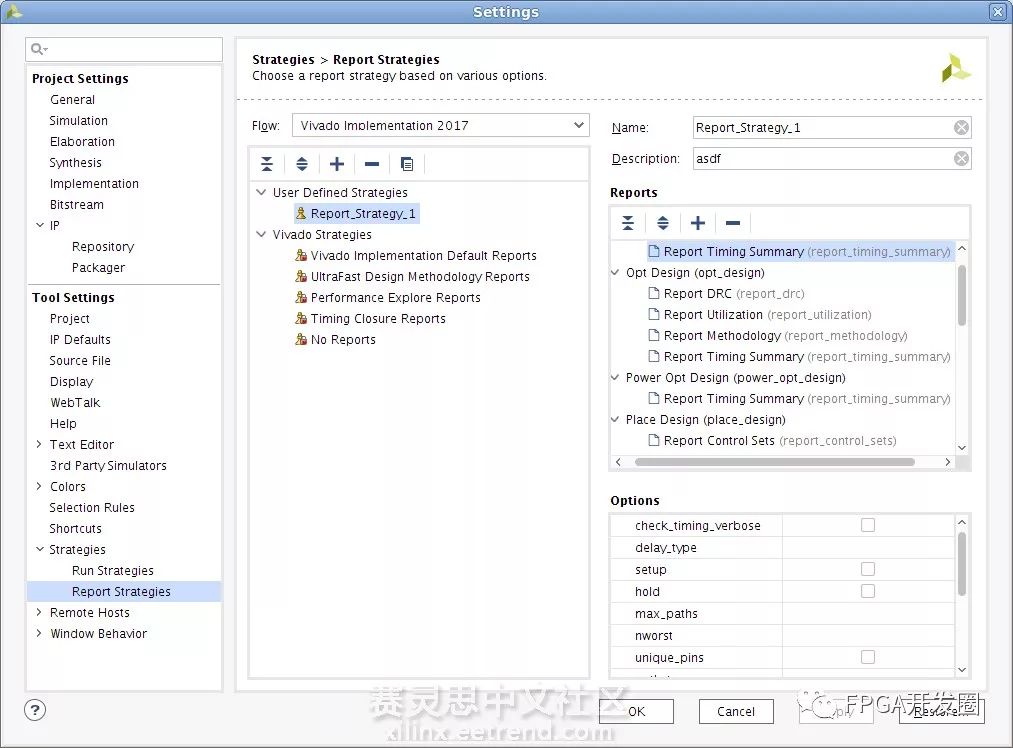

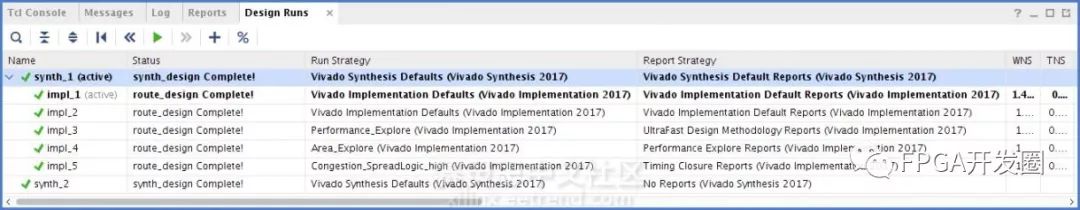

基于上文对可配置报告的描述,我们将介绍报告策略的概念。类似于运行策略允许您调整Vivado的性能以满足您的独特需求,报告策略允许您根据您的设计定制报告。 您可以配置报告策略并在不同运行甚至不同项目间复用。我们提供了几个预先配置的策略,包括:UltraFast方法报告,性能探索报告,时序收敛报告,或者,如果您仅仅想运行的更快,可以选择no reports选项。图2显示了工具设置窗口,用户可以在其中创建自己的自定义策略或查看Xilinx推荐的策略。图3显示了设计运行窗口,其中包含多个配置了不同运行和报告策略的实现和综合运行。

图 2. 工具设置窗口,允许用户创建自己的自定义策略

图 3. 设计运行窗口显示了几种运行和报告策略

可配置的报告可让您灵活地决定哪些报告对您的设计最为关键,并使您能够专注于解决您的独特问题。 当你最终推动并结束您的设计时,唯一会遇到的问题就是打开庆祝酒瓶的软木塞子!“砰!”Bingo!

关于作者Brian Lay是Vivado IDE和支持基础架构的高级产品营销经理。作为IDE营销经理,他曾参与Xilinx许多不同的项目,包括时序约束向导,部分重新配置的项目支持以及运行时硬件调试等。Brian拥有伊利诺伊大学厄巴纳-香槟分校电气工程硕士学位和明尼苏达大学的本科学位。他曾在Sun Microsystem和Advanced Micro Devices工作过,拥有超过17年的经验。他的技能包括全定制电路设计,综合布局布线,时钟分配设计,全芯片集成以及时序,噪声,功耗,DRC,IR压降的各个方面,以验证CPU,GPU和FPGA中的这些电路。

- 相关推荐

- 热点推荐

- Vivado

-

印刷电路板(PCB)可配置逻辑功能2023-08-29 962

-

如何读懂Vivado时序报告2023-06-23 2958

-

超可配置的多功能门;三态-74LVC1G992023-02-20 442

-

低功耗双PCB可配置多功能门-74AUP2G582023-02-17 390

-

低功耗可配置多功能门-74LVC1G97_Q1002023-02-14 377

-

低功耗可配置多功能门-74LVC1G98_Q1002023-02-07 457

-

求助,如何把一个非CubeMX项目变成STM32CubeMX可配置?2023-01-06 525

-

Gowin可配置功能单元用户指南2022-09-28 1157

-

Gowin可配置功能单元(CFU)用户指南2022-09-14 493

-

Vivado下显示指定路径时序报告的流程2021-01-15 3495

-

如何创建Vivado HLS项目2018-11-20 4493

-

VIVADO中使用MB如何配置冷启动2017-02-08 722

-

Xilinx 发布Vivado2013.3新增全新设计方法及功能2013-10-29 987

全部0条评论

快来发表一下你的评论吧 !