聊一聊接收端物理层逻辑子层的实现细节

电子说

描述

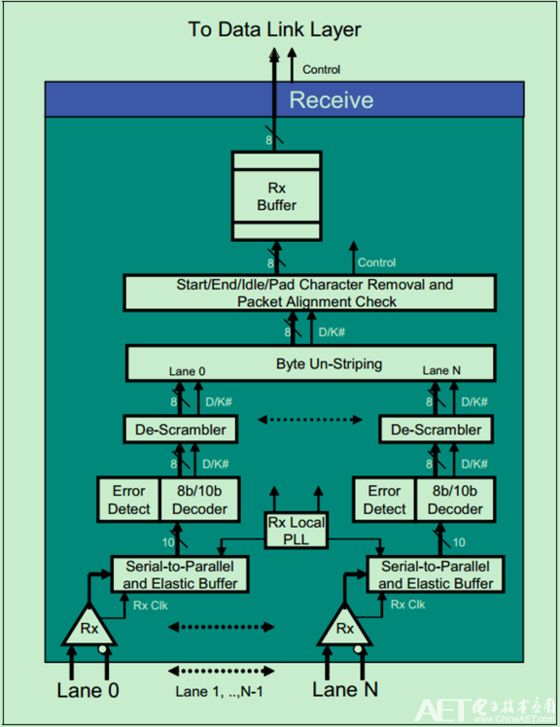

这一篇文章来继续聊一聊接收端物理层逻辑子层的实现细节。回顾一下之前的那张图片:

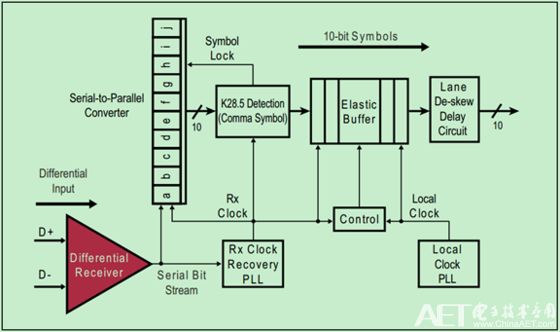

其中的一个Lane的具体逻辑如下图所示:

其中,Rx Clock Recovery从输入的串行数据流中提取出Rx Clock。当Rx Clock稳定在Tx Clock的频率上(Rx Clock locked on to the Tx Clock Freq)时,我们就称接收端取得了Bit Lock。

如果链路(Link)处于低功耗状态(比如L0s或者L1)时,接收端此时会失去同步(即Losing Bit Lock)。为了避免物理层认为这是一个错误(异常),发送端会发送一个电气空闲命令集(Electrical Idle Ordered Sets,EIOS)通知接收端,即将进入低功耗状态。此时,接收端会临时关闭(De-gate)其输入。

注:这里的关闭(De-gate)并非是直接关闭输入端口,只是暂时不对输入端口上的数据进行处理。

当发送端需要唤醒链路(Link)时,会首先发送一定数量的FTS Ordered Sets,并重新取得Bit Lock和Symbol Lock。

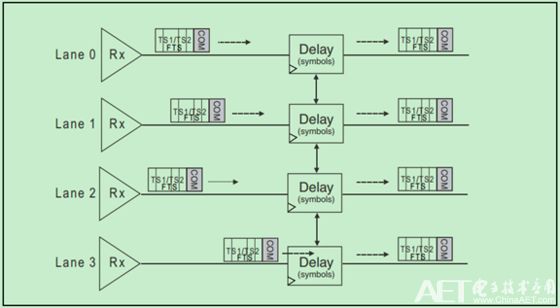

接收端的链路De-Skew逻辑如下图所示:

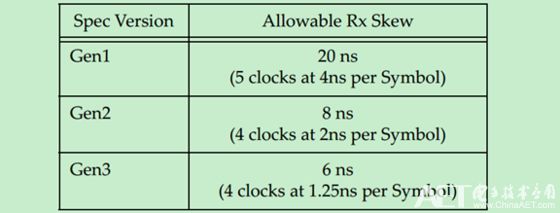

Gen1和Gen2的PCIe采用COM字符来进行De-Skew,如果COM没有同事出现在每个Lane上,那么先到达的COM会被延时一会,以实现Lane的同步。很显然,这种机制只能校正比较小的Skew,也就是说Lane-to-Lane的Skew有一个最大值,超出这个最大值,De-Skew也无能为力了。如下表所示:

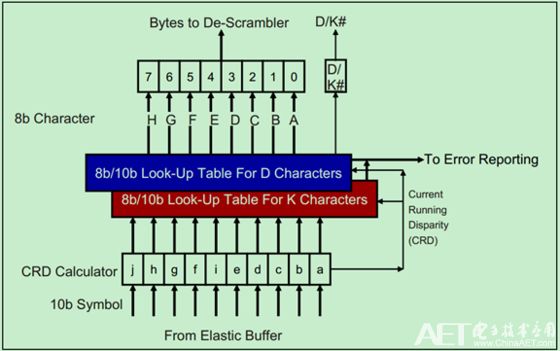

接收端的8b/10b解码器结构如下图所示:

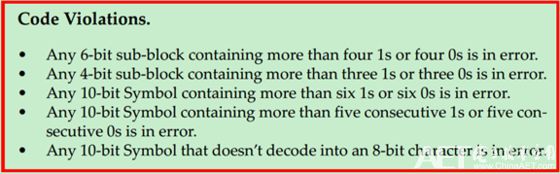

以下情况,被认为是编码冲突(Code Violation),即该字符在传输过程中发生了错误:

关于解扰码器(Descrambler)和Byte Un-striping都比较简单了,这里就不在详细地介绍了。具体可以参考PCIe Spec的相关内容。

-

RapidIO标准的串行物理层实现2025-12-09 734

-

MultiGABSE-AU物理层PMA子层及PMD子层的相关机制2024-12-23 2101

-

如何搞定通信物理层?物理层包含哪些内容?如何落地实现呢?2023-11-20 4636

-

WLAN物理层关键通信技术2023-05-19 749

-

分析802.11标准在物理层的定义2022-11-09 7189

-

串口通信的物理层与协议层的相关资料推荐2022-02-17 969

-

什么是以太网物理层?Ethernet物理层有哪些功能?2021-03-18 6230

-

三种不同类型以太网物理层的编码规则和测试分析2019-08-29 29848

-

CAN总线不同的物理层2019-05-23 2915

-

PCIe物理层接口定义了物理层中的,媒介层和物理编码子层之间的统一接口2018-09-07 9942

-

物理层的成帧过程2010-02-09 1565

-

USB3.0的物理层接收端的测试方法 (完整版)2009-10-08 7632

-

WCDMA系统的物理层(FDD)2009-06-14 819

-

物理层的作用2008-07-22 7218

全部0条评论

快来发表一下你的评论吧 !