【深度解析】硬件电路设计:如何确保嵌入式数据可靠性?

描述

在嵌入式系统开发中,硬件电路设计是确保数据可靠性的关键环节。本期我们将重点探讨硬件设计中的两个重要方面:数据读写保护和掉电保护。

硬件电路设计

硬件电路设计

在嵌入式系统开发中,硬件电路设计对于确保数据的可靠性和系统的稳定性起着至关重要的作用。电源管理、信号完整性、电磁兼容性(EMC)、数据读写保护和掉电保护等都是硬件电路设计的关键方面。这些要素相互配合,共同构建了一个既可靠又高效的硬件平台。今天,我们将重点深入探讨数据读写保护和掉电保护这两个至关重要的环节。 数据读写保护

数据读写保护

在硬件电路设计中,数据读写保护是确保数据完整性和安全性的关键。NAND Flash芯片通常配备一个写保护引脚(#WP),但在实际设计中,许多工程师往往会忽略这个引脚,导致芯片始终处于可写状态。这种设计存在潜在风险,可能会导致数据被意外写入或覆盖,从而影响数据的完整性和可靠性。

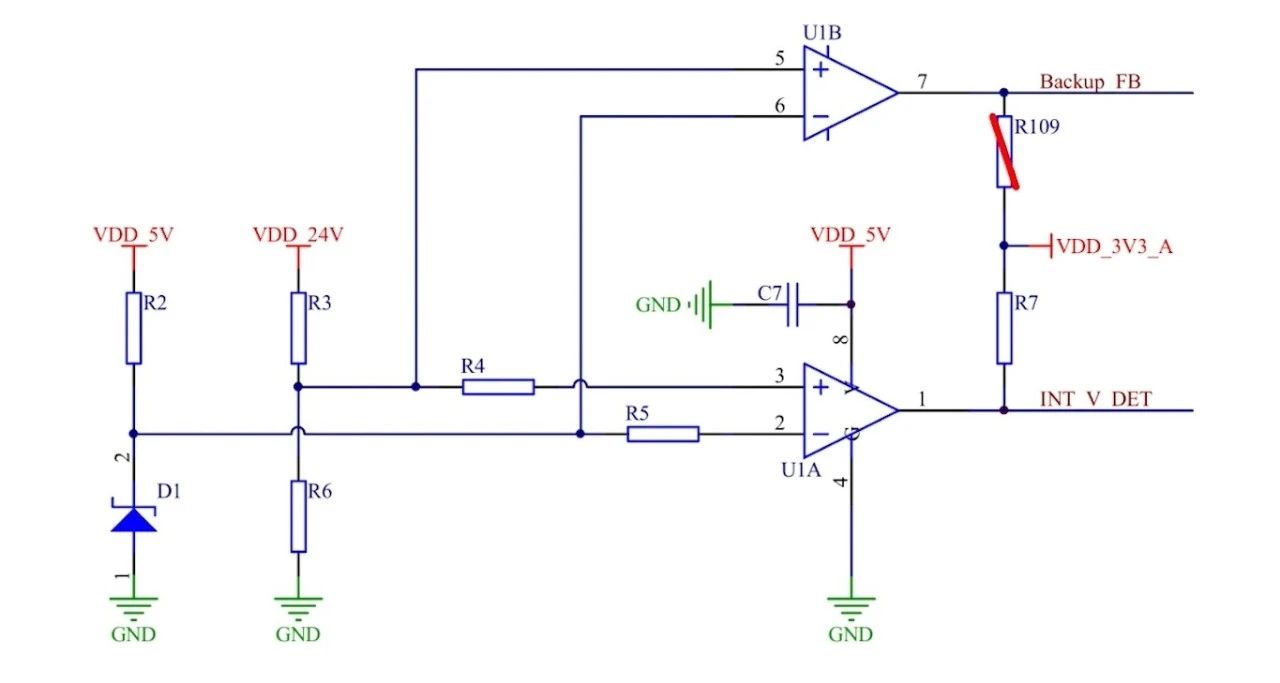

图1 带NAND写保护的电路图

1. 写保护引脚(#WP)的作用

写保护引脚(#WP)是NAND Flash芯片的一个重要特性,用于防止数据被意外写入或覆盖。当#WP引脚被设置为低电平时,芯片进入只读模式,数据无法被写入或修改。当#WP引脚被设置为高电平时,芯片进入可写模式,可以进行数据写入操作。

2. GPIO控制#WP引脚

建议在硬件设计时,使用一个GPIO引脚来控制#WP引脚。这样可以确保芯片在大多数时间处于只读状态,仅在需要写入数据时才切换到可写模式。这种设计不仅提高了数据的安全性,还减少了因意外写入导致的数据损坏风险。具体实现方法:

- 硬件连接:将NAND Flash芯片的#WP引脚连接到微控制器的一个GPIO引脚。

- 软件控制:通过微控制器的GPIO控制函数,动态设置#WP引脚的状态。

HAL_GPIO_WritePin(GPIOx, GPIO_PIN_x, GPIO_PIN_RESET); // 设置WP引脚为低电平,进入只读模式HAL_GPIO_WritePin(GPIOx, GPIO_PIN_x, GPIO_PIN_SET); // 设置WP引脚为高电平,进入可写模式

3. 数据完整性校验

除了硬件保护,还可以通过软件实现数据完整性校验。例如,使用CRC校验或ECC纠错技术,确保数据在写入和读取过程中的完整性。这些技术可以有效检测和纠正数据传输中的错误,进一步提高数据的可靠性。

掉电保护

掉电保护

掉电保护是硬件设计中另一个容易被忽视的环节。许多数据丢失或系统损坏问题都是由系统异常掉电引起的。通过增加掉电保护电路,可以有效规避这些问题。

1. 掉电检测电路

掉电检测电路可以检测电源电压的下降,并向处理器发送中断信号。常见的实现方法是使用电压比较器(如LM393)设计一个简单的掉电检测电路。当电源电压下降到一定值时,电压比较器输出低电平,触发处理器的中断引脚。

图2 掉电检测电路参考具体实现方法:

- 硬件连接:将电压比较器的输出引脚连接到微控制器的一个中断引脚。

- 软件处理:在中断处理函数中,执行数据保存和系统关闭流程。

voidHAL_GPIO_EXTI_Callback(uint16_t GPIO_Pin){ if (GPIO_Pin == GPIO_PIN_x) { // 检测到掉电中断 // 保存关键数据 SaveCriticalData(); // 关闭系统 ShutdownSystem(); }}

2. 后备电源

后备电源可以在主电源中断时提供足够的电力,确保系统能够完成必要的善后工作。常见的后备电源包括超级电容和备用电池。超级电容具有快速充放电的特性,适合短时间的后备电源需求;备用电池则可以提供更长时间的电力支持。具体实现方法:

- 硬件连接:将超级电容或备用电池连接到系统的电源输入端,并通过一个切换电路确保在主电源中断时自动切换到后备电源。

- 软件处理:在系统检测到掉电中断后,立即启动数据保存和系统关闭流程,确保在后备电源耗尽之前完成所有关键操作。

3. 中断处理

系统接收到中断信号后,立即启动数据保存和系统关闭流程。这包括保存关键数据、关闭外设、关闭文件系统等操作,确保数据的完整性和系统的稳定性。具体实现方法:

- 数据保存:将关键数据写入非易失性存储器(如EEPROM或Flash)。

- 关闭外设:关闭所有外设,确保它们处于安全状态。

- 关闭文件系统:关闭文件系统,确保文件系统的完整性。

voidSaveCriticalData(){ // 将关键数据写入非易失性存储器 WriteDataToFlash(criticalData);}

voidShutdownSystem(){ // 关闭外设 ClosePeripherals(); // 关闭文件系统 CloseFileSystem(); // 关闭系统 HAL_PWR_EnterSLEEPMode(PWR_SLEEPENTRY_WFI);}

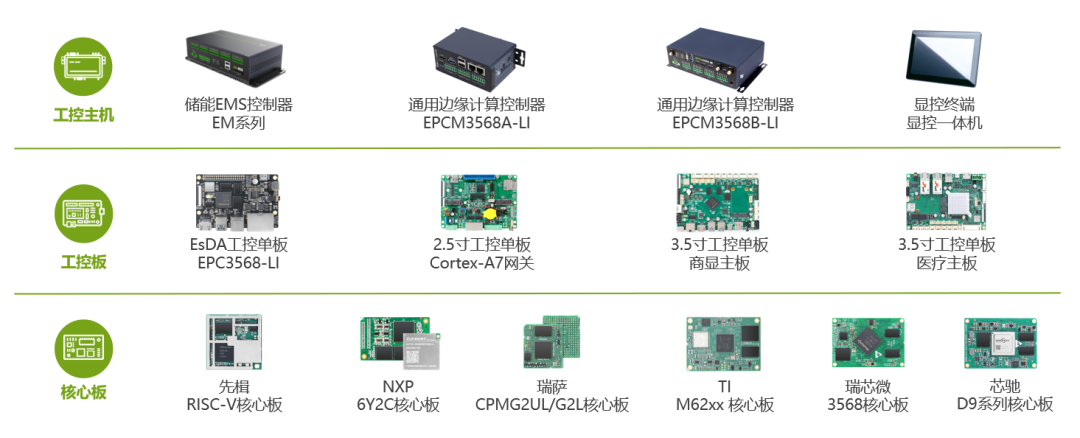

ZLG致远电子边缘技术产品

ZLG致远电子边缘技术产品

ZLG致远电子在设计产品时,充分考虑了数据读写保护和掉电保护的需求。通过精心设计的硬件电路,确保了数据的可靠性和系统的稳定性。我们采用的GPIO控制WP引脚和掉电检测电路,为数据可靠性提供了坚实的硬件基础。

图2 ZLG致远电子边缘技术产品

-

硬件电路的可靠性2015-10-23 5719

-

嵌入式软件可靠性测试方法2016-11-05 2949

-

嵌入式系统产品的可靠性2018-08-30 2362

-

嵌入式软件的可靠性测试与可靠性增长评估2019-06-17 2649

-

开发高可靠性嵌入式系统的技巧有哪些?2019-09-29 1765

-

如何对嵌入式软件进行可靠性测试2021-10-27 1638

-

嵌入式软件的安全可靠性控制2009-04-22 621

-

嵌入式系统软件可靠性设计2010-11-17 783

-

嵌入式系统的可靠性设计2017-11-30 1737

-

军用嵌入式系统的可靠性考虑因素2017-12-02 949

-

嵌入式系统硬件可靠性分析2018-01-17 1122

-

高可靠性嵌入式主板设计2025-03-25 1285

-

【技术指南】提升嵌入式数据可靠性,从元器件选型开始!2025-07-29 675

-

【干货速递】嵌入式数据可靠性,软件设计的这些细节不能忽视!2025-07-31 737

-

知识分享-嵌入式系统可靠性模型2026-03-11 487

全部0条评论

快来发表一下你的评论吧 !