使用肖特基二极管保护射频采样ADC输入

移动通信

描述

任何高性能ADC,尤其是射频采样ADC,输入或前端的设计对于实现所需的系统级性能而言很关键。很多情况下,射频采样ADC可以对几百MHz的信号带宽进行数字量化。前端可以是有源(使用放大器)也可以是无源(使用变压器或巴伦),具体取决于系统要求。无论哪种情况,都必须谨慎选择元器件,以便实现在目标频段的最优ADC性能。

简介

射频采样ADC采用深亚微米CMOS工艺技术制造,并且半导体器件的物理特性表明较小的晶体管尺寸支持的最大电压也较低。因此,在数据手册中规定的出于可靠性原因而不应超出的绝对最大电压,将当前主流的射频采样ADC与之前的老器件相比,可以发现这个电压值是变小的。

在使用ADC对输入信号进行数字量化的接收机应用中,系统设计人员必须密切关注绝对最大输入电压。该参数直接影响ADC的使用寿命和可靠性。不可靠的ADC可能导致整个无线电系统无法使用,且更换成本也许非常巨大。

为了抵消过压带来的风险,射频采样ADC集成了可以检测高电平阈值的电路,允许接收机通过自动增益控制(AGC)环路调节增益来进行补偿。但是,如果采用流水线型ADC,则与架构相关的固有延迟可能导致输入暴露于高电平之下,从而可能损害ADC输入。本文讨论了一种简单的方法来增强AGC环路,保护ADC。

输入架构

射频采样ADC可采用多种不同的设计,最常见的一种是流水线架构,该架构采用多级级联,将模拟信号转换为数字信号。第一级最重要,可以是缓冲或未缓冲级。选择哪种设计取决于设计要求和性能目标。例如,一个带缓冲器的ADC通常在频率范围内具有更好的SFDR性能,但功耗比不带缓冲器的ADC更高。

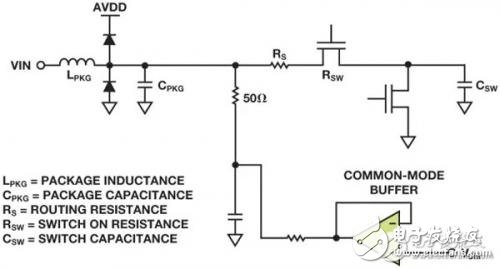

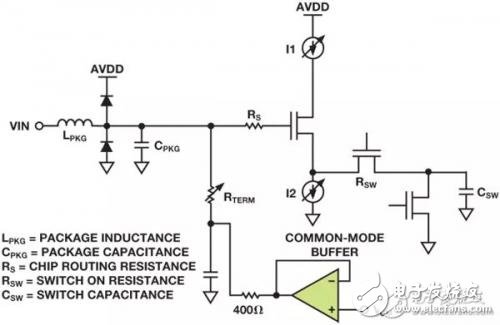

前端设计同样会根据ADC是否有缓冲级而改变。没有缓冲器的ADC需要使用额外的串联电阻来处理输入电荷反冲,它同样会改善SFDR性能。图1和图2显示了AD9625未缓冲和AD9680缓冲射频采样ADC的等效输入电路简化图。为简明起见,仅显示单端输入。

图1. 未缓冲射频采样ADC输入的等效电路

图2. 缓冲射频采样ADC输入的等效电路

无论采用何种架构,ADC输入端可持续的绝对最大电压由MOSFET能够处理的电压决定。缓冲输入更复杂,且比未缓冲输入功耗更大。ADC具有多种不同类型的缓冲器,最常见的一种是源极跟随器。

故障机制

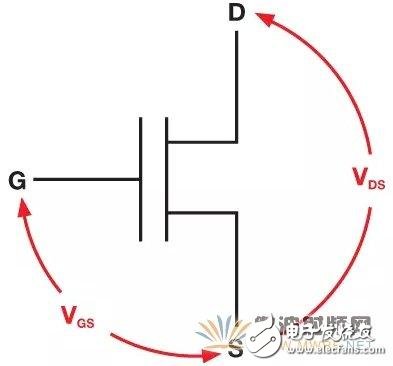

缓冲和未缓冲ADC的故障机制有所不同,但通常是在超出允许的最大栅极-源极电压( (VGS))或漏极-源极电压((VDS))时发生故障。这些电压如图3所示。

图3. MOS晶体管的关键电压

例如,假设VDS超过允许的最大电压,则发生VDS击穿故障,这通常在MOSFET处于关断状态且在漏极施加了相对于源极的过量电压时发生。如果VGS超过允许的最大电压,则它会导致VGS击穿(亦称为氧化层击穿)。这通常在MOSFET处于导通状态且在栅极施加了相对于源极的过量电压时发生。

未缓冲ADC的故障机制

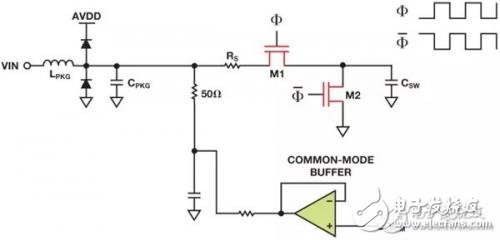

图4显示的是一个未缓冲ADC输入。采样过程由反相时钟信号Φ和Φ控制,它们是MOSFET M1的采样/保持信号以及MOSFET M2的复位信号。M1导通时,M2关断,且电容CSW跟踪信号(采样或跟踪模式)。当M1关断时,MDAC中的比较器作出判断后M2导通,电容CSW复位。这样可在采样阶段使采样电容为下一次采样做好准备。该电路通常工作状态优良。

但是,高压输入使M2暴露在超出其漏源电压的应力之下。当对输入高压进行采样(M1导通、M2关断)时,M2会暴露于较大的VDS之下,其在不足采样时钟半周期的时间内处于关断状态,但哪怕只是瞬时的暴露也会降低电路的可靠性,导致ADC随时间失效。在复位模式下(M1关断、M2导通),因M1的漏极上有输入信号,从而也会暴露于大的VDS电压。

图4. 未缓冲ADC输入的故障模式

缓冲ADC的故障机制

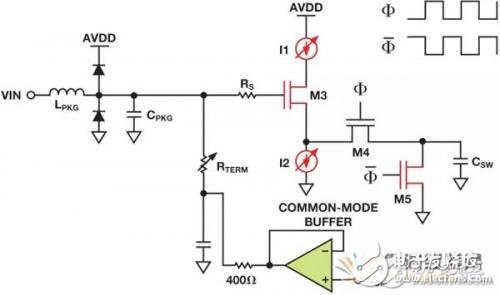

图5显示的是一个缓冲ADC输入。采样和复位信号适用相同的时钟方案。无论相位如何,当缓冲器M3栅极暴露于高压输入时,产生电流I1以及I2。电流源I1采用PMOS晶体管实现,而I2采用NMOS晶体管实现。M3栅极上的高电压导致I1和I2 MOSFET产生过大的VDS。此外,M3栅极上的高电压还可导致氧化层击穿。

图5. 缓冲ADC输入的故障模式

缓冲和未缓冲ADC的击穿机制有所不同,因此绝对最大输入电压同样有所不同,如表1所以。

-

使用肖特基二极管保护射频采样ADC的输入2018-09-21 2504

-

射频采样ADC输入保护:这不是魔法2018-11-01 3320

-

肖特基二极管保护电路小窍门2018-11-30 4124

-

如何使用肖特基二极管保护射频采样ADC输入?2021-04-06 2353

-

二极管保护电路图2009-07-17 2660

-

肖特基二极管,什么是肖特基二极管,肖特基二极管原理2010-02-26 4420

-

肖特基二极管作用2017-10-23 4450

-

关于射频采样ADC输入保护的分析介绍2019-08-23 6368

-

普通硅二极管和肖特基二极管区别_肖特基二极管和快恢复二极管区别2019-08-09 9481

-

二极管保护电路2023-08-27 5487

-

肖特基二极管的功能 肖特基二极管的作用2023-08-28 15462

-

肖特基二极管坏了的表现 肖特基二极管怎么测量好坏2023-09-02 7928

-

肖特基二极管概论2021-06-18 2367

-

肖特基二极管2021-06-26 2576

-

肖特基二极管保护电路的设计原理2024-08-27 3913

全部0条评论

快来发表一下你的评论吧 !